【Xilinx-VDMA模块学习】-01- VDMA IP的GUI配置介绍

使用的是Vivado 2015.4,XC7Z020, AXI Video Direct Memory Acess(6.2)。

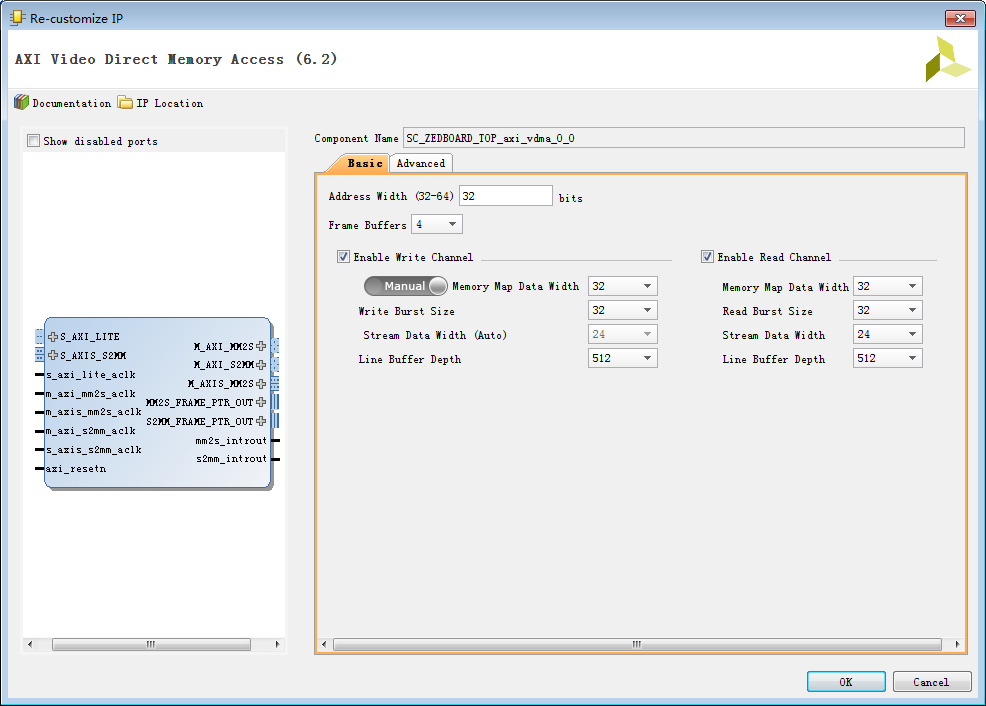

在我的系统中,GUI配置图片如下:(其实和默认配置没有太大区别)

下面介绍VDMA IP内各个参数的配置说明。

1.Basic标签页

Address Width:数据线位宽

除非内存地址空间大约32位,一般就配置成32位了,因为所做的板子DDR只有512MB

Frame Buffers:帧缓冲数

用来缓冲输入图像的帧缓存数量,最大可以选择32帧,在这里选择4就可以了。

据我所了解这个值一般最小设置为3,因为VDMA有一个读通道,一个写通道,在实际使用时一般都是写完了一帧数据,然后再去读这一帧的数据(VDMA内有一种机制,保证读出的帧总是上一次写完的帧)。这样能够防止读取到的图像被撕裂或者别的情况发生。

正常情况下的读写速率一般相同或有可能是写入速度略高于读取速率,在图像写入和读出稳定后,为了保证写入的帧不重叠到读取帧上,Frame Buffers设置为3即可解决。

设置为3时,同一时刻的读写帧组合如下:

FRAME0/FRAME2

FRAME1/FRAME0

FRAME2/FRAME1

读写通道:

Memory Map Data Width: 根据图像的像素数据位宽设置即可,我这里用的RGB三色 共24位数据,选32就可以了

Write/Read Burst Size: 存储空间AXI读写的突发读写数量大小

Stream Data Width:数据流AXIS位宽,RGB 24位,

Line Buffer Depth:数据流AXIS的缓存深度,用来缓存图像数据每一行数据的buffer深度。在xapp1205文档中第6页提到read and write side line buffers inside the AXI Video DMA core are

set to accommodate about one fourth of a line.我这里图像是640*480,这里设置的512,总之在读写速率相同的情况下这个值可以设置的稍微小一些,但最小也要超过行长度的1/4为好。

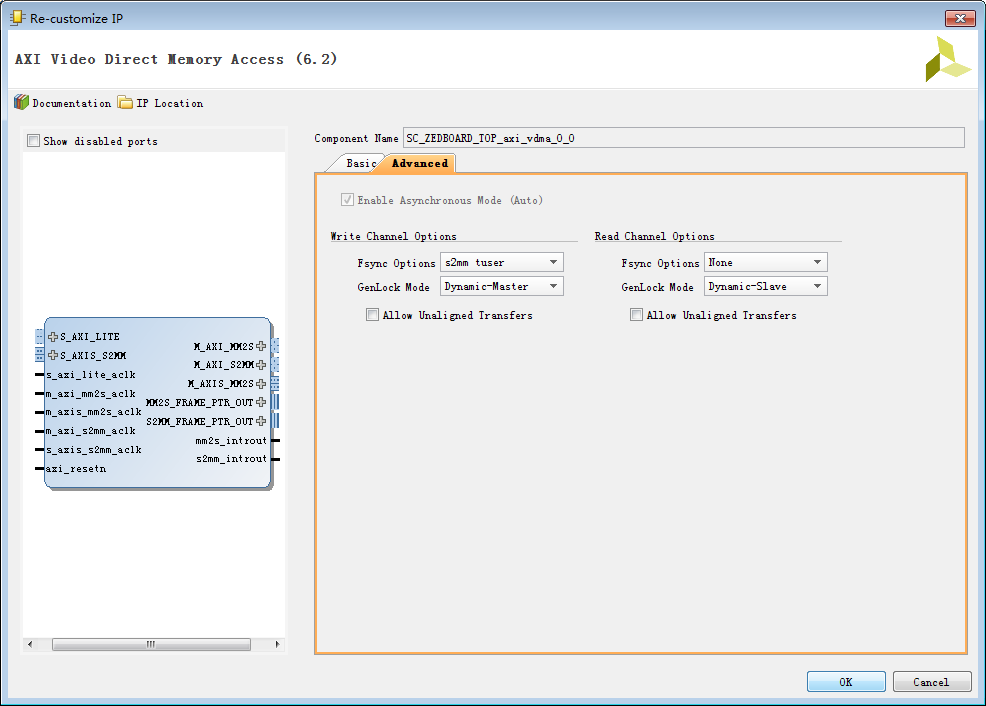

2.Advanced标签页,

因为VDMA里面的同步机制有些复杂,pg020文档里也说建议专业的选手再来配置这些东西,所以所有配置都按默认配置。当然我也想专业一点,尝试了许多次,但是感觉还是这个默认配置是最方便可靠的。

Write/Read Channel Options:

Fsyn Options(Write): 选择了s2mm_tuser,这样每一帧写图像的同步操作是根据前一级IP的AXIS输出总线内的tuser来触发的。这是很好的方法,帧同步起来方便快捷,不会出太大问题。

还可以配置成s2mm_fsync,选择这个后IP的GUI会多出一根信号输入线,这样就可以用诸如VTC的模块来进行全局的帧同步功能。选择这个功能后,VDMA写通道将会忽略AXIS总线中的tuser帧同步信号。

总之,我暂时还是用了第一种默认配置,第二种配置尝试过,但同步起来稍微要考虑的多了一些。也正是因为如此,Frame Buffers我选择了4,防止读写不同步时可能带来的问题。

Fsync Options(Read): 选择了None,Free Running,我的理解就是不需要单独外部同步触发信号,VDMA是通过M_AXIS_MM2S中tuser和反馈回来的tready信号握手成功后来开始触发一帧的读写的。

GenLock Mode: 写通道设置为Dynamic-Master,读通道设置为Dynamic-Slave

为了保证视频图像的读写实时性,需要内部有着一定的机制,这个机制就是通过GenLock模块来完成的。

Dynamic的前缀意思是读写GenLock会互相锁定,而另外两种没有前缀的Master和Slave则需要一些额外的软件开销,或者不太符合我的功能要求,我就没有仔细研究了。

我所理解的动态互相锁定:首先读写通道会有一个各自正在操作的帧编号告诉对方,默认写是0,读是2(3 Frame Buffers),由于读写速率不同或者是内存存取上出现延迟等等问题,有可能会导致,读写的帧编号错位(我猜的)。当主(即写通道)写操作完成后,会看一下从通道正在操作的帧编号,假如从的帧编号和主准备下次操作帧编号相同,主会选择跳过这个帧,并去下一帧进行写操作。从(读通道)读操作完成后,会读取主通道上一次操作的帧编号,并直接进行下次的读操作。

机制就是这样了,保证了读写操作不会同时发生在一个帧,导致数据的错误。但是我在想,对于摄像头的读取和显示是否可以不用这样设置,而是直接让读写发生在同一帧上,读取速率相同的前提下,让读取操作比写操作晚上几行,这样系统将会有着更低的延时,但这样也会需要更加精确的数据流控制。

Allow unaligned Transfers:默认不选择,这种高级功能就先不研究了,不选

这样,我的VDMA就配置完成了,读写通道的速率都是1080P要求的148.5M。通过另外的Video Test Pattern Generator、AXI_Interconnect、Video On Screen Display、Video Timing Controller、AXI4-Stream to Video Out来共同实现了VDMA图像读写和1080P视频显示的逻辑架构。

下一次,写一下VDMA和上面提到的这些模块如何工作,让视频图像显示起来。

【Xilinx-VDMA模块学习】-01- VDMA IP的GUI配置介绍的更多相关文章

- nodejs的mysql模块学习(十)连接池集群配置选项

连接池集群选项 canRetry : 如果true ,连接池集群会在连接失败时尝试连接 默认true removeNodeErrorCount : 如果连接失败,节点的errCount增加.当erro ...

- SoC中的IP模块学习

SoC中的IP模块学习 理解IP Spec-->register定义,理解原理+架构框图 查看testcase+model(看已有的测试例程),分析操作/使用模块的流程,寄存器的配置方法 运行仿 ...

- Xilinx 常用模块汇总(verilog)【03】

作者:桂. 时间:2018-05-10 2018-05-10 21:03:44 链接:http://www.cnblogs.com/xingshansi/p/9021919.html 前言 主要记 ...

- 【Xilinx-VDMA模块学习】-00-开始

最近在做XILINX图像相关的逻辑,需要用到VDMA模块,最后算是把这个模块摸得比较透了. 先在这里记一下,之后有空了总结一下.包括VDMA在Vivado中的GUI配置和软件驱动的详细理解.

- Python学习--01入门

Python学习--01入门 Python是一种解释型.面向对象.动态数据类型的高级程序设计语言.和PHP一样,它是后端开发语言. 如果有C语言.PHP语言.JAVA语言等其中一种语言的基础,学习Py ...

- Day5 - Python基础5 常用模块学习

Python 之路 Day5 - 常用模块学习 本节大纲: 模块介绍 time &datetime模块 random os sys shutil json & picle shel ...

- ThinkPhp学习01

原文:ThinkPhp学习01 一.ThinkPHP的介绍 MVC M - Model 模型 工作:负责数据的操作 V - View 视图(模板 ...

- Node.js学习之TCP/IP数据通讯

Node.js学习之TCP/IP数据通讯 1.使用net模块实现基于TCP的数据通讯 提供了一个net模块,专用于实现TCP服务器与TCP客户端之间的通信 1.1创建TCP服务器 在Node.js利用 ...

- python中confIgparser模块学习

python中configparser模块学习 ConfigParser模块在python中用来读取配置文件,配置文件的格式跟windows下的ini配置文件相似,可以包含一个或多个节(section ...

随机推荐

- 宿主机丢失vmnet0和vmnet8网卡

好久没打开虚拟机竟然发现与主机的连接网卡都不见了,有人说进入编辑-->虚拟网络编辑-->将主机虚拟适配器连接到此网络打钩就好,我觉得蛮有道理的,但是试验打勾并点击应用时虚拟机又会返回到没打 ...

- linux下的文本处理命令sed&awk&grep

Sedsed 是个精简的.非交互式的编辑器.他能执行和编辑vi和emacs相同的编辑任务.sed编辑器不提供交互使用方式:只能在命令行输入编辑命令.指定文件名,然后在屏幕上察看输出.sed编辑器没有破 ...

- HDOJ 1319 Prime Cuts<数论>

学会了不难.通过这道题学习了两点: 1:筛选法求素数. 2:在写比较长的程序的时候,给每个功能部分加上注释,思路会更清晰. 题意: 1.题目中所说的素数并不是真正的素数,包括1: 2.需要读懂题意,对 ...

- zencart侧边导航点击一级目录展开二级目录

[小 大] 2013-09-17 00:20 来源: 未知 作者:wtozz_admin 我要投稿 zencart侧边导航点击一级目录展开二级目录 zen cart Categories默认的是只显示 ...

- 改变MyEclipse创建JSP时默认的pageEncoding编码

如何改变MyEclipse创建JSP时默认的pageEncoding编码 有时我们需要改变MyEclipse创建JSP时默认的pageEncoding编码,因为也许它默认的编码不是我们想要的,比如我们 ...

- Pop框架简述

Facebook发布了Paper之后,进一步开源了其背后的动画引擎Pop,此框架并不满足于苹果自身的动画单调性,致力于给用户一种逼真的动画效果,可以减少用户对于苹果原生Core Animation 复 ...

- php实现分页

php函数 <?php////////////////////$result :容器的id//$url:请求的url//$total:总条数//$num:页容量//$pagenum:总页数//$ ...

- Express 简介

Express 简介 Express 是一个简洁而灵活的 node.js Web应用框架, 提供了一系列强大特性帮助你创建各种 Web 应用,和丰富的 HTTP 工具. 使用 Express 可以快速 ...

- Linux 分区和目录

[1. 分区与目录概念理解] Linux的分区是物理上的概念,就像我们把一块硬盘分成C:,D:,E:三个区一样,物理上将存储空间分开 Linux的目录是逻辑上的概念,Linux的目录树实际上是一个分 ...

- mysql trouble shooting---- 从库停止同步lock_wait_timeout_exceeded_try_restarting_transaction

问题描述: 数据库从库停止同步. 问题分析: show slave status\G;(也可使用show full processlist) 显示 某个update语句出错,Lock wait tim ...