AXI总线介绍

原帖地址:https://wenku.baidu.com/view/7c424c17e3bd960590c69ec3d5bbfd0a7956d5b9.html

1、AXI简介

AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据阶段是分离的;支持地址不对齐的数据传输;同时在基于突发(burst_basded transcation)的传输中,只需要首地址;同时分离的读写数据通道,总共有5个独立的通道;并支持显著传输(outstanding transcation)访问和乱序访问; 非常容易添加流水线级数以获得高频的时序。AXI 是AMBA 中一个新的高性能协议。AXI 技术丰富了现有的AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

突发传输一般表示的是两个设备之间进行数据传送的一种模式,也可将其称为突发模式下的数据传输。而突发(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输的周期数就是突发长度(Burst Lengths,简称BL)。在突发传输模式下,多个数据单元当做一个单元(相当一个数据块)来传送,从而提高了传输效率。突发方式将整个信道专用于传送一个源节点的数据。具有突发方式功能的设备常常为成组方式操作提供最大吞吐率。

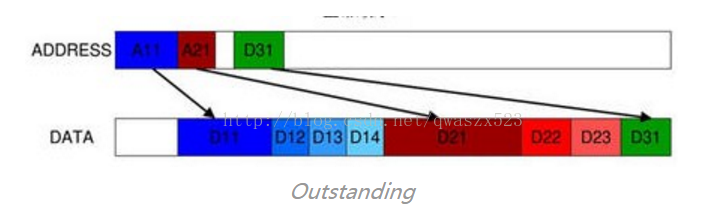

Outstanding: The ability to issue multiple outstanding addresses means that masters can issue transaction addresses without waiting for earlier transactions to complete. This featurecan improve system performance because it enables parallel processing of transactions.

发出A11的addr后,在完成D11~D14的transfer之前,发出A21叫做outstanding。

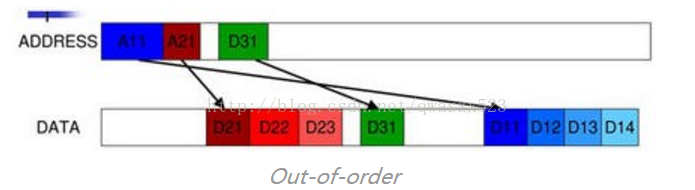

Out-of-order : The ability to complete transactions out of order means that transactions to faster memory regions can complete without waiting for earlier transactions to slower memory regions. This feature can also improve system performance because it reducesthe effect of transaction latency.

地址的顺序是A11,A21,A31,而返回数据顺序则可能是D2,D3,D1,这个过程叫做Out-of-order

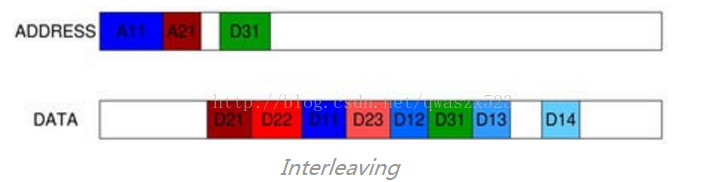

Interleaving: Write data interleaving enables a slave interface to accept interleaved write data with different AWID values. The slave declares a write data interleaving depth that indicates if the interface can accept interleaved write data from sources with different AWID values.

D11和D12之间插入D23,叫做interleaving。

简单而言,outsatanding是对地址而言,一次burst还没结束,就可以发送下一相地址。而out-of-order和interleaving则是相对于 transaction,out-of-order说的是发送transaction和接收的cmd之间的顺序没有关系,如先接到A的cmd,再接到B的cmd,则可以先发B的data,再发A的data;interleaving指的是A的data和B的data可以交错,如A1 B1 A2 B2 B3……

2. AXI 特点

单向通道体系结构。信息流只以单方向传输,简化时钟域间的桥接,减少门数量。当信号经过复杂的片上系统时,减少延时。

支持多项数据交换。通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。

独立的地址和数据通道。地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。

3.AXI协议和AXI协议定义的基础事务

- AXI总线共有5个通道分别是read address channel,write address channel,read data channel, write data channel,write response channel。每一个AXI传输通道都是单方向的。

- 每一个transaction都有地址和控制信息在地址通道(address channel)中,用来描述被传输数据的性质。

- 读transcation的结构图如下:读请求和数据返回

- 写transcation的结构如下:

- 5、 这5条独立的通道都包含一个信息信号和一个双路的VALID、READY握手机制。

- 6、 信息源通过VALID信号来指示通道中的数据和控制信息什么时候有效。目地源用READY信号来表示何时能够接收数据。读数据和写数据通道都包括一个LAST信号,用来指明一个事物传输的最后一个数据。

- 7、 读和写事务都有他们自己的地址通道,这地址通道携带着传输事务所必须的地址和信息。

- dd

AXI总线介绍的更多相关文章

- AXI总线

AXI(Advanced eXtensible Interface)是一种总协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture) ...

- zynq里面的AXI总线(2017-1-11)

在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议.其中三种AXI总线分别为: AXI4:(For high-performance memory-mapped requir ...

- AXI总线(转)

AXI(Advanced eXtensible Interface)是一种总协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture) ...

- AXI总线协议

AXI总线协议 (一).概述 AXI (高性能扩展总线接口,Advanced eXtensible Interface)是ARM AMBA 单片机总线系列中的一个协议,是计划用于高性能.高主频的系统设 ...

- zedboard如何从PL端控制DDR读写(二)——AXI总线

虽然Xilinx已经将和AXI时序有关的细节都封装起来,给出了官方IP和向导生成自定义IP,用户只需要关注自己的逻辑实现,但是还是有必要简单了解一下AXI的时序,毕竟咱是做硬件设计的. AXI(Ad ...

- FPGA中的除法运算及初识AXI总线

FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会.硬件逻辑实现的除法运算会占用较多的资源,电路结构复杂,且通常无法在一个时钟周期内完成.因此FPGA实现除法运算并不是一个&qu ...

- 自定义AXI总线形式SPI接口IP核,点亮OLED

一.前言 最近花费很多精力在算法仿真和实现上,外设接口的调试略有生疏.本文以FPGA控制OLED中的SPI接口为例,重新夯实下基础.重点内容为SPI时序的RTL设计以及AXI-Lite总线分析.当然做 ...

- 利用ZYNQ SOC快速打开算法验证通路(6)——利用AXI总线实时配置sysGen子系统

利用ZYNQ验证算法的一大优势在于,可以在上位机发送指令借助CPU的控制能力和C语言易开发特点,实时配置算法模块的工作模式.参数等对来对其算法模块性能进行全面的评估.最重要的是无需重新综合硬件模块. ...

- 将自己写的HDL代码封装成带AXI总线的IP

将自己写的HDL代码封装成带AXI总线的IP 1.Tools->create and package IP 2.create AXI4总线的IP 3.新建block design 4.点击右键, ...

随机推荐

- Codeforces 822E Liar dp + SA (看题解)

Liar 刚开始感觉只要开个dp[ i ][ j ][ 0 / 1 ]表示处理了s的前 i 个用了 k 段, i 是否是最后一段的最后一个字符 的 t串最长匹配长度, 然后wa24, 就gg了.感觉这 ...

- Codeforces 633F The Chocolate Spree 树形dp

The Chocolate Spree 对拍拍了半天才知道哪里写错了.. dp[ i ][ j ][ k ]表示在 i 这棵子树中有 j 条链, 是否有链延伸上来. #include<bits/ ...

- Codeforces 387E George and Cards

George and Cards 我们找到每个要被删的数字左边和右边第一个比它小的没被删的数字的位置.然后从小到大枚举要被删的数, 求答案. #include<bits/stdc++.h> ...

- BZOJ3110 [Zjoi2013]K大数查询 树套树 线段树 整体二分 树状数组

欢迎访问~原文出处——博客园-zhouzhendong 去博客园看该题解 题目传送门 - BZOJ3110 题意概括 有N个位置,M个操作.操作有两种,每次操作如果是1 a b c的形式表示在第a个位 ...

- day9文件操作---从即日起时景丽阳老师给我们讲课

今天的主要内容是文件的操作,读,写,只读只写,或者可读同时可写,追加写,以二进制的方式读,以二进制的方式写,以二进制的方式追加. 思维导图: 给你一个文件路径,从中找出所有的文件,方法如下: # 方法 ...

- PyQt PySide QListWidget 添加自定义 widget

PyQt PySide QListWidget 添加自定义 widget 原文链接:https://stackoverflow.com/questions/25187444/pyqt-qlistwid ...

- java实现点选汉字验证码(转)

package com.rd.p2p.web; import java.awt.BasicStroke; import java.awt.Color; import java.awt.Font; im ...

- 自定义PDO封装类

<?php class Db { protected static $_instance = null; // 定义标识符(通过$_instance值得改变情况,来判定Model类是否被实例化) ...

- group by 和where 条件后面不能用刚设置的别名。

select count(*),c_xy_bj a from z_user group by c_xy_bj 这个group by后面不能使用c_xy_bj 字段的别名a,只有外面再嵌套sel ...

- 00-JAVA语法基础--动手动脑

1.运行EnumTest.java,并分析结果,得出结论. 其源代码以及运行结果截图如下: 枚举类型的常量以字符串的形式顺序储.源代码中s和t不是原始数据类型.getCLass():取得当前对象所属的 ...