verilog语法实例学习(7)

常用的时序电路介绍

组合电路:这类电路的输出信号值仅却决于输入端信号值。

时序电路:时序电路的输出值不仅取决于当前的输入值,还取决于电路的历史状态,所以时序逻辑电路中包含保存逻辑信号值的存储元件,存储元件中的值代表了当前电路的状态。当电路的的输入信号值发生改变时,新输入的信号值可能使电路保持同样的状态,也可能使电路进入另一种状态,随着时间推移,输入信号值的变化导致电路状态发生一系列的改变,这种电路称为时序电路。

同步时序电路:大部分情况下,由一个时钟信号控制的时序电路称为同步时序电路。在同步时序电路中,状态变量是同一时钟控制的触发器表征,这个时钟是由脉冲组成的周期信号,状态变化可发生在时钟脉冲的上升沿或者下降沿。

异步时序电路:没有时钟控制信号的时序电路称为异步时序电路。

组合逻辑电路既能用连续赋值语句描述,也能用过程赋值语句描述,但时序电路只能用过程赋值语句描述。下面是一些时序电路的典型例子。

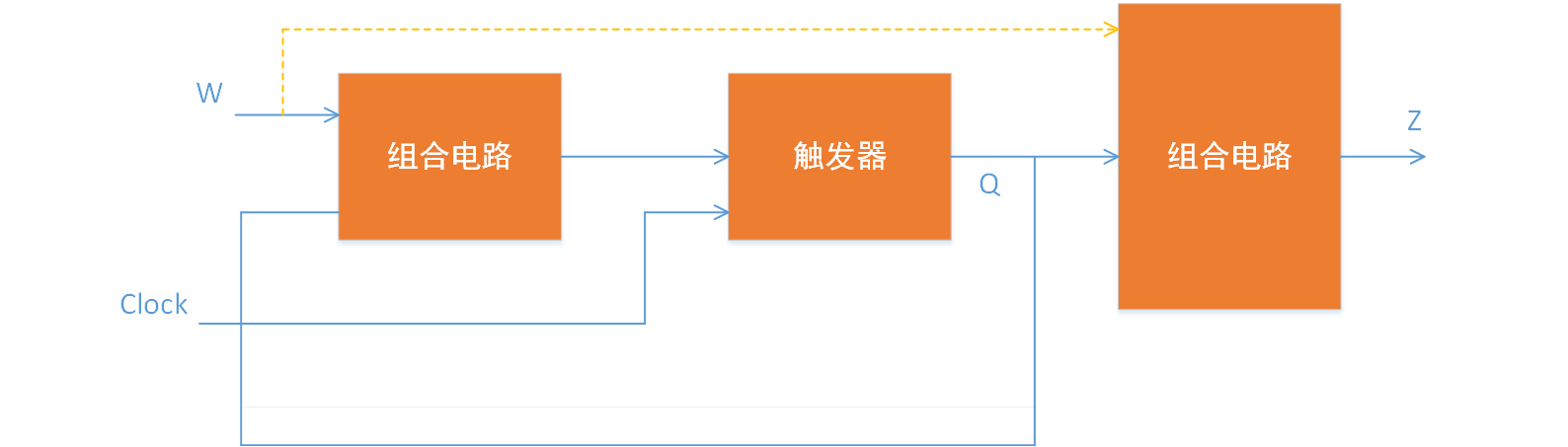

同步时序电路的一般形式

时序电路由组合逻辑以及一个或多个触发器实现。一般的架构如下图所示:W为输入,Z为输出,触发器中存储的状态为Q。在时钟信号的控制下,触发器通过加在其输入端的组合逻辑输入,使得电路从一个状态变成另一个状态。

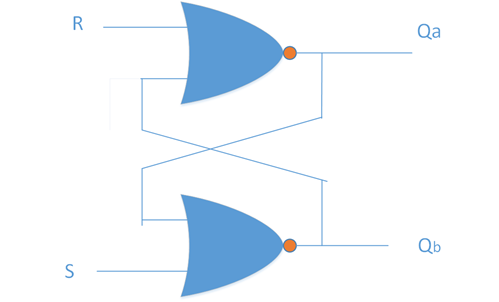

基本锁存器

基本锁存器通常如下图所示,由两个或非门用交叉耦合的方式相连。它的输入包括复位端R(reset)和置位端S(set),输出为Qa和Qb,Qa和Qb在这儿互为反相。

假设Qa=1,Qb=0,当R=0,S=0时,可知Qa=1,Qb=0保持不变。 //锁存器保持原态

假设Qa=0,Qb=1,当R=0,S=0时,可知Qa=0,Qb=1保持不变。 //锁存器保持原态

当R=1,S=0时,Qa=0,Qb=1 //锁存器复位

当R=0,S=1时,Qa=1,Qb=0 //锁存器置位

当R=1,S=1时,Qa=0,Qb=0

所以基本锁存器的特性表(不是真值表,输出不仅仅和输入相关)为:

| S | R | Qa | Qb | 备注 |

| 0 | 0 | 0/1 | 1/0 | 保持不变 |

| 0 | 1 | 0 | 1 | |

| 1 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 0 |

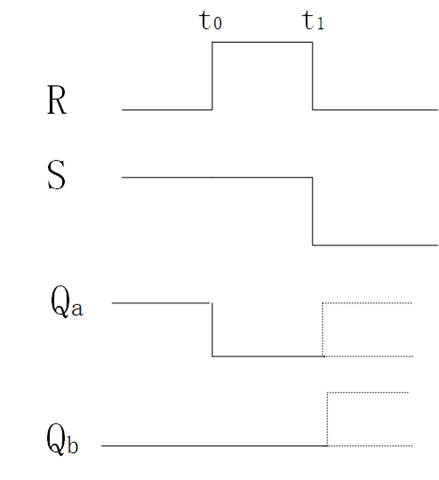

我们来看基本锁存器震荡的情况:在t0时刻,R=1,S=1,所以Qa,Qb都为0,在t1时刻,R=0,S=0,Qa和Qb立即变为1,随后又变为0,反复震荡,如果两个或非门的延迟严格相等,则这种震荡会反复持续下去,但实际情况下,延迟总有差别,所以最终会停留在两个状态中的某一个,但不能确定时哪一个,这种不确定性在波形中用虚线标出。通常来说,只要电路中包含一条或多条反馈电路,其状态便于逻辑门的传输延迟有关,设计这类电路必须十分小心。

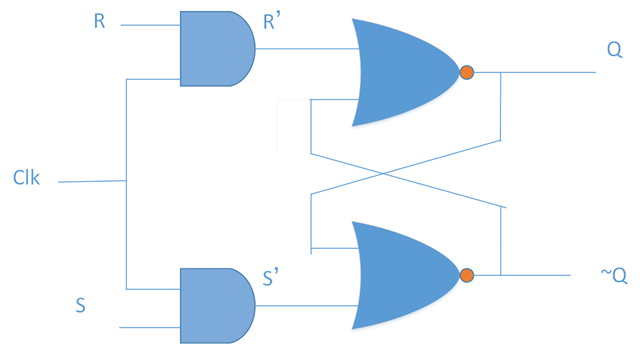

门控SR锁存器

对基本锁存器进行一点改动,加入时钟信号(Clk)作为控制信号,形成如下图所示的锁存器称为门控SR锁存器。

当Clk为1时,该电路功能和基本锁存器一样,在Clk为0时,无论S,R信号为何值,输出状态保持不变。

若S=R=1,时钟信号Clk从1变为0时候,将会引起震荡,所以我们要尽量避免S,R都为1的状态。

因为S,R不能同时为1,所以输出端我们用Q和~Q表示

| Clk | S | R | Q(t+1) | 备注 |

| 0 | x | x | Q(t) | 保持不变 |

| 1 | 0 | 0 | Q(t) | 保持不变 |

| 1 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | x | 要避免SR同时为1 |

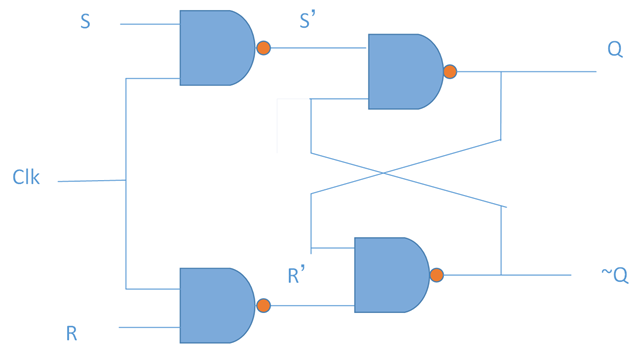

下面是与非门实现的门控SR锁存器,与或门实现的门控SR锁存器相比,Clk信号是由与非门选通的,而且,S和R正好位置相反。

但它们的特性表是一样的。

| Clk | S | R | S‘ | R’ | Q(t+1) | 备注 |

| 0 | x | x | 1 | 1 | Q(t) | 保持不变 |

| 1 | 0 | 0 | 1 | 1 | Q(t) | 保持不变 |

| 1 | 0 | 1 | 1 | 0 | 0 | |

| 1 | 1 | 0 | 0 | 1 | 1 | |

| 1 | 1 | 1 | 0 | 0 | x | 要避免SR同时为1 |

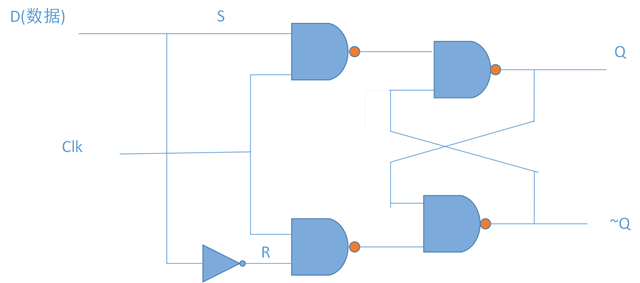

门控D锁存器

实际应用中更常用的是门控D锁存器,它在SR锁存器的基础上进行了小小的改动。和SR锁存器不同,D锁存器只有一个输入端D,如下图所示:

D为1,则Q置位为1,D为0,则Q复位为0。相比SR锁存器,D锁存器不会出现S,R都为1的麻烦状态。

D锁存器的输出受到时钟电平高低的控制,所以这种锁存器又被称作电平敏感型信号锁存器。与之对应的是在时钟边沿触发的存储元件,通常称作触发器。

| Clk | D | Q(t+1) |

| 0 | x | Q(t) |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

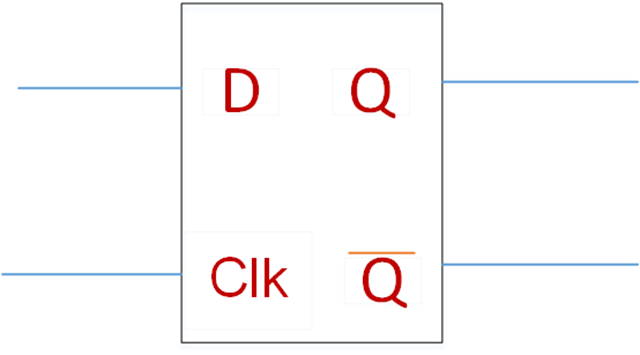

D锁存器的图形符号为:

门控D锁存器的代码如下:

在时钟为高电平时,Q=D,否则Q保持原来的值,所以锁存器可以当作存储元件考虑。

verilog中D锁存器的代码如下:

/*门限D锁存器*/

module dqlatch(D, clk, Q);

input D;

input clk;

output reg Q; always @(D,clk)

if(clk)

Q = D; //没有else,在clk低电平,Q锁存之前的值。 endmodule

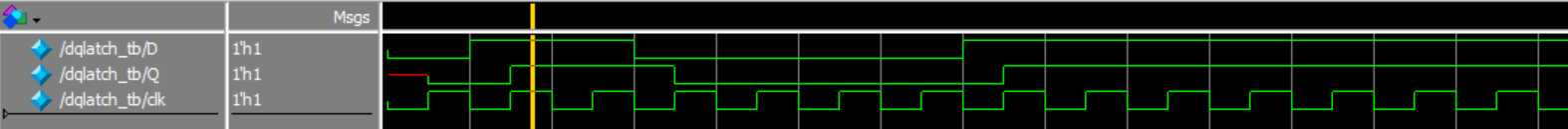

使用下面的testbench代码,可以验证D锁存器。

`timescale 1ns/1ns

`define clock_period 20 module dqlatch_tb;

reg D;

wire Q;

reg clk; dqlatch dqlatch0(.D(D),.clk(clk),.Q(Q));

always # (`clock_period/2) clk = ~clk; initial

begin

D = 1'b0;

clk = 1'b0;

#(`clock_period)

D = 1'b1;

#(`clock_period*2)

D = 1'b0;

#(`clock_period*4)

D = 1'b1;

#(`clock_period*10)

$stop;

end endmodule

从波形中,可以看出在时钟信号clk高电平时候,Q=D,否则Q保持之前的值。

在下面的连接中,我们讨论了触发器的传输延时的影响。对于锁存器是一样的分析方法,在时钟边沿到来时,也要考虑信号D的建立时间和保持时间。

https://www.cnblogs.com/mikewolf2002/p/10200660.html

verilog语法实例学习(7)的更多相关文章

- verilog语法实例学习(4)

Verilog模块 Verilog中代码描述的电路叫模块,模块具有以下的结构: module module_name[ (portname {, portname})]; //端口列表 [parame ...

- verilog语法实例学习(1)

本文档中通过verilog实例来学习verilog语法.Verilog是一种硬件描述语言,它具有并发性和时序性.并发性是指不同硬件模块的同时操作,时序性是指信号的赋值或操作在时钟的边沿进行.由于作者本 ...

- verilog语法实例学习(12)

verilog中的综合和不可综合总结 Verilog中综合的概念 综合就是EDA工具或者说综合工具把我们编写的verilog代码转化成具体电路的过程.Verilog中有很多语法,结构,过程,语句,有些 ...

- verilog语法实例学习(6)

函数和任务 函数 https://wenku.baidu.com/view/d31d1ba8dd3383c4bb4cd283.html verilog中函数的目的是允许代码写成模块的方式而不是定义独立 ...

- verilog语法实例学习(5)

子电路模块 子电路模块的使用 一个verilog模块能够作为一个子电路包含在另一个模块中.采用这种方式,所有的模块都必须定义在一个文件中,那么verilog编译器就必须被告知每个模块的所属.模块例化的 ...

- verilog语法实例学习(2)

Verilog中的信号类型 线网类型 线网类型表示一个或多个门或者其它类型的信号源驱动的硬件连线.如果没有驱动源,则线网的默认值为z.verilog中定义的线网类型有以下几种: wire,tr ...

- verilog语法实例学习(13)

verilog代码编写指南 变量及信号命名规范 1. 系统级信号的命名. 系统级信号指复位信号,置位信号,时钟信号等需要输送到各个模块的全局信号:系统信号以字符串Sys开头. 2. 低电平有效的 ...

- verilog语法实例学习(11)

同步时序电路的一般形式 时序电路由组合逻辑以及一个或多个触发器实现.一般的架构如下图所示:W为输入,Z为输出,触发器中存储的状态为Q.在时钟信号的控制下,触发器通过加在其输入端的组合逻辑输入,使得电路 ...

- verilog语法实例学习(10)

常用的时序电路介绍 T触发器和JK触发器 在D触发器输入端添加一些简单的逻辑电路,可以生成另一种类型的存储元件.比如下图所示的T触发器.该电路有一个上升沿触发的触发器和两个与门,一个或门,以及一个反相 ...

- verilog语法实例学习(9)

常用的时序电路介绍 寄存器 一个触发器可以存储一位数据,由n个触发器组成的电路可以存储n位数据,我们把这一组触发器叫做寄存器.寄存器中每个触发器共用同一个时钟. 下面是n位寄存器的代码,我们通过一个参 ...

随机推荐

- JavaWeb中Tomcat与Eclipse的集成—步骤详解

前面会简单介绍,下翻Tomcat与Eclipse的集成 一.先介绍一下应用程序的结构: 1.到目前为止应用程序物理结构有两种: C/S——Client / server:这种结构的应用,客户端与服务端 ...

- 数据包注入重放工具aireplay-ng

数据包注入重放工具aireplay-ng aireplay-ng是aircrack-ng组件包的一个工具.它可以注入和重放数据帧,用于后期的WEP.WPA-PSK破解.它提供九种攻击模式,包括死亡 ...

- android studio svn 创建分支

创建分支或标签 从哪里复制 工作副本 用这个变体去创建分支,并带着当地的改变.通常,服务项将被 添加带历史 , 不仅仅只有目标目录. 每个不同于根的版本文件 ,将被指定的复制.它推荐 去更新 工作副本 ...

- CentOS 7下启动postfix服务报错:fatal: parameter inet_interfaces: no local interface found for ::1

sed -i 's/inet_interfaces = localhost/inet_interfaces = all' /etc/postfix/main.cf service postfix re ...

- Ubuntu Java7 SDK环境变量配置(转)

1.去甲骨文官网下载java7 sdk http://www.oracle.com/technetwork/java/javase/downloads/index.html 这里笔者下载了最新的jav ...

- Android ListView理解之BaseAdapter

ListView是Android开发过程中较为常见的组件之一,它将数据以列表的形式展现出来.一般而言,一个ListView由以下三个元素组 成: 1.View,用于展示列表,通常是一个xml所指定的. ...

- Ubuntu 14 安装Java(JRE、JDK)、Maven

JRE vs OpenJDK vs Oracle JDK JRE(Java Runtime Environment),它是你运行一个基于Java语言应用程序的所正常需要的环境.如果你不是一个程序员的话 ...

- cocos 主循环

CCApplication的run为主循环,负责在空闲的时候,调用CCDirector的mainloop,setAnimationInterval设置多少秒一帧.m_nAnimationInterva ...

- Apache Kafka —一个不同的消息系统

Apache已经发布了Kafka 0.8,也是自从成为Apache软件基金会的顶级项目后Kafka的 第一个主版本. Apache Kafka是发布—订阅消息传递,实现了分布式提交日志,适用于离线和在 ...

- 在ASP.NET MVC下实现单个图片上传, 客户端服务端双重限制图片大小和格式, 服务端裁剪图片

在"MVC文件图片ajax上传轻量级解决方案,使用客户端JSAjaxFileUploader插件01-单文件上传"一文中,使用JSAjaxFileUploader这款插件实现了单文 ...