基于FPGA(DDS)的正弦波发生器

记录背景:昨晚快下班时,与同事rk聊起怎么用FPGA实现正弦波的输出。我第一反应是利用高频的PWM波去滤波,但感觉这样的波形精度肯定很差;后来想起之前由看过怎么用FPGA产生正弦波的技术,但怎么都想不起来这个技术的名称是叫什么了。后来搜索后才知道就是DDS(Direct Digital Synthesizer),即:直接数字频率合成器。

最近(好吧,不是最近,是一直)发现自己记东西记不牢,究竟是自己老了,记忆力下退;还是自己不用心去记;还是因为看得少,缺少实践(毕竟纸上得来终觉浅、绝知此事要躬行)。

-----------------------------分割线-----------------------------------

以下内容主要转自:http://blog.chinaaet.com/lincoding/p/5100050592,如有侵权,请告知删除。抱歉!

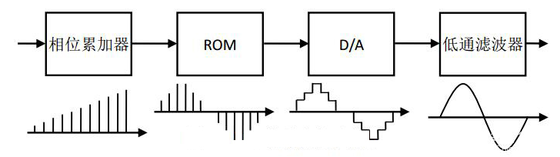

DDS的主要组成部分:相位累加器、相位调制器、波形数据表、DAC和低通滤波器四大部分组成。如下图:

DDS的原理:

1、首先ROM中要存放好要显示的正弦波数据;

2、然后由相位累加器(其实就是个计数器)一直累加,这个累加器的值作为ROM的地址

3、DAC根据ROM输出的数据输出对应的电压值

4、由于上述输出的电压值是个离散值,无法构成平滑的正弦波,因此需要在后级增加一个低通滤波器才能输出完美的正弦波。

那么,怎么实现上述的功能呢?

首先,我们要考虑两个问题:

A、相位累加器(计数器)的位宽是多少?

B、ROM的数据位宽和深度(深度:2^地址位宽)是多少?

对于第一个问题:相位累加器的位宽一般是24~32bits,一般选32bits(因为这样的位宽能满足绝大部分的应用场合了);

对于第二个问题:

ROM的数据位宽选择要看DAC模块,比如我的DAC模块的数据输入数据范围是0~1023,那么ROM的数据位宽就要选择10位;

ROM的深度也要取决于你的DAC模块,因为ROM中只能存储整数。

相位累加器举例:

//-----------------------------------

//phase adder

reg [:] fre_cnt;

always @ ( posedge clk or negedge rst_n )

begin

if ( ! rst_n )

fre_cnt <= 'd0;

else if ( DDS_en )

fre_cnt <= fre_cnt + 'b1;

else

fre_cnt <= 'd0;

end

这就是所谓的相位累加器,在DDS_en是能以后就一直技术,直到记满,然后重新又开始计数。

DDS_rom u_DDS_ddsrom

(

.clock (clk),

.address (fre_cnt),

.q (DAC_data)

);

然后,将计数的值作为ROM的地址送给ROM,ROM输出相应的正弦波数据,这是,会把2048个点(假设ROM中存了一个正弦波周期的数据,共2048个数据)全部输出。而2048个点全部输出需要的实践为:2048*20ns(假设时钟为50MHz)=40960ns(24414.0625Hz),这就是DDS的基本频率,我们将其称为基频。

***********************************************************************************************************

如果我们希望能将频率翻倍,可以这样:

//-----------------------------------

//phase adder

reg [:] fre_cnt;

always @ ( posedge clk or negedge rst_n ) //clk为50Mhz

begin

if ( ! rst_n )

fre_cnt <= 'd0;

else if ( DDS_en )

fre_cnt <= fre_cnt + 'd2;

else

fre_cnt <= 'd0;

end DDS_rom u_DDS_ddsrom

(

.clock (clk),

.address (fre_cnt),

.q (DAC_data)

);

如果我们希望把频率减半,我们可以这样:

//-----------------------------------

//phase adder

reg [:] fre_cnt;

always @ ( posedge clk_ref or negedge rst_n ) //clk_ref为25Mhz

begin

if ( ! rst_n )

fre_cnt <= 'd0;

else if ( DDS_en )

fre_cnt <= fre_cnt + 'b1;

else

fre_cnt <= 'd0;

end DDS_rom u_DDS_ddsrom

(

.clock (clk),

.address (fre_cnt),

.q (DAC_data)

);

注意:上述的clk_ref为25MHz;

但由于上述需要用到另外的时钟,clk_ref,这会让代码不好维护,改良代码如下:

//-----------------------------------

//phase adder

reg [:] fre_cnt;

always @ ( posedge clk or negedge rst_n ) //clk为50Mhz

begin

if ( ! rst_n )

fre_cnt <= 'd0;

else if ( DDS_en )

fre_cnt <= fre_cnt + fre_value;

else

fre_cnt <= 'd0;

end wire [:] rom_addr = fre_cnt[:]; DDS_rom u_DDS_ddsrom

(

.clock (clk),

.address (rom_addr),

.q (DAC_data)

);

为了更进一步完善DDS,我们可以再增加一个相位调节的功能:

//-----------------------------------

//phase adder

reg [:] fre_cnt;

always @ ( posedge clk or negedge rst_n ) //clk为50Mhz

begin

if ( ! rst_n )

fre_cnt <= 'd0;

else if ( DDS_en )

fre_cnt <= fre_cnt + fre_value;

else

fre_cnt <= 'd0;

end wire [:] rom_addr = fre_cnt[:] + pha_value; DDS_rom u_DDS_ddsrom

(

.clock (clk),

.address (rom_addr),

.q (DAC_data)

);

就是增加一个pha_value的相位控制字,它的位宽需与ROM中DAC模块的位宽相同。

Summary:

1、相位累加器的位宽为24~32bites,一般选32bits;

2、频率控制字位宽与相位累加器位宽相同;

3、ROM的数据位宽选择取决于DAC模块;

4、ROM的深度(2^地址位宽)有标准深度,但可任意;

5、相位控制字位宽选择取决于DAC模块。

基于FPGA(DDS)的正弦波发生器的更多相关文章

- 基于FPGA的DDS设计(一)

最近在学习基于FPGA的DDS设计,借此机会把学习过程记录下来,当作自己的学习笔记也希望能够帮助到学习DDS的小伙伴. DDS(Direct Digital Synthesizer)直接数字合成器,这 ...

- 基于FPGA的音频信号的FIR滤波(Matlab+Modelsim验证)

1 设计内容 本设计是基于FPGA的音频信号FIR低通滤波,根据要求,采用Matlab对WAV音频文件进行读取和添加噪声信号.FFT分析.FIR滤波处理,并分析滤波的效果.通过Matlab的分析验证滤 ...

- 基于FPGA的VGA显示静态图片

终于熬到暑假了,记过三四周的突击带考试,终于为我的大二画上了一个完整的句号,接下来终于可以静心去做自己想做的事情了,前一阵子报了一个线上培训班,学学Sobel边缘检测,之前一直在学习图像处理,但是因为 ...

- (DDS)正弦波形发生器——幅值、频率、相位可调(二)

(DDS)正弦波形发生器--幅值.频率.相位可调(二) 主要关于调相方面 一.项目任务: 设计一个幅值.频率.相位均可调的正弦波发生器. 频率每次增加10kHz 相位每次增加 PI/2 幅值每次增加两 ...

- (DDS)正弦波形发生器——幅值、频率、相位可调(一)

(DDS)正弦波形发生器--幅值.频率.相位可调 一.项目任务: 设计一个幅值.频率.相位均可调的正弦波发生器. 频率每次增加1kHz. 相位每次增加 2*PI/256 幅值每次增加两倍 二.文章内容 ...

- 基于FPGA的飞机的小游戏

基于FPGA的飞机的小游戏 实验原理 该实验主要分为4个模块,采用至上而下的设计方法进行设计.由50M的晶振电路提供时钟源,VGA显示控制模块.图形显示控制模块.移动模块的时钟为25M,由时钟分频电路 ...

- 基于FPGA的图像去噪

目录 结构图 其中FPGA 控制模块为核心,通过它实现视频图像数据的获取.缓存.处理和控制各模块间通讯[1].由CCD 相机对目标成像,高速图像数据由camera link 实时传输[2],经信号转换 ...

- 基于FPGA的线阵CCD图像测量系统研究——笔记

本文是对基于FPGA的线阵CCD图像测量系统研究(作者:高尚)的阅读笔记 第一章绪论 1. 读读看 读了前面的摘要依然没有看懂作者要做什么.接着往下读....终于看到了一个字眼“基于机器视觉的图像测量 ...

- 基于FPGA的按键扫描程序

最近在学习FPGA,就试着写了个按键扫描的程序.虽说有过基于单片机的按键扫描处理经验,对于按键的处理还是有一些概念.但是单片机程序的编写通常都采用C写,也有用汇编,而FPGA却是采用VHDL或者Ver ...

- 基于FPGA的DW8051移植(三)

总结一下问题: 1) http://www.cnblogs.com/sepeng/p/4137405.html 基于FPGA的DW8051移植(一)里面用modelsim观测波形发现程序进入了ida ...

随机推荐

- Xdebug原理

前言: 前面一篇博文记录了Xdebug的安装配置.配置使用起来相对简单易懂,那么Xdebug的实现原理又是如何呢?所以就找了些资料来理解下其中的原理. 内容: Xdebug工作原理 1,IDE(如Ph ...

- alpha冲刺随笔(一)

项目Alpha冲刺(团队) Alpha冲刺第一天 姓名 学号 博客链接 何守成 031602408 http://www.cnblogs.com/heshoucheng/ 黄锦峰 031602411 ...

- Docker(五)-Dcoker容器

简单的说,容器是独立运行的一个或一组应用,以及它们的运行态环境. 如果把镜像看成面向对象中的 类 的话,那么容器就是 类 的实例化 对象. 容器 启动容器 启动容器有两种方式,一种是基于镜像新建一个容 ...

- List元素删除不会导致越界但有问题的写法

今天在论坛里看到一段请教list删除的问题,下面先看代码: public static void main(String[] args) { List<Integer> list = ne ...

- BZOJ2568 比特集合(树状数组)

考虑维护f[k][x]表示“最低k位所表示的数不大于x”的数的个数.那么查询时答案就为f[k][2k-1]-f[k][2k-1-1]. 同时记录每个数在集合中出现多少次.这样的话插入.删除已经解决了, ...

- 学习《Unix/Linux编程实践教程》(1):Unix 系统编程概述

0.目录 1.概念 2.系统资源 3.学习方法 4.从用户的角度来理解 Unix 4.1 登录--运行程序--注销 4.2 目录操作 4.3 文件操作 5.从系统的角度来理解 Unix 5.1 网络桥 ...

- MT【93】二次函数衣服一件

注:最后一行中$f(\dfrac{-x_1}{2})$应改为$f(\dfrac{-a}{2})$.有空再重新编辑.

- 自学Aruba1.2-WLAN一些基本常识802.11n速率计算方式、802.11n及802.11AC速率表

点击返回:自学Aruba之路 自学Aruba1.2-WLAN一些基本常识802.11n速率计算方式.802.11n及802.11AC速率表 1. 802.11n速率计算方式 以802.11g的54M最 ...

- BZOJ 4540 [Hnoi2016]序列 | 莫队 详细题解

传送门 BZOJ 4540 题解 --怎么说呢--本来想写线段树+矩阵乘法的-- --但是嘛--yali的机房太热了--困--写不出来-- 于是弃疗,写起了莫队.(但是我连莫队都想不出来!) 首先用单 ...

- 解题:CF1118F2 Tree Cutting (Hard Version)

题面 好题不问Div(这是Div3最后一题,不得不说Mike真是强=.=) 首先同一个颜色的点的LCA要和它们在一个划分出的块里,那么我们先按颜色把所有点到它们的LCA的路径涂色,如果这个过程中出现了 ...