(原创)Verilog三段式状态机

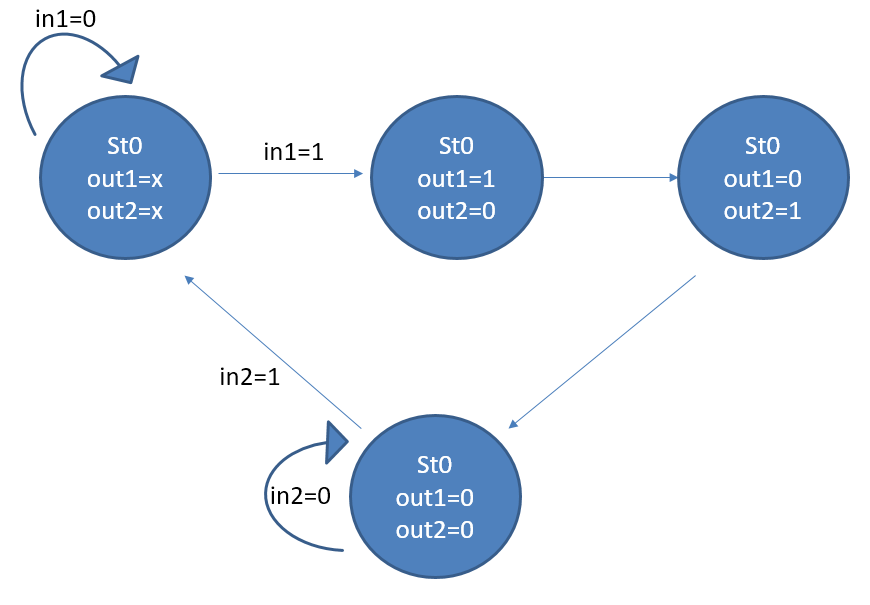

下面以上图一个简单的FSM说明三段式Verilog状态机范式:

`timescale 1ns / 1ps

module FSM(

clk,rst_n,

in1,in2,

out1,out2,

CS,NS

);

input clk,rst_n;

input in1,in2;

output out1,out2;

output [:] CS,NS; reg [:] CS,NS;

reg out1,out2; parameter St0 = 'b00,

St1 = 'b01,

St2 = 'b10,

St3 = 'b11; // 1、状态切换

always @(posedge clk or negedge rst_n)

if(!rst_n)

begin

CS<=St0;

end

else

CS<=NS; // 2、次态转移

always @ (*)

begin

case(CS)

St0:

begin

if(in1=='b1) NS=St1;

else NS=St0;

end

St1:

begin

NS=St2;

end

St2:

begin

NS=St3;

end

St3:

begin

if(in2=='b1) NS=St0;

else NS=St3;

end

default:NS=St0;

endcase

end //3、输出逻辑

always @(*)

begin

if(CS==St1) out1='b1;

else out1='b0;

if(CS==St2) out2='b1;

else out2='b0;

end endmodule

(原创)Verilog三段式状态机的更多相关文章

- Verilog三段式状态机描述

时序电路的状态是一个状态变量集合,这些状态变量在任意时刻的值都包含了为确定电路的未来行为而必需考虑的所有历史信息. 状态机采用VerilogHDL语言编码,建议分为三个always段完成. 三段式建模 ...

- verilog 三段式状态机的技巧

三段式代码多,但是有时钟同步,延时少,组合逻辑跟时序逻辑分开并行出错少. (1)同步状态转移 (2)当前状态判断接下来的状态 (3)动作输出 如果程序复杂可以不止三个always .always ...

- 10010序列检测器的三段式状态机实现(verilog)

序列检测器是时序数字电路设计中经典的教学范例,夏宇闻的<verilog数字系统设计教程>一书中有这个例子,用verilog设计一个“10010”序列的检测器.看完后我觉得F和G两个状态多余 ...

- Verilog笔记.三段式状态机

之前都是用的一段式状态机,逻辑与输出混在一起,复杂点的就比较吃力了. 所以就开始着手三段式状态机. 组合逻辑与时序逻辑分开,这样就能简单许多了. 但是两者在思考方式上也有着很大的区别. 三段式,分作: ...

- 简单三段式状态机实验2-LCD12864

此实验是在“基于I2C EPPRPM(AT24C02B) + LCD12864实验”基础上,把LCD模块里的一段式状态机改成三段式,I2C EPPROM模块暂时未改出来,一步一步来吧,改完后代码下载到 ...

- 简单三段式状态机实验1-SOS

一直想从一段式状态机切换到三段式状态机,从书上和网上不断搜寻三段式案例及方法,感觉很简单,就想拿之前做过的实验把一段式改成三段式,可是写起来并非那么简单,很棘手,改完后也没有成功,尤其状态机里面的计数 ...

- FPGA三段式状态机的思维陷阱

用三段式描述状态机的好处,国内外各位大牛都已经说的很多了,大致可归为以下三点: 1.将组合逻辑和时序逻辑分开,利于综合器分析优化和程序维护; 2.更符合设计的思维习惯; 3.代码少,比一段式状态机更简 ...

- 基于FPGA的三段式状态机

状态机分类: 通常, 状态机的状态数量有限, 称为有限状态机(FSM) .由于状态机所有触发器的时钟由同一脉冲边沿触发, 故也称之为同步状态机. 根据状态机的输出信号是否与电路的输入有关分为 Meal ...

- 三段式状态机 [CPLD/FPGA]

状态机的组成其实比较简单,要素大致有三个:输入,输出,还有状态. 状态机描述时关键是要描述清楚前面提高的几个状态机的要素,即如何进行状态转移:每个状态的输出是什么:状态转移是否和输入条件相关等. 有人 ...

随机推荐

- php获取id

private static function getClientIp() { if (getenv('HTTP_X_FORWARDED_FOR')) { $tmp = explode(',', ge ...

- winfrom导出DataGridView为Excel方法

声明:此方法需要电脑安装Excel软件 需要类库:Microsoft.Office.Interop.Excel.dll 可百度自行下载 方法代码: /// <summary> /// 导出 ...

- 调用 CURL 使用正则抓取信息

Class MyCurl{ protected $_pdo; //构造方法 链接数据库 public function __construct(){ $this->_pdo ...

- vue做nav切换

话不多说,直接上代码. 关键:通过点击来改变thisindex ,又thisinde == index来控制class是否含active来控制样式 简单效果如下:

- Azkaban工作流调度器

Azkaban工作流调度器 在Hadoop领域常用的工作流调度系统 Oozie,Azkaban,Cascading,Hamake等等. 性能对比: 安装: 创建ssl配置 keytool -keyst ...

- 学习PYTHON之路, DAY 10 进程、线程、协程篇

线程 线程是应用程序中工作的最小单元.它被包含在进程之中,是进程中的实际运作单位.一条线程指的是进程中一个单一顺序的控制流,一个进程中可以并发多个线程,每条线程并行执行不同的任务. 直接调用 impo ...

- 在Linux和Windows之间的远程控制的实现

主要开发工作用Linux,邮件和文档等主要在Windows,两者之间经常需要传输数据,两台主机都必须同时运行着. 但是,通常来说,它们需要同时准备两套显示器.鼠标和键盘,既占地方又不够方便. 远程控制 ...

- APP下载在微信无法打开 该如何处理

大家是不是经常会遇到微信内点击链接或扫描二维码无法打开指定网页的问题?只要你使用微信转发分享,相信你就一定会遇到,那么打不开的原因很简单了,就是被微信拦截了.这个问题我们只需要实现从微信内直接跳出到外 ...

- wholesale custom weighted blankets / travel weighted blankets

What is weighted blankets? Weighted blanket named heavy gravity blanket,for child and adult. Help re ...

- 小白的python之路Linux部分10/28&29

属主属组其他人对文件的rwx权限 1.userdel删东西不全,会有残留,