Xilinx约束学习笔记(三)—— 时序概念

3. 时序概念

发现对于时序基础的介绍这一块,Intel 的文档竟然要比 Xilinx 的详细,因此引用了很多 Intel 的文档内容。

3.1 术语

发送沿(launch edge),指用来发送数据的源时钟的活动边缘。采样沿(capture edge),Intel 的文档中称作latch edge。指的是对数据进行采样的目的时钟的活动边沿。源时钟(source clock),用来发送数据时钟。目的时钟(destination clock),用来对数据进行采样的时钟。建立时间要求(setup requirement),是发送沿和采样沿之间的关系,它定义了最严格的建立时间约束。建立时间关系(setup relationship),是指对建立时间进行检查。保持时间要求(hold requirement),是发送沿和采样沿之间的关系,它定义了最严格的保持时间约束。保持时间关系(hold relationship),是指保持时间进行检查。

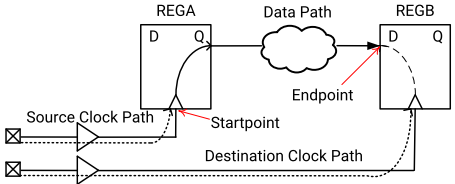

3.2 时序路径

时序路径的形态:

- 从输入端口到内部时序单元的路径。如图中

DIN到REGA的路径。 - 从时序单元到时序单元的内部路径。如图中

REGA到REGB的路径。 - 从内部时序单元到输出端口的路径。如图中

REGB到DOUT的路径。 - 从输入端口到输出端口的路径。如图中

In-2-Out Data Path。

时序路径分段:

源时钟路径(Source Clock Path)。

是指从时钟源点(通常是一个输入端口)到时序单元的时钟管脚所经过的路径。对于从输入端口开始的时序路径,没有源时钟路径。

数据路径(Data Path)。

指数据传播的路径。从时序单元的时钟引脚或数据输入端口开始,到时序单元的数据输入引脚或一个数据输出端口结束。

目的时钟路径(Destination Clock Path)。

是指从目的时钟源点(通常是一个输入端口)到采样时序单元的时钟管脚所经过的路径。对于终点为输出端口的时序路径,没有相应的目的时钟路径。

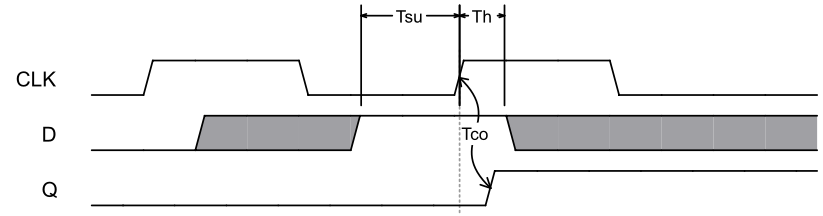

3.3 建立时间和保持时间

每个 FPGA 内部的寄存器都有两个固有的特性参数,建立时间和保持时间,其时间的长短是由器件本身决定的。

- 建立时间(Setup):在时钟沿之前,数据需要提前保持稳定的时间。如图中 Tsu 这一段时间内,数据 D 必须保持稳定不变。

- 保持时间(Hold):在时钟沿之后,数据需要继续保持稳定的时间。如图中 Th 这一段时间内,数据 D 必须保持稳定不变。

这两个时间是保证数据能够被正常采样的前提,如果不满足这两个时间要求,寄存器就可能会出现亚稳态,输出数据 Q 的值将不再是 D 上的输入值 ,而会是随机值。

寄存器还有另一个特性参数 Tco,指的是从时钟沿到达时钟引脚开始,到对数据 D 采样,直到输出至 Q 的延时。

Recovery 与 Setup 类似,Remove 与 Hold 类似,只是这两个参数针对的是寄存器的复位引脚,而不是数据输入引脚 D。

3.4 静态时序分析(Static Timing Analysis)

静态时序分析一般可分为两类:

- 最大延迟分析(Max Delay Analysis),包括 Setup 和 Recovery 分析。

- 最小延迟分析(Min Delay Analysis),包括 Hold 和 Remove 分析。

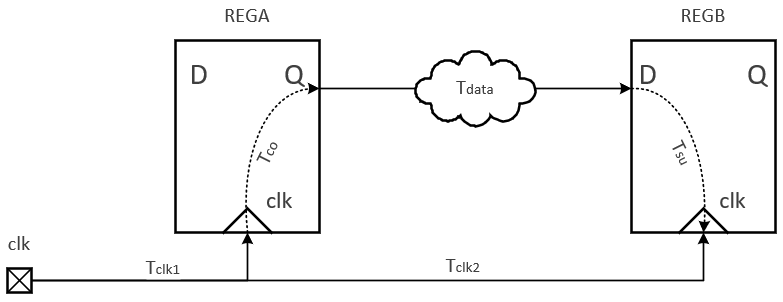

3.3.1 Setup/Recovery 时间检查

建立时间检查是为了确保在最悲观的场景下,仍然可以对数据安全的进行采样。

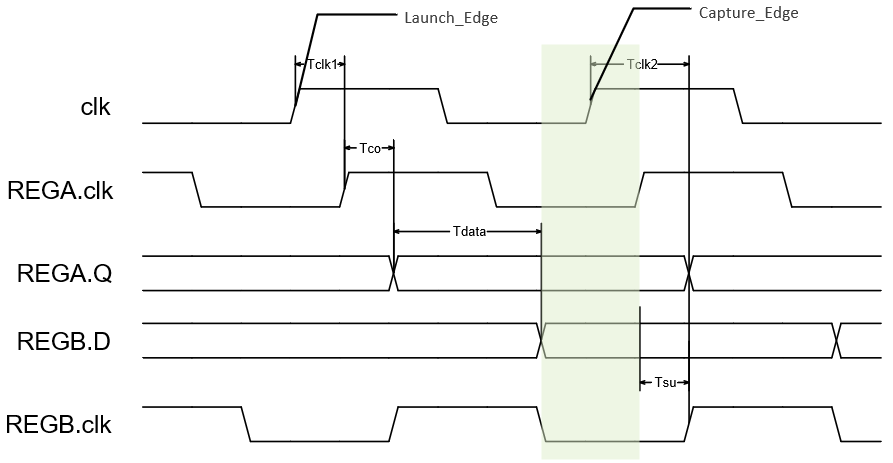

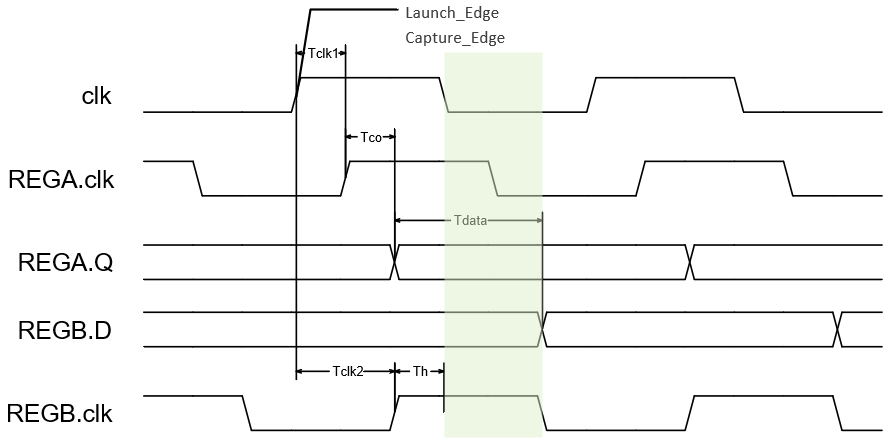

以两个寄存器 REGA 和 REGB 为例。两者由同一个时钟 clk 驱动。clk 经过源时钟路径 Tclk1 和目的时钟路径 Tclk2 延迟后,分别到达 REGA 和 REGB 的时钟引脚。如要满足 REGB 的建立时间 Tsu 的要求(REGB.D 在 REGB.clk 的采样沿之前的 Tsu 时刻之前就保持稳定不变)。语言可能不好理解,我们用公式来表达。

REGB.clk 的采样沿之前的 Tsu 时刻,我们把它称作 Data_Required_Time。依照下图,我们可以很容易得到:

\]

也就是说,REGA.Q 在经过 Tdata 延迟之后到达 REGB.D 的时刻在 Data_Required_Time 之前就即可满足建立时间要求。这个时刻也可以用公式来表式,我们称作它为 Data_Arrival_Time。

\]

将上述两个值相减,即可以得到建立时间的余量 Setup_Slack(下图中绿色部分)。

\]

当建立时间的余量为正数时,即表示满足建立时间要求。当为负数时,即不符合建立时间要求。

上图中需要理解的是,一般情况下,对于同一时钟,每个时钟沿既是发送沿也是采样沿。

上述公式都是在时钟完全理想的情况下推导的,但实际硬件上是不存在理想时钟的,因此要让代码在硬件上正常工作,还需要把时钟的不确定性(Clock Uncertainty)添加上。Clock Uncertainty 是指任何一对时钟边缘之间可能的时间变化之和。不确定性包括时钟抖动(Clock Jitter),某些硬件原语引入的相位误差,以及用户在约束(set_clock_uncertainty)中指定的时钟不确定性。对上计算公式修改后:

\]

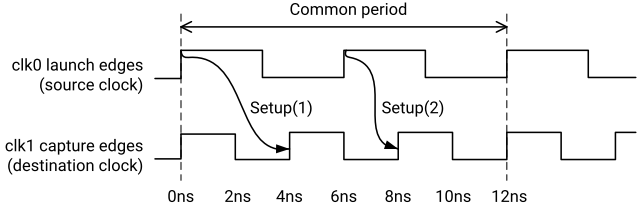

对于源时钟和目的时钟不是同一时钟时,建立时间检查只在两个时钟之间最悲观的建立时间关系上执行。例如下图,源时钟和目的时钟是不同频的,为 2:3 的关系,周期的最小公倍数为 12ns。在这 12ns 内有两个建立时间关系,Setup(1) 和 Setup(2)。Setup(1) 为 4ns,Setup(2) 为 2ns,所以使用 Setup(2) 做分析检查。

至于恢复时间余量的计算方法和建立时间的一样,只是恢复时间针对的是寄存器的复位端口。

3.3.2 Hold/Removal 时间检查

保持时间检查,是为了满足器件的保持时间特性。即在采样沿之后,数据仍要保持一段 Th 时间。如下图中,REGB.D 的新数据的到达时间要比采样沿至少落后 Th 才能保证满足保持时间特性。绿色部分是多出来的保持时间余量。

同样,把新数据要求到达的时间用公式表示如下,新数据实际到达时间只能比这个时间晚。

\]

新数据实际到达时间用公式表示如下:

\]

将上述两个值相减,即可以得到建立时间的余量 Hold_Slack(下图中绿色部分)。

\]

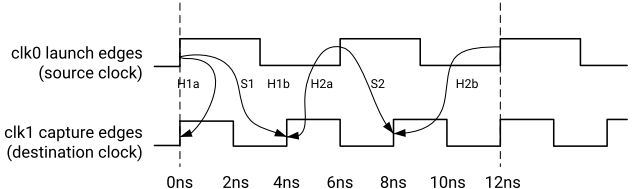

保持时间检查是基于建立时间检查的,对于每一个建立时间检查都有两个对应的保持时间检查:

- 第一 hold 检查确保 Launch Edge 打出的数据不会被 Capture Edge 前一个沿采集到。(下图中的H1a 和 H2a)

- 第二 hold 检查确保由下一个 Launch Edge 打出数据不会被当前 Capture Edge 采集到。(下图中的H1b 和 H2b)

在保持时间检查期间,时序引擎只报告两个时钟之间最差的保持关系。最差的保持关系并不总是与最差的建立关系联系在一起。时序引擎会检查所有可能的建立关系及其对应的保持关系,以确定最差的保持关系。

上图中,有两种 Setup 关系(S1 和 S2),每种 Setup 对应两种 Hold 关系(H1b 和 H2a 为两个 Setup 关系共有)。

- S1 对应两个 Hold 关系为 H1a(0ns)和 H1b(-2ns)。

- S2 对应两个 Hold 关系为 H2a(-2ns)和 H2b(-4ns)。

上述括号中的值是 Launch Edge 减去 Capture Edge 得到的,时序引擎在做时序分析的时候会选择 H1a 进行分析,而不是 H2b。因为 Launch Edge 比 Capture Edge 越是落后,余量就越大。

至于移除时间余量的计算方法和保持时间的一样,只是移除时间针对的是寄存器的复位端口。

Xilinx约束学习笔记(三)—— 时序概念的更多相关文章

- Xilinx约束学习笔记(一)—— 约束方法学

<Xilinx约束学习笔记>为自己阅读 Xilinx 官方 UG903 文档后的学习笔记,大多数为翻译得来,方便大家学习. 1 约束方法学 1.1 组织约束文件 Xilinx 建议将时序约 ...

- Xilinx约束学习笔记(二)—— 定义时钟

2. 定义时钟 2.1 关于时钟 为了获得最佳精度路径覆盖信息,必须正确定义时钟. 时钟要定义在时钟树的根 pin 或 port 上,称为 source point. 时钟的边缘应该由周期和波形进行组 ...

- 【转载】【时序约束学习笔记1】Vivado入门与提高--第12讲 时序分析中的基本概念和术语

时序分析中的基本概念和术语 Basic concept and Terminology of Timing Analysis 原文标题及网址: [时序约束学习笔记1]Vivado入门与提高--第12讲 ...

- 学习笔记(三)--->《Java 8编程官方参考教程(第9版).pdf》:第十章到十二章学习笔记

回到顶部 注:本文声明事项. 本博文整理者:刘军 本博文出自于: <Java8 编程官方参考教程>一书 声明:1:转载请标注出处.本文不得作为商业活动.若有违本之,则本人不负法律责任.违法 ...

- Oracle学习笔记三 SQL命令

SQL简介 SQL 支持下列类别的命令: 1.数据定义语言(DDL) 2.数据操纵语言(DML) 3.事务控制语言(TCL) 4.数据控制语言(DCL)

- java之jvm学习笔记三(Class文件检验器)

java之jvm学习笔记三(Class文件检验器) 前面的学习我们知道了class文件被类装载器所装载,但是在装载class文件之前或之后,class文件实际上还需要被校验,这就是今天的学习主题,cl ...

- NumPy学习笔记 三 股票价格

NumPy学习笔记 三 股票价格 <NumPy学习笔记>系列将记录学习NumPy过程中的动手笔记,前期的参考书是<Python数据分析基础教程 NumPy学习指南>第二版.&l ...

- ES6学习笔记<三> 生成器函数与yield

为什么要把这个内容拿出来单独做一篇学习笔记? 生成器函数比较重要,相对不是很容易理解,单独做一篇笔记详细聊一聊生成器函数. 标题为什么是生成器函数与yield? 生成器函数类似其他服务器端语音中的接口 ...

- muduo网络库学习笔记(三)TimerQueue定时器队列

目录 muduo网络库学习笔记(三)TimerQueue定时器队列 Linux中的时间函数 timerfd简单使用介绍 timerfd示例 muduo中对timerfd的封装 TimerQueue的结 ...

随机推荐

- Java方法02——定义与调用

方法的定义与调用 定义与调用 例子 package method; public class Demon03 { public static void main(String[] arg ...

- C++ //继承中构造和析构顺序

1 #include <iostream> 2 #include <string> 3 using namespace std; 4 5 class Base 6 { 7 pu ...

- GitHub不再支持密码验证解决方案:SSH免密与Token登录配置

今天提交代码,push到GitHub上,突然出现这个问题. remote: Support for password authentication was removed on August 13, ...

- Redis-缓存穿透/击穿/雪崩

1. 简介 如图所示,一个正常的请求 客户端请求张铁牛的博客. 服务首先会请求redis,查看请求的内容是否存在. redis将请求结果返回给服务,如果返回的结果有数据则执行7:如果没有数据则会继续往 ...

- 日志导致jvm内存溢出相关问题

生产环境日志级别为info,请看如下这行代码: LOGGER.debug("the DTO info: {}", JSON.toJSONString(DTO)); 这段代码主要有两 ...

- Shell-05-函数

函数 函数定义 shell中函数的定义格式如下 [ function ] funname [()] { action; [return int;] } 说明: 1.可以带function fun() ...

- 【MySQL】自定义数据库连接池和开源数据库连接池的使用

数据库连接池的概念 数据库连接背景 数据库连接是一种关键的.有限的.昂贵的资源,这一点在多用户的网页应用程序中体现得尤为突出.对数据库连接的管理能显著影响到整个应用程序的伸缩性和健壮性,影响到程序的性 ...

- npm常用命令及其node相关工具汇总

它是一个事件驱动异步I/O单进程的服务端JS环境,基于Google的V8引擎,V8引擎执行Javascript的速度非常快,性能非常好. 浏览器是JS的前端运行环境. Node.js是JS的后端运行环 ...

- 如何在github上fork以及同步原作者代码

参考网址:https://blog.csdn.net/llll2020/article/details/86140488 转 GitHub上fork别人打代码后如何保持和原作者同步的更新 </ ...

- PL/SQL 安装使用

PL/SQL 安装 前提:安装Oracle 使用 登录 oracle连接地址格式 ip:端口/ServerName,如192.168.136.130:1521/xe 新建菜单 Sql-Window 编 ...