第一个FPGA工程—LED流水灯

这一章我们来实现第一个FPGA工程—LED流水灯。我们将通过流水灯例程向大家介绍一次完整的FPGA开发流程,从新建工程,代码设计,综合实现,管脚约束,下载FPGA程序。掌握本章内容,大家就算正式的开始入门FPGA开发了。

1.1.1.电路说明

1.1.2.新建工程

第一步:从开始菜单启动Quartus II 13.1(64 bit) ,如下图。

第二步:菜单栏选择File—>New

Project Wizard,新建工程。

第三步:弹出新建工程对话框,点击Next,下一步。

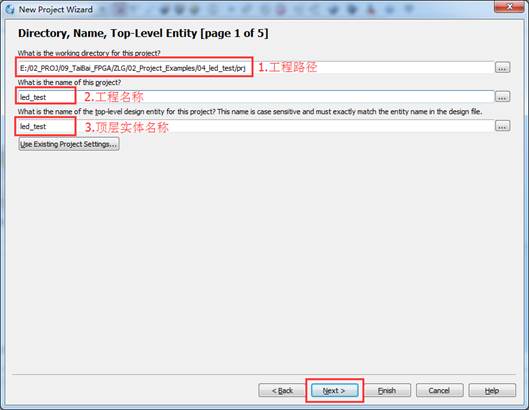

第三步:如下图,依次设置工程的存放路径,工程名称,顶层文件名称,如图依次设置好,这里我们将所有工程相关的文件放在prj文件夹内,便于工程文件与源码文件的管理,同时要保持工程名称与顶层实体名称一致,继续Next。

第四步:添加设计文件,这一步我们不需要添加,后续我们会新建相应的代码文件。这里继续Next。

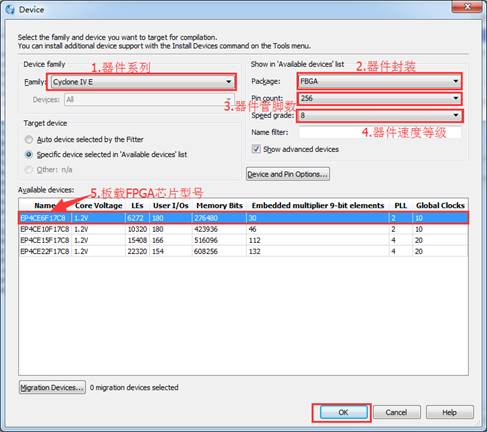

第五步:选择FPGA器件,如图所示,这里我们选择器件家族是CycloneIV系列的,封装是FBGA,管脚数为256,速度等级为8。这里速度等级越小,速度越快。这里我们FPGA的具体型号为EP4CE6F17C8。大家通过这个对话框了解这个器件的基本资源。这里我简单介绍一下这些资源的名称,在后面的章节里我们还会详细讲解FPGA内部资源与结构。

1、CoreVoltage是内核电压,Cyclone IV的内核电压是1.2V。

2、LE是Altera最基本的逻辑单元,LEs表示FPGA的所有的逻辑资源, 我们这款芯片的逻辑资源数为6272。

3、User I/Os表示用户IO数,这里共有180个IO可以供用户使用。

4、Memory Bits与embedded multiplier 9-bit elements实际是一回事,后者简称M9K,M9K就是指位宽为9bit,深度为1K的RAM。这里一共有30个M9K,大家计算一下9*1024*30=276480就是Memory Bits。

5、PLL锁相环,内部一共有两个锁相环。

6、Global

clocks全局时钟网络数,这里一共有10个。设计中的时钟信号会优先全局时钟资源。

第六步:设置EDA工具,这里我们就设置一下仿真工具,使用默认Modelsim

-Altera,语言选择Verilog。实际后面我们不建议大家使用Modelsim-Altera。我们会推荐大家在直接使用Modelsim-SE,后者的通用性更强。继续Next。

第七步:总结新建工程的基本信息。到这里就完成工程的建立。

1.1.3.代码设计

大家阅读本节前,首先应该对Verilog语法有一定了解,其次阅读我们提供的编码规范文件,了解基本的命名规则和工程架构,从一开始就培养良好的编码习惯。

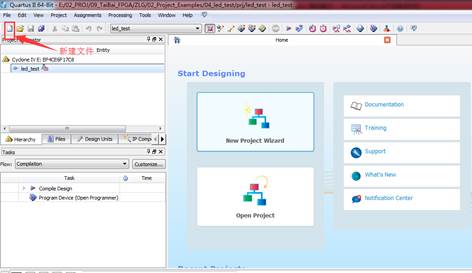

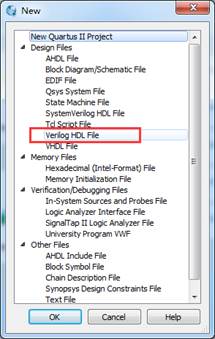

第一步:新建verilog源文件,如下图,点击新建文件图标,或者通过菜单栏File—>New打开新建文件向导。

第二步:在新建文件向导中,选择Verilog HDL File,点击OK。

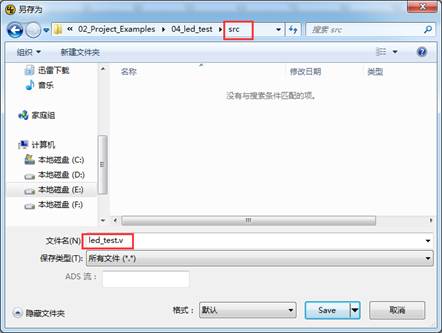

第三步:因为我们已经配置过UltraEdit为默认编辑器,此时会打开UltraEdit(注意:UltraEdit编辑Verilog代码前,要添加语法高亮文件,详见3.3.3节内容),弹出新建源文件,将源文件另存至src文件夹下,命名为led_test.v与顶层实体名称一致。我们将源码文件和工程文件放在不同文件夹下,方便日后的工程维护。

第四步:编写代码逻辑,这里我们实现了一个流水灯。这里我们用了一个27位的计数器,时钟频率为50MHz,周期为20ns,当计数到第25位置位时,计数器值为25’d16777216,此时时间为16777216*20ns=335ms。这样每大约经过335ms,计数器的[26:24]位就会加1。我们第一个always实现计数器,第二个always实现控制不同时间时LED的输出,即每隔335ms改变一次LED的输出状态。

1. module led_test

2. (

3. input i_clk, //input clk ,50mhz

4. input i_rst_n, //reset, active low

5. output reg [3:0]o_led //led

out

6. );

7. reg [26:0] led_count;

8. //-------------------------------------------------------------------

9. //

流水灯计数器

10. //-------------------------------------------------------------------

11. always @ (posedge i_clk or negedge i_rst_n)

12. begin

13. if(!i_rst_n)

14. led_count <=27'd0;

15. else

16. led_count <=led_count + 27'd1;

17. end

18. //-------------------------------------------------------------------

19. // 计数器bit24置1,表示已大约计数335ms,每隔335ms,led_count[26:24]自动加1

20. //-------------------------------------------------------------------

21. always @ (posedge clk or negedge i_rst_n)

22. begin

23. if(!i_rst_n)

24. o_led <=4'b1111;

25. else begin

26. case(led_count[26:24]) //when

25th bit set= 335ms

27. 3'b000: o_led<= 4'b1110;

28. 3'b001: o_led<= 4'b1101;

29. 3'b010: o_led<= 4'b1011;

30. 3'b011: o_led<= 4'b0111;

31. 3'b100: o_led<= 4'b1100;

32. 3'b101: o_led<= 4'b1001;

33. 3'b110:o_led <= 4'b0011;

34. 3'b111: o_led<= 4'b0000;

35. default: o_led<= o_led;

36. endcase

37. end

38. end

39. endmodule

1.1.4.综合实现

对于刚接触FPGA的同学可能不太了解综合实现的意思,其实简单里说,综合实现就相当于单片机的编译过程。而FPGA的编译过程不像其他高级语言的编译过程,FPGA编译过程实际是相应硬件电路的实现过程。

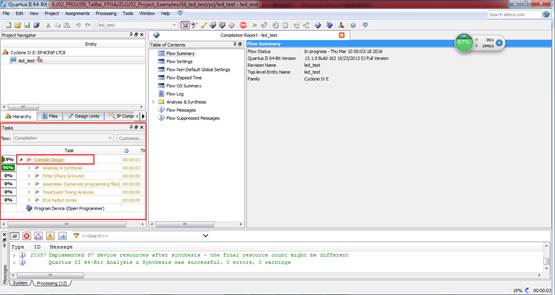

第三小节,我们完成了代码设计,我们就可以综合实现了。步骤就是双击task窗口下的“Compile

Design”,就会开始综合实现了。

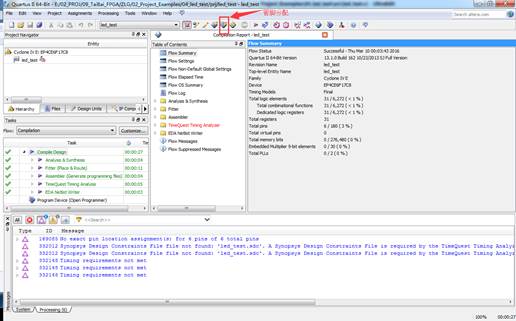

Altera的FPGA编译过程大致分为以下几个过程:分析综合,布局布线,生成烧写文件,时序分析,EDA网表生成。如下图所示。

分析综合:这个过程首先是完成对源码文件的语法编译,其次是将我们设计的语言综合成相应的网表文件,而这个网表文件实际是与FPGA上资源是相互映射的。首先什么是网表文件?网表文件描述了相应工程的FPGA设计中包含了FPGA资源,同样描述了这些资源又是如何连接的。其次,FPGA有哪些资源?我们会在后续章节详细介绍,这里就说一个最简单的资源——触发器,这个是我们数电里面学习过的,在FPGA里一般叫做寄存器。例如我们这个工程中,最终led_count和o_led都会映射到相应的寄存器。

布局布线:这个过程是根据分析综合中得到的网表文件进行的,如果大家有PCB设计经验可能会更好理解。所谓布局,就像PCB布局,将设计中用到的资源布局到FPGA器件内部不同的位置。所谓布线,同样类似PCB布线,将FPGA内部用到的资源根据网表文件中描述的链接关系连在一起。

生成烧写文件:这个过程比较好理解,基于上述过程产生的文件,再生成用烧写FPGA的文件。

EDA网表生成:这个过程则是用来生成仿真所需网表文件。仿真时会用到。

1.1.5.管脚分配

这一节我们将介绍管脚分配,管脚分配过程中我们会同时讲解关于Altera FPGA管脚主要特点及分类。

第一步:管脚分配前应该先将源码文件进行综合,让Quartus获取相应的IO信息。这一步第四小节已经讲了,我就不做详细介绍了。

第二步:打开管脚分配工具Pin Planner,如下图。或者可以通过菜单栏Assignments—>Pin Planner打开,也可以下图所示快捷图标打开。

第三步:分配管脚之前,我们先介绍一下FPGA的IO分布情况、管脚的特点及种类,以及Pin Planner工具的使用。如下图为Pin

Planner界面。

Pin

Planner工具界面大致可分为以下几个部分:

总体管脚布局区域:如图所示,中间器件图描述了每个管脚的位置。

Report区域:通过这个区域,将相应信息打上√,就可以高亮我们所关心的IO信息。这里我们高亮IO的bank信息。FPGA的管脚是分bank的,而且每个bank的IO的电平都可以独立配置的。

Tasks区域:这个区域包含了很多IO信息,我们可以双击需要的IO信息,相应的信息就会添加到Repoat区域中。

Pin Legend区域:这里具体说明IO的所有种类,并用不同的颜色和形状表示出来。而FPGA的IO管脚大致分为 用户IO,配置管脚,电源管脚这几类。

管脚分配区域:我们在这个区域内对我们设计中的IO进行分配。

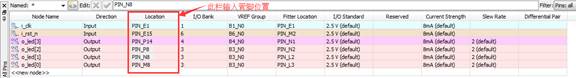

第四步:分配管脚。在Location栏中输入相应管脚的位置,完成管脚分配。

1.1.6.程序烧写

第一个FPGA工程—LED流水灯的更多相关文章

- 利用简单的有限状态机(FSM)来实现一个简单的LED流水灯

有限状态机,(英语:Finite-state machine, FSM),又称有限状态自动机,简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型. 有限状态机是指输出取决于过去 ...

- 使用CCS10新建TMS320F28335工程并闪烁LED(流水灯)程序

学习TMS320F28335使用Code Composer Studio 10.4.0下载和安装本文不再叙述. 1. 新建工程 1.1选择目录新建工作区 1.2打开软件界面如下图所示: 1.3选择新建 ...

- 第一个FPGA工程----点亮开发板上的3个LED灯

第一个FPGA工程----点亮开发板上的3个LED灯 1.新建FPGA工程 开启Quartus2的画面 File--New Project Wizard..指定工程的路径与工程名 指定所使用的FPGA ...

- S3C6410裸奔之旅——RVDS2.2编译、仿真、调试过程 LED流水灯---转的

S3C6410裸奔之旅——RVDS2.2编译.仿真.调试过程 LED流水灯 (2012-10-13 23:56:30) 转载▼ 标签: s3c6410裸奔 ok6410 rvds2.2 rvds2.2 ...

- 学习笔记——单片机简介 & 点亮LED & 流水灯 & 电路基础【更新Ing】

视频地址:https://www.bilibili.com/video/av10765766 超详细!!!!!! 单片机内部三大资源 [资源:单片机可提供使用的东西] FLASH 可以重复擦写 断电后 ...

- 关于LED 流水灯的软件调试方法(非开发板调试)

因为: 硬件 norflash 有寿命,所以尽量少用,而且自己也不会把 程序在 KEIL中从SDRAM 中调试,不会设置.所以采取软件虚拟的方法调试. 主要修改一下几部分: 1. ledcircle ...

- LED流水灯(二)

记住看汇编的时候是红在上面 黑色在下面 startup.s 程序 ; MDK跑马灯实验; PRESERVE8 // 字节对齐关键词 ,汇编有8位对齐的要求,要添加 AREA ...

- TQ210裸机编程(2)——LED流水灯

两个文件start.S和led.c start.S .global _start @声明一个全局的标号 _start: bl main ...

- [DM8168]Linux下控制GPIO实现LED流水灯

首先加载驱动模块,应用程序通过调用API实现GPIO控制功能. 驱动程序: /* * fileName: led_gpio.c * just for LED GPIO test * GP1_14 -& ...

随机推荐

- [hgoi#2019/2/16t2]friend

题目描述 在一个遥远的国度里有n个人,每个人手上写着4个互不相同的数. 这个国度比较奇怪,如果两个人至少有一个数字相同,则他们是一对朋友. 现在这n个人按序号从左到右排成了一排,每个人都想知道在他左边 ...

- Windows Server 2008配置Network Load Balancing(服务群集)

最近配置SharePoint 2013 WFE 时,客户提到要让多台WFE能load balance,于是研究了下Network Load Balancing. 当把一台服务器 ...

- cf379F New Year Tree (树的直径+倍增lca)

可以证明,如果合并两棵树,新的直径的端点一定是原来两树中直径的端点 可以把新加两个点的操作看成是把两个只有一个点的树合并到原来的树上,然后用其中的一个点去和原来树上的直径两端点更新直径就可以了 #in ...

- php框架:Flight 简介

Flight是一个php的极简的有着微内核的框架,能过快速的构建RESTful的应用 官网地址: http://flightphp.com/ github地址:https://github.com/m ...

- 【CSS】绝对定位和相对定位

html:定位层 特点: >>完全脱离默认文档流,独立于立体层面的Z轴之上. >>和float浮动一样都脱离了默认文档流,但float元素与默认文档流之间会相互产生影响,而定位 ...

- 5个强大的Java分布式缓存框架

在开发中大型Java软件项目时,很多Java架构师都会遇到数据库读写瓶颈,如果你在系统架构时并没有将缓存策略考虑进去,或者并没有选择更优的缓存策略,那么到时候重构起来将会是一个噩梦.本文主要是分享了5 ...

- 质量不合格_区分excel两列不同的值

sklearn实战-乳腺癌细胞数据挖掘(博主亲自录制视频) https://study.163.com/course/introduction.htm?courseId=1005269003& ...

- MySQL中的时态(日期/时间)数据类型

时态类型的取值范围 mysql> create table t (dt datetime,d date,t time); Query OK, 0 rows affected (0.30 sec) ...

- div中让内容能不换行就尽量不换行.【纯原】

div中让内容能不换行就尽量不换行,部分左对齐,部分右对齐. <html> <head> <title>九歌·少司命</title> <style ...

- css postion 属性区别【原】

CSS样式中的postion元素有四个属性,即static | absolute | fixed | relative. static: 默认值.无特殊定位,遵循HTML基本定位规则 . fixed: ...