SignalTap II进阶学习

1. 多级触发

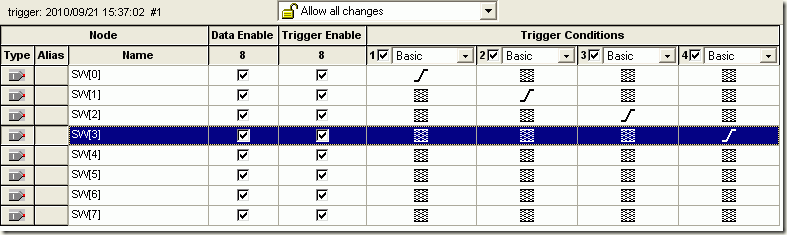

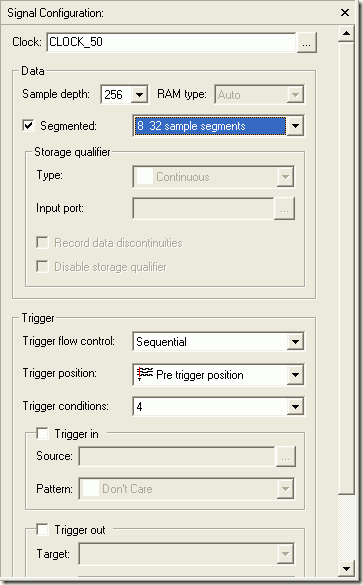

有时候我们可能需要利用多个信号(最多10个)依次触发后,观察特定的值。这这时候我们可以增加触发条件来满足我们的需求。

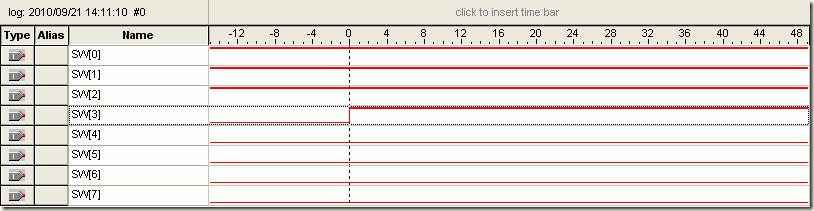

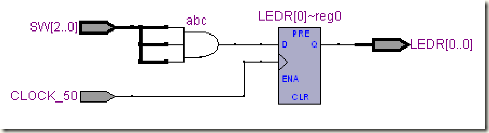

多个触发信号如上图所示,只有依次发生SW[0]上升沿、 SW[1]上升沿、SW[2]上升沿和SW[3]上升沿后,才会抓取得到信号。

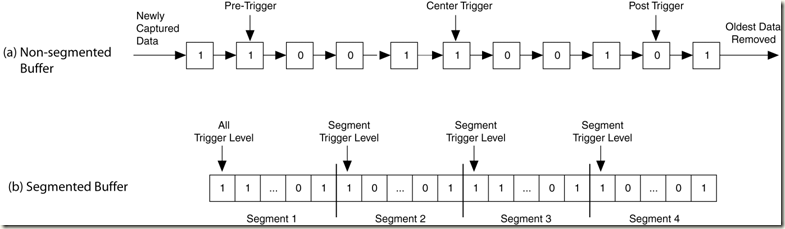

2. 高级触发条件

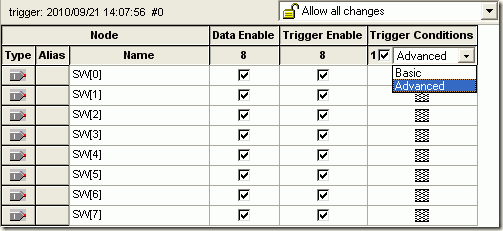

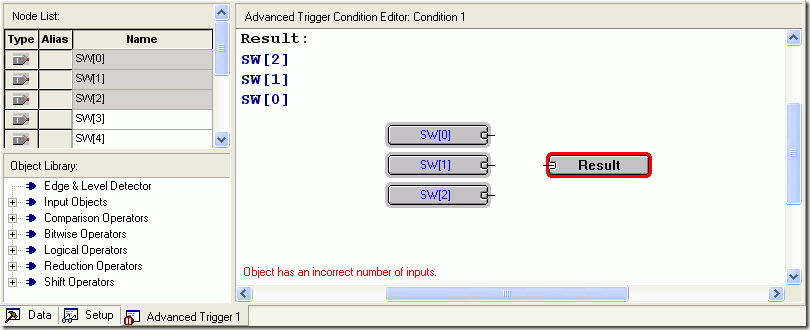

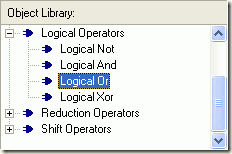

有时候我们的触发条件不能简单的高低电平或者上升沿、下降沿,可能是多个信号的逻辑电路,这时候需要使用高级触发条件。比如,三个信号只要出现上升沿或者下降沿时,触发抓取信号,即只要这三个信号有一个发生变化就抓信号。

(1) 首先在Trigger Conditions里选择Advanced。

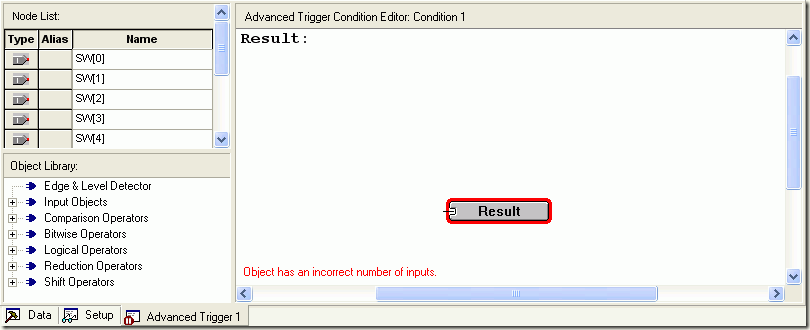

(2) 高级触发编辑窗口:

(3) 将3个信号节点选中拖进编辑窗口:

(4) 下一步是增加逻辑运算符到电路中,一个是逻辑或,另一个是电平和边沿检测器:

(5) 下一步是设置电平和边沿检测器的敏感属性,双击它,因为检测是否改变,所以选择“E”。

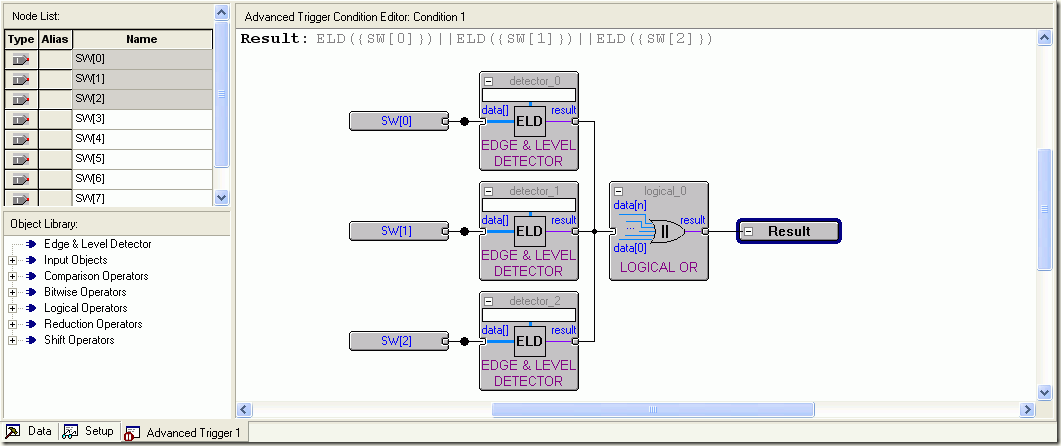

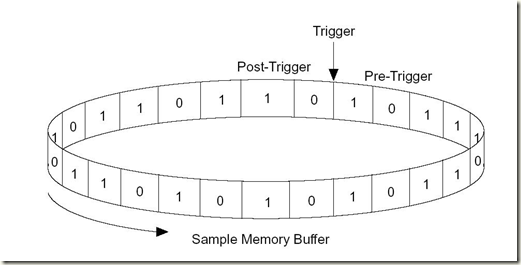

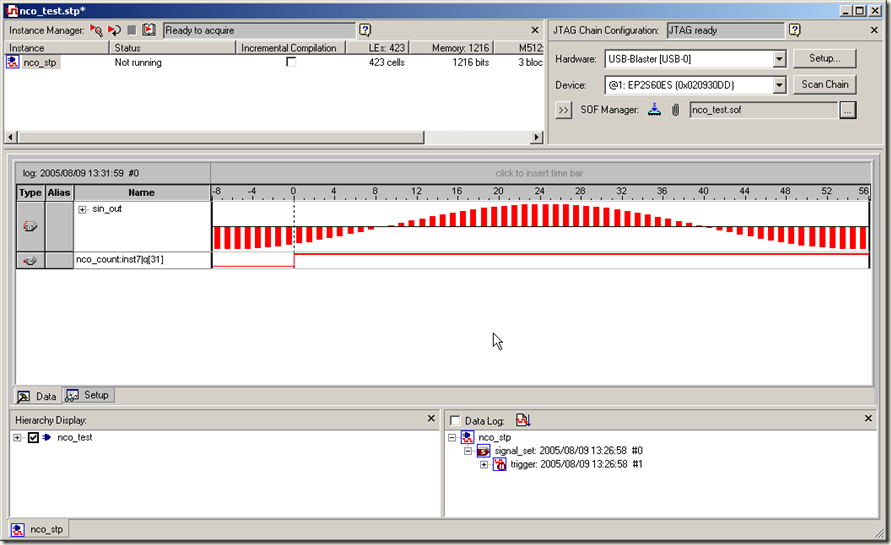

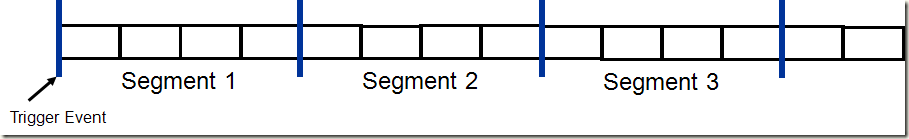

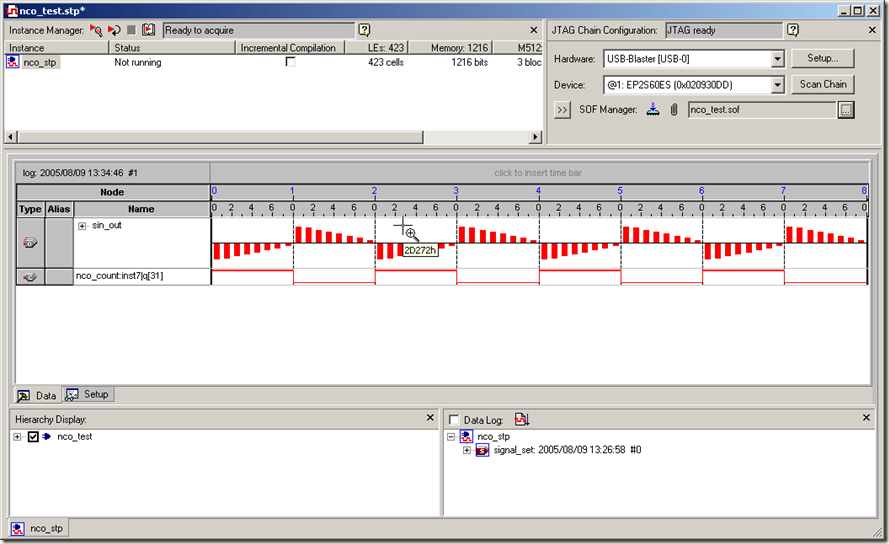

3. Buffer Acquisition Modes(缓冲区获取模式)

一种是不分割连续,另一种是分割模式。

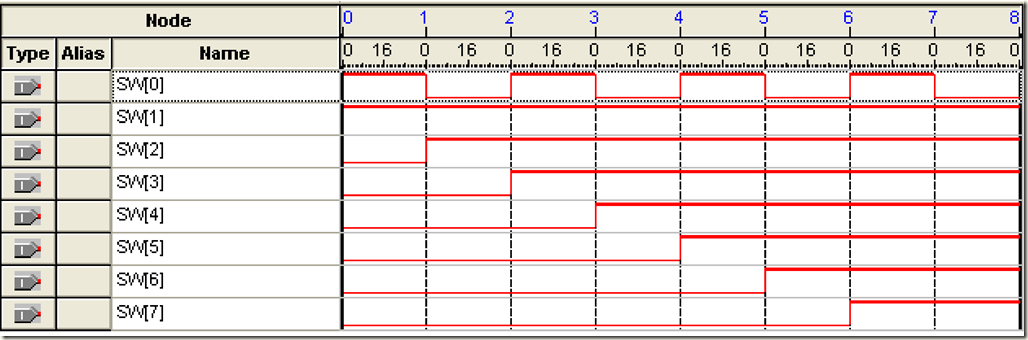

将大小为256为的采样深度分为8个32个采样点的块,允许捕获8次触发事件,下面是触发条件为SW[0]任意边沿触发的捕获结果。

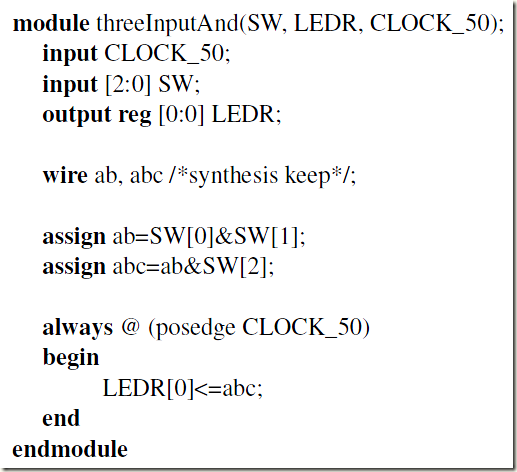

4. Use of Synthesis Keep Directive

有时候我们需要观察一些中间信号,但是选用的过滤器为pre-synthesis,由于软件的优化,这些信号被优化掉了(wire型居多),使得我们获取这些信号。这时候一种方法就是利用综合语句Synthesis Keep Directive。

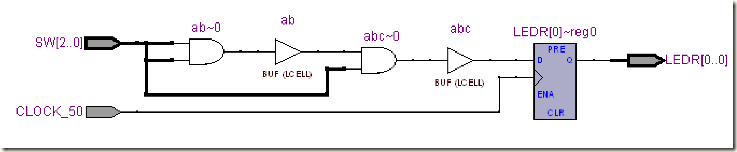

如果没有综合语句keep,RTL视图如下图所示,那么就不存在我们要观察的信号了。

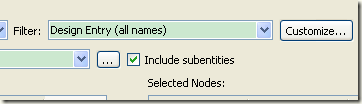

另外,还可以在Filter中选择Design Entry(all names),那么就会有你要的任何信号。

当然你也可以为wire分配寄存器,或者引出输出引脚,但是这样使设计复杂冗余。

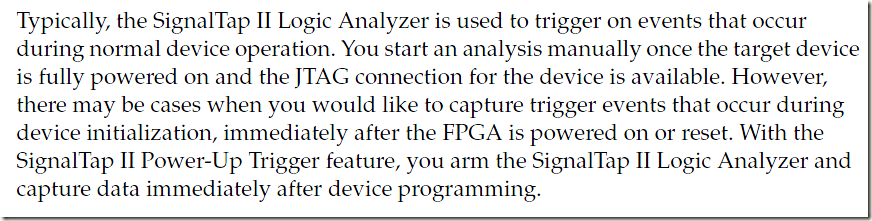

5. Power-Up Trigger

通常情况下,SignalTapII只能探测当其Run起来以后器件运行情况,其未Run之前的情况就无法探测得到。往往我们有时候非常需要了解系统中上电伊始某些信号的状况(比如有些系统需要上电几秒甚至几毫秒内要完成的某些初始化动作),这是在以往SignalTapII无法办到的。自从SignalTapII加入了Power-up Trigger特性以后这个问题就得到了解决。

上电触发用在上电后且在ELA(内嵌逻辑分析仪)运行之前。

具体步骤如下:

1)使能Power-Up Trigger;

2)为Power-up Trigger配置触发条件;

3)重新编译工程并加载器件;

4)首次Analizer Run显示的是Power-Up Trigger采集到的数据;

5)持续Run回到Run-time Trigger模式。

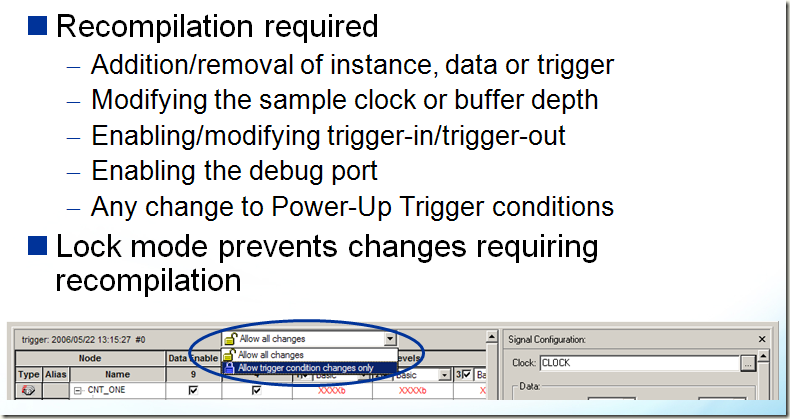

6. 重编译

由于我们调试的需要,经常修改STP文件,只有改变信号的触发信号(高低电平、上升沿、下降沿、任意边沿、不关心)时,不用重编译,其他的改变都需要重新编译工程。

SignalTap II进阶学习的更多相关文章

- Matlab 进阶学习记录

最近在看 Faster RCNN的Matlab code,发现很多matlab技巧,在此记录: 1. conf_proposal = proposal_config('image_means', ...

- SignalTap II逻辑分析仪的使用

一.例子 我们使用如图1所示的verilog代码所实现的开关电路作为例子.这个电路把DE系列开发板上的前8个开关简单的和对应的8个红色LED相连接.它是这样工作的:在时钟(CLOCK_50)的上升沿读 ...

- PHP程序员进阶学习书籍参考指南

PHP程序员进阶学习书籍参考指南 @heiyeluren lastmodify: 2016/2/18 [初阶](基础知识及入门) 01. <PHP与MySQL程序设计(第4版)> ...

- SignalTap II应用小实例之触发位置

概述 SignalTap II一直以来都是笔者调试Altera FPGA设计的利器,最近比较有时间静下心来研究SignalTap II某些细节,虽然笔者有过不少关于SignalTap的使用,且也发表过 ...

- zuul进阶学习(二)

1. zuul进阶学习(二) 1.1. zuul对接apollo 1.1.1. Netflix Archaius 1.1.2. 定期拉 1.2. zuul生产管理实践 1.2.1. zuul网关参考部 ...

- Quartus prime 16.0 signaltap II 使用

前言 由于逻辑分析仪太贵,altera贴心提供signal tap II来观察输出波形,不过使能signaltap II会占用片内ram,毕竟原理就是把数据采样到ram中再通过jtag口上传到quar ...

- ROS进阶学习笔记(11)- Turtlebot Navigation and SLAM - ROSMapModify - ROS地图修改

ROS进阶学习笔记(11)- Turtlebot Navigation and SLAM - 2 - MapModify地图修改 We can use gmapping model to genera ...

- SignalTap ii的使用

1.实现原理 SignalTap II获取实时数据的原理是在工程中引入Megafunction中的ELA(Embedded Logic Analyzer),以预先设定的时钟采样实时数据,并存储于FPG ...

- 如何使用SignalTap II觀察reg與wire值? (SOC) (Verilog) (Quartus II) (SignalTap II)

Abstract撰寫Verilog時,雖然每個module都會先用ModelSim或Quartus II自帶的simulator仿真過,但真的將每個module合併時,一些不可預期的『run-time ...

随机推荐

- Android 开发 -------- 自己定义View 画 五子棋

自己定义View 实现 五子棋 配图: watermark/2/text/aHR0cDovL2Jsb2cuY3Nkbi5uZXQvbG92ZV9KYXZjX3lvdQ==/font/5a6L5L2T ...

- VS2015调用Matlab2017a环境配置(转载)

VS2015调用Matlab2017a环境配置 一定要在Debug+x64平台下进行配置,x64,x64,x64!!!* 1.配置环境变量 右键计算机—–>属性——>高级系统设置——> ...

- 【犀牛书笔记】JavaScript正则表达式的模式匹配

正则表达式,是一个描述字符模式的对象. JavaScript用RegExp类表示正则表达式 String和RegExp都定义了相关方法 原创文章,转载请注明:http://www.cnblogs.co ...

- Zookeeper中的选举机制

Zookeeper虽然在配置文件中并没有指定master和slave,但是,zookeeper工作时,是有一个节点为leader,其他则为follower.leader是通过内部的选举机制临时产生的. ...

- mui时间选择器选择今天以后的时间

<script type="text/javascript"> (function($) { $.init(); // var result = $('#result' ...

- Easyui datebox单击文本框显示日期选择

Easyui默认是点击文本框后面的图标显示日期,为了更进一步优化体验 修改为单击文本框显示日期选择框 修改jquery.easyui.min.js(作者用的是1.3.6版本,其他版本或有区别) 可 c ...

- EJB包含哪3种bean

EJB包含哪3种bean 解答:session bean(会话bean), entity bean(实体bean), message bean(消息bean)

- setAttribute()使用方法与IE兼容解决方法

我们经常需要在JavaScript中给Element动态添加各种属性,可以使用setAttribute()来实现,但涉及到了浏览器的兼容性问题.setAttribute(string name,str ...

- 【BZOJ】3392: [Usaco2005 Feb]Part Acquisition 交易(spfa)

http://www.lydsy.com/JudgeOnline/problem.php?id=3392 同1674 #include <cstdio> #include <cstr ...

- Spring MVC学习-----------springMVC-mvc.xml

springMVC-mvc.xml 配置文件片段解说 (未使用默认配置文件名称) <?xml version="1.0" encoding="UTF-8" ...