数字电路中的等效电路和FPGA中的等效电路

欢迎各位朋友关注“郝旭帅电子设计团队”,本微信公众号会定时更新相关技术类资料、软件等等,希望各位朋友都能在本微信公众号获得一些自己想要的“东西”。

本篇内容主要介绍数字电路中的等效电路(注意:是数字电路,不是模拟电路)。

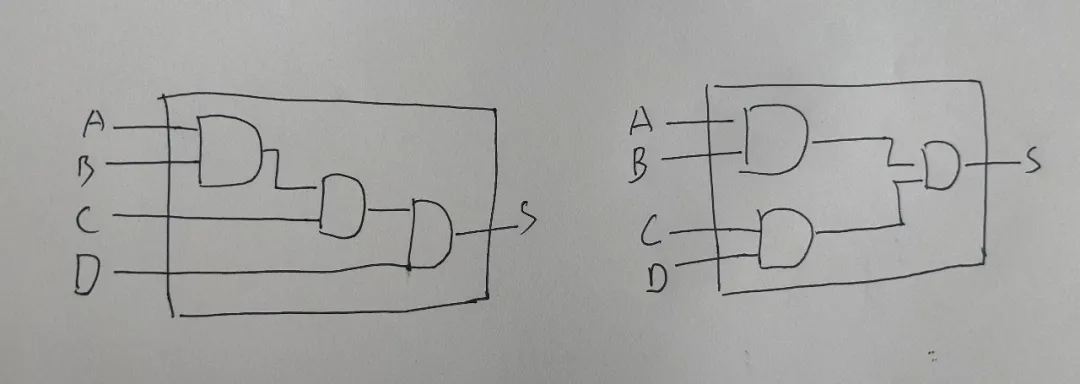

上述为利用三个二输入与门组成的两种不同结构的四输入与门。

无论是哪一种架构,都可以完成四输入与门的功能,所以我们一般将这两种电路称之为“等效电路”。

“等效电路”一定是完全等效的吗?

答案是否定的。对于数字电路来说,有两个相对来说比较重要的指标:一个是逻辑关系(逻辑如果不对的话,啥也白扯);一个是实现逻辑输出所带来的延迟。

在上述的两种结构中,将四个输入信号同时放置到两种结构的输入端,那么左侧结构将会经过三个门延迟得到结果(线延迟忽略),右侧结构将会经过两个门延迟得到结果。如果我们保持输入不变,经过大于三个门延迟的时间去看结果,那么两个结构都得出结果,所以是等效的。如果我们保持输入不变,在两到三个门延迟的时间之间去看结果,那么左侧结构没有出现结果,右侧结构将会得出结果,那么此时两个结构是不等效的。

所以说:等效是带有一定的条件的;如果想要不同的电路结构得出同样的电路输出,那么必须要满足一定的条件(一般是输入不变,等待足够的时间延迟)。

在FPGA中,是利用存储器(LUT)来等效数字逻辑门。

存储器(Memory)是现代信息技术中用于保存信息的记忆设备。它根据控制器指定的位置存入和取出信息。

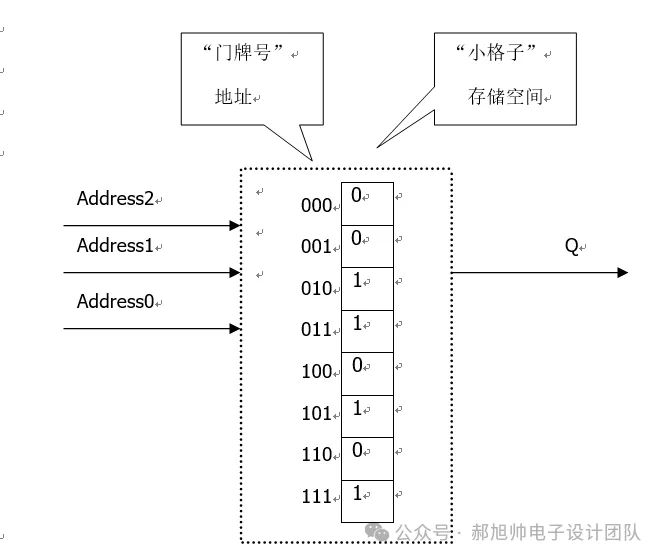

存储器中被分为了很多“小格子”,每一个“小格子”里面都可以放下很多的二进制数码。每个小格子都会有自己独特的标识,就像我们的门牌号一样,每个屋都是不同的。逻辑功能是当外部输入一个“门牌号”,对应的“小格子”里面的二进制数码就会输出。存储器中的“小格子”的数量,在制造时,就已经确定。“小格子”的数量确定了,那么“门牌号”的形势也就被确定了。例:我们有100个房间,我们只有两个十进制的数码就可以表示了,00至99。在存储器中,“门牌号”也只能用二进制数来表示,例如:有4个“小格子”,那么“门牌号”就要用两个二进制码来表示,00~11。每个“小格子”里面存放的二进制数的个数,在制造时,也就确定好了。通常我们把“门牌号”称为地址,“小格子”称为单个地址的存储空间,每个“小格子”能放下的二进制数码的个数称为“存储器的存储位宽”。制作一个拥有8个地址,单个地址空间为1个二进制数码的存储器。此时,地址码应该有三位,每个地址对应的存储二进制数码 的个数为1个。要求:000地址中,放入0;001地址中,放入0;010地址中,放入1;011地址中,放入1;100地址中,放入0;101地址中,放入1;110地址中,放入0;111地址中,放入1;

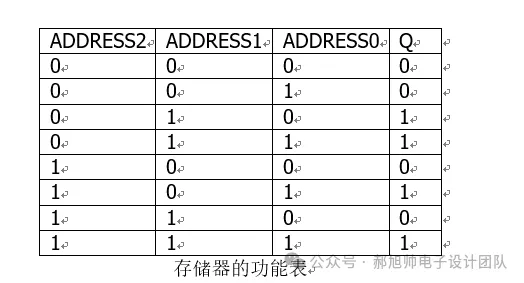

按照我们存储器的逻辑功能,给于地址,存储器就会给出对应地址中所存放的数据。那么存储器的功能表如下:

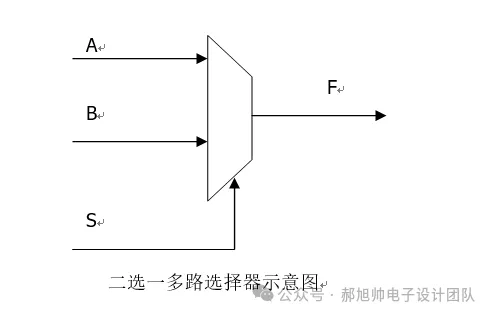

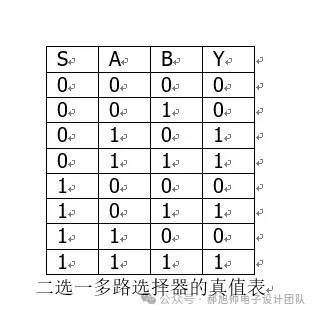

在做设计时,经常会需要一个多路选择器,下面我们以二选一多路选择器为例。

当S=0时,Y=A;当S=1时,Y=B。根据已知功能,列出真值表。

将存储器的功能表和二选一多路选择器的真值表相对比,我们会发现,除了自定义的信号名称不相同外,逻辑功能是相同的。那么也就是说,在黑盒设计时,我们可以将一个带有预设值的存储器放进去,它所对外的功能,也是可以实现二选一多路选择器的。此时,我们可以带有预设值的存储器可以等效为二选一多路选择器。

仔细观察,我们发现,任意真值表都可以用存储器来等效。那也就是说,存储器电路可以等效为任意组合逻辑的电路。

本篇内容中有部分资源来源于网络,如有侵权,请联系作者。

如果您觉得本公众号还不错的话,可以推给身边的朋友们,感谢并祝好!

数字电路中的等效电路和FPGA中的等效电路的更多相关文章

- FPGA中的INOUT接口和高阻态

除了输入输出端口,FPGA中还有另一种端口叫做inout端口.如果需要进行全双工通信,是需要两条信道的,也就是说需要使用两个FPGA管脚和外部器件连接.但是,有时候半双工通信就能满足我们的要求,理论上 ...

- FPGA中竞争冒险问题的研究

什么是竞争冒险? 1 引言 现场可编程门阵列(FPGA)在结构上由逻辑功能块排列为阵列,并由可编程的内部连线连接这些功能块,来实现一定的逻辑功能. FPGA可以替代其他PLD或者各种中小规模数 ...

- FPGA中的delay与latency

delay和latency都有延迟的意义,在FPGA中二者又有具体的区别. latency出现在时序逻辑电路中,表示数据从输入到输出有效经过的时间,通常以时钟周期为单位. delay出现在组合逻辑电路 ...

- FPGA中的时序分析(四)

常用约束语句说明 关于Fmax 上述是实现Fmax的计算公式,clock skew delay的计算如下图, 就是两个时钟的差值.到头来,影响Fmax的值的大小就是组合逻辑,而Fmax是针对 ...

- 【转】关于FPGA中建立时间和保持时间的探讨

时钟是整个电路最重要.最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错:因而明确FPGA设计中决定系统时钟的因素,尽 ...

- FPGA中浮点运算实现方法——定标

有些FPGA中是不能直接对浮点数进行操作的,仅仅能採用定点数进行数值运算.对于FPGA而言,參与数学运算的书就是16位的整型数,但假设数学运算中出现小数怎么办呢?要知道,FPGA对小数是无能为力的,一 ...

- FPGA中改善时序性能的方法_advanced FPGA design

本文内容摘自<advanced FPGA design>对应中文版是 <高级FPGA设计,结构,实现,和优化>第一章中的内容 FPGA中改善时序,我相信也是大家最关心的话题之一 ...

- Altera FPGA中的pin进一步说明

最近END china上的大神阿昏豆发表了博文 <FPGA研发之道(25)-管脚>,刚好今天拿到了新书<深入理解Altera FPGA应用设计>第一章开篇就讲pin.这里就两者 ...

- FPGA中的除法运算及初识AXI总线

FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会.硬件逻辑实现的除法运算会占用较多的资源,电路结构复杂,且通常无法在一个时钟周期内完成.因此FPGA实现除法运算并不是一个&qu ...

- 【转载】FPGA 中的latch 锁存器

以下这篇文章讲述了锁存器的一些概念和注意事项.原文标题及链接: FPGA 中的latch 锁存器 - 快乐至永远上的博客 - 与非博客 - 与网 http://www.eefocus.com/liuy ...

随机推荐

- KDE算法解析

核密度估计(Kernel Density Estimation, KDE)算法通过样本估计这些样本所属的概率密度函数,是non-parametric方法,也就是在进行估计时无需假设分布的具体形式.本文 ...

- verilog设计知识集合

verilog设计知识集合 一.基本知识 verilog HDL,verilog硬件描述语言,可从上层到下层一直设计,使用一些列分层的模块来表示极其复杂的数字系统的语言.利用EDA工具将模块转化为网表 ...

- KingbaseES V8R6 常用的系统函数

查看当前日志文件lsn位置: select sys_current_wal_lsn(); 查看某个lsn对应的日志名: select sys_walfile_name('0/1162FBA0'); 查 ...

- 浅谈JVM整体架构与调优参数

本文分享自华为云社区<[性能优化]JVM整体架构与调优参数说明>,作者: 冰 河. JVM的分类 这里,我们先来说说什么是VM吧,VM的中文含义为:虚拟机,指的是使用软件的方式模拟具有完整 ...

- JDK 14的新特性:switch表达式

目录 简介 写在前面 连写case switch返回值 yield 总结 简介 switch的新特性可是源远流长,早在JDK 12就以预览功能被引入了,最终在JDK 14成为了正式版本的功能:JEP ...

- Java 包和 API 深度解析:组织代码,避免命名冲突

Java 包和 API Java 中的包 用于将相关的类分组在一起.可以将其视为文件目录中的一个文件夹.我们使用包来避免名称冲突,并编写更易于维护的代码. 包分为两类: 内置包(来自 Java API ...

- Bash下切换conda环境

背景:很多时候实验命令都是基于Linux系统的,但是很多人的电脑是window系统的. 使用git自带的Bash可以运行linux命令,不过有时候在bash中想使用conda环境的时候比较麻烦,具体做 ...

- HarmonyOS创作激励计划启动:助力技术创作突破边界

即日起推出HarmonyOS创作激励计划,成功投稿并入选的文章将在HarmonyOS开发者公众号上线,9大技术社区同步宣发,不仅有丰厚稿酬,还有机会赢取创作奖品! 活动时间 即日起-2024年12 ...

- 全局模型可解释之部分依赖图:Partial Dependence Plot

本部分是来自大纲 模型可解释的一个子分支. 部分依赖图可以表示1个或者2个特征对模型的预测结果所能产生的边际效应.同时也能展示1个特征和label直接是否具有:线性相关性.单调性等. 当我们把pdp应 ...

- MMDeploy部署实战系列【第三章】:MMdeploy pytorch模型转换onnx,tensorrt

MMDeploy部署实战系列[第三章]:MMdeploy pytorch模型转换onnx,tensorrt 这个系列是一个随笔,是我走过的一些路,有些地方可能不太完善.如果有那个地方没看懂,评论区问就 ...