基于Verilog的串口发送程序

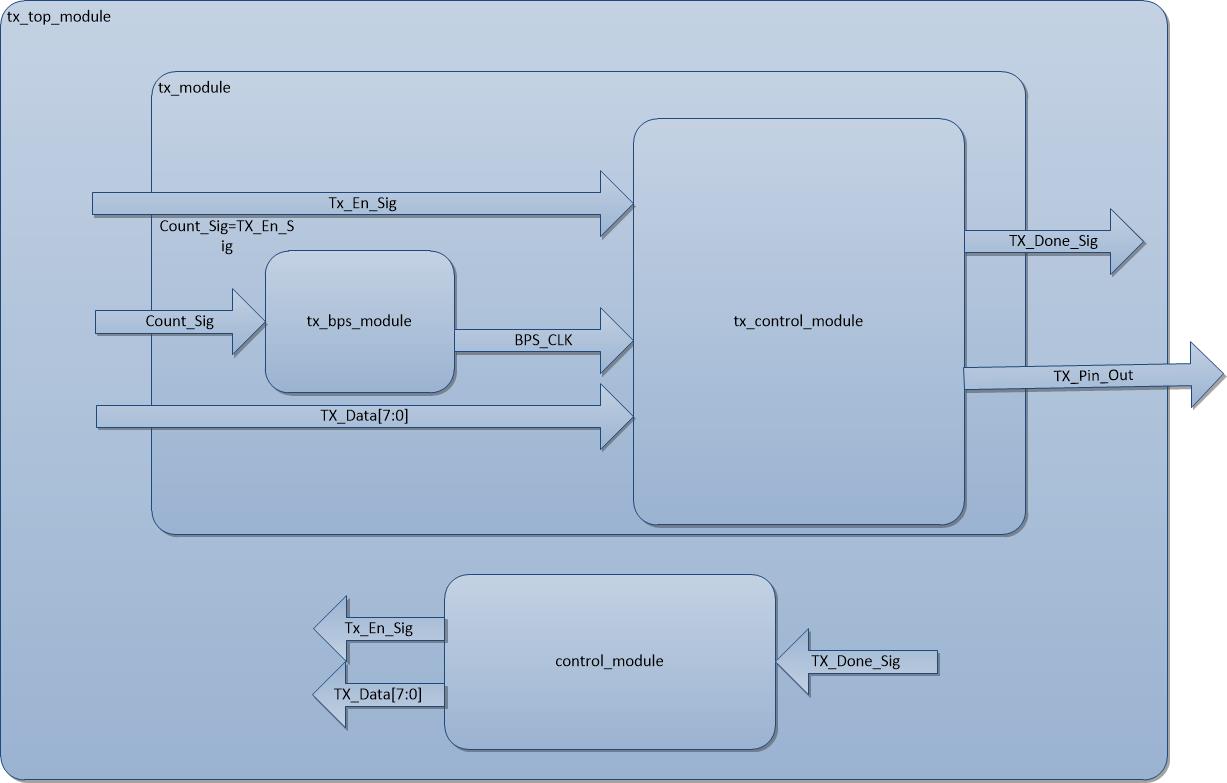

一、模块框图及基本思路

tx_bps_module:波特率时钟产生模块

tx_control_module:串口发送的核心控制模块

tx_module:前两个模块的组合

control_module:发送控制模块,每秒触发一次发送

tx_top_module:tx_module+control_module

二、软件部分

tx_bps_module:

module tx_bps_module #(parameter Baud=)(

CLK,RSTn,

Count_Sig,

BPS_CLK

);

input CLK;

input RSTn;

input Count_Sig;

output BPS_CLK; /***************************/

localparam Baud_Div=50_000_000/Baud-;

localparam Baud_Div2=Baud_Div/; reg[:] Count_BPS;

/*************************/

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

Count_BPS<='d0;

else if(Count_BPS==Baud_Div)

Count_BPS<='d0;

else if(Count_Sig)

Count_BPS<=Count_BPS+;

else Count_BPS<='d0;

end

/************************/

assign BPS_CLK=(Count_BPS==Baud_Div2)?'b1:1'b0;

endmodule

tx_control_module:

module tx_control_module(

CLK,RSTn,

TX_En_Sig,TX_Data,BPS_CLK,

TX_Done_Sig,TX_Pin_Out

);

input CLK,RSTn;

input TX_En_Sig,BPS_CLK;

input [:]TX_Data;

output TX_Done_Sig,TX_Pin_Out;

/***************************************/

reg rTX;

reg isDone;

reg[:] i;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

rTX<='b1;

isDone<='b0;

i<='d0;

end

else if(TX_En_Sig)

begin

case(i)

'd0:if(BPS_CLK) begin rTX<=0;i<=i+1'b1; end

'd1,4'd2,'d3,4'd4,'d5,4'd6,'d7,4'd8:

if(BPS_CLK) begin rTX<=TX_Data[i-];i<=i+'b1; end

'd9:if(BPS_CLK) begin rTX<=1;i<=i+1'b1; end

'd10:if(BPS_CLK) begin rTX<=1;i<=i+1'b1; end

'd11:if(BPS_CLK) begin isDone<=1;i<=i+1'b1; end

'd12: begin isDone<=0;i<=1'b0; end

endcase

end

end

/***************************************/

assign TX_Pin_Out=rTX;

assign TX_Done_Sig=isDone;

endmodule

tx_module:

module tx_module(

CLK,RSTn,

TX_En_Sig,TX_Data,TX_Pin_Out,TX_Done_Sig

);

input CLK;

input RSTn;

input TX_En_Sig;

input [:] TX_Data;

output TX_Pin_Out;

output TX_Done_Sig; wire BPS_CLK; tx_bps_module U0(.CLK(CLK),.RSTn(RSTn),.Count_Sig(TX_En_Sig),.BPS_CLK(BPS_CLK));

tx_control_module U1(.CLK(CLK),.RSTn(RSTn),.TX_En_Sig(TX_En_Sig),

.BPS_CLK(BPS_CLK),.TX_Data(TX_Data),.TX_Done_Sig(TX_Done_Sig),

.TX_Pin_Out(TX_Pin_Out));

endmodule

control_module:

module control_module(

CLK, RSTn,

TX_Done_Sig,

TX_En_Sig, TX_Data

);

input CLK;

input RSTn;

input TX_Done_Sig;

output TX_En_Sig;

output [:]TX_Data; /***********************************************/

localparam T1S='d49_999_99;

reg [:] Count_Sec;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

Count_Sec<='d0;

else if(Count_Sec==T1S) Count_Sec<='d0;

else Count_Sec<=Count_Sec+'b1;

end

/************************************************/ reg[:] rData;

reg isEn;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

rData<='h31;

isEn<='b0;

end

else if(TX_Done_Sig)

begin

rData<='h31;

isEn<='b0;

end

else if(Count_Sec==T1S) isEn<='b1;

end /*************************************************/

assign TX_Data=rData;

assign TX_En_Sig=isEn; /*************************************************/

endmodule

tx_top_module:

module tx_top_module(

CLK,RSTn,

TX_Pin_Out

);

input CLK;

input RSTn;

output TX_Pin_Out; wire TX_Done_Sig;

wire TX_En_Sig;

wire [:]TX_Data;

control_module U0(

.CLK(CLK), .RSTn(RSTn),

.TX_Done_Sig(TX_Done_Sig),

.TX_En_Sig(TX_En_Sig), .TX_Data(TX_Data)); tx_module U1(

.CLK(CLK),.RSTn(RSTn),

.TX_En_Sig(TX_En_Sig),.TX_Data(TX_Data),.TX_Pin_Out(TX_Pin_Out),.TX_Done_Sig(TX_Done_Sig)

);

endmodule

三、硬件部分

黑金SPARTAN开发板

NET "CLK" LOC = T8;

NET "RSTn" LOC = L3;

NET "TX_Pin_Out" LOC = D12;

基于Verilog的串口发送程序的更多相关文章

- 基于Verilog的串口接收程序

一.模块框图及基本思路 detect_module:检测输入引脚的下降沿,以此判断一帧数据的开始 rx_bps_module:波特率时钟产生模块 rx_control_module:串口接收的核心控制 ...

- 基于Verilog的带FIFO写入缓冲的串口发送接口封装

一.模块框图及基本思路 tx_module:串口发送的核心模块,详细介绍请参照前面的“基于Verilog的串口发送实验” fifo2tx_module:当fifo不为空时,读取fifo中的数据并使能发 ...

- 纠错:基于FPGA串口发送彩色图片数据至VGA显示

今天这篇文章是要修改之前的一个错误,前面我写过一篇基于FPGA的串口发送图片数据至VGA显示的文章,最后是显示成功了,但是显示的效果图,看起来确实灰度图,当时我默认我使用的MATLAB代码将图片数据转 ...

- 基于Verilog的带FIFO输出缓冲的串口接收接口封装

一.模块框图及基本思路 rx_module:串口接收的核心模块,详细介绍请见“基于Verilog的串口接收实验” rx2fifo_module:rx_module与rx_fifo之间的控制模块,其功能 ...

- C#中缓存的使用 ajax请求基于restFul的WebApi(post、get、delete、put) 让 .NET 更方便的导入导出 Excel .net core api +swagger(一个简单的入门demo 使用codefirst+mysql) C# 位运算详解 c# 交错数组 c# 数组协变 C# 添加Excel表单控件(Form Controls) C#串口通信程序

C#中缓存的使用 缓存的概念及优缺点在这里就不多做介绍,主要介绍一下使用的方法. 1.在ASP.NET中页面缓存的使用方法简单,只需要在aspx页的顶部加上一句声明即可: <%@ Outp ...

- 串口发送端verilog代码分析

串口发送端verilog代码分析 `timescale 1ns / 1ps ////////////////////////////////////////////////////////////// ...

- 基于STM32F10x的串口(USART)输入输出编程

1 前言 STM32有强大的固件库,绝大部分函数都可以有库里面的函数组合编写.固件库可以到ST官网(www.st.com)上下载,也可以搜索“STM32 固件库 v3.5”下载到固件库.本文章就是基于 ...

- C语言实验单片机串口发送int型数据

void SendIint(int n)reentrant { unsigned char s; while(n!=0) { s=(unsigned char)n%10+48; SendByte(s) ...

- 【小梅哥FPGA进阶教程】串口发送图片数据到SRAM在TFT屏上显示

十五.串口发送图片数据到SRAM在TFT屏上显示 之前分享过rom存储图片数据在TFT屏上显示,该方法只能显示小点的图片,如果想显示TFT屏幕大小的图片上述方法rom内存大小不够.小梅哥给了个方案,利 ...

随机推荐

- 【题解】Luogu P3287 [SCOI2014]方伯伯的玉米田

原题传送门 一眼就能看出来这是一道dp题 显而易见每次操作的右端点一定是n,每株玉米被拔高的次数随位置不下降 用f(i,j) 表示以第i 株玉米结尾它被拔高了j 次的最长序列长度. \(f(i,j)= ...

- 修改mongodb(带仲裁节点的副本集)各机器端口

需求:因为端口调整,需要改变副本的备份集 1.查看当前的副本集信息 [root@localhost bin]# ./mongo 192.168.1.134:10001 repltest:PRIMARY ...

- JS设计模式(1)单例模式

什么是单例模式 定义:1.只有一个实例.2.可以全局访问 主要解决:一个全局使用的类频繁地创建与销毁. 何时使用:当您想控制实例数目,节省系统资源的时候. 如何解决:判断系统是否已经有这个单例,如果有 ...

- 小技巧:windows软件窗口键盘移动

alt+tab alt+空格 m键,上下左右操作

- Learning-Python【15】:内置函数

截止到Python版本3.6.2,一共为我们提供了68个内置函数.它们就是Python提供的直接可以拿来使用的所有函数. 这个表的顺序是按照首字母的排列顺序来的,都混乱的堆在一起.比如,oct和bin ...

- centos7中安装python3.7遇到的问题

安装python3.7的步骤 wget https://www.python.org/ftp/python/3.7.3/Python-3.7.3.tar.xz yum install -y gcc ...

- SecureCRT自动断开

解决方法 可以通过两个入口进行设置: 1.右击Session中的连接,选择Properties->Terminal->Anti-idle->勾选Send protocol NO-OP ...

- 20190318wdVBA_替换下划线

Sub 替换下划线() Selection.HomeKey wdStory Selection.Find.ClearFormatting Selection.Find.Font.Underline = ...

- 了解FPGA市场现状和未来趋势

转, 来源: http://www.sohu.com/a/204640373_740053 可编程的“万能芯片” FPGA——现场可编程门阵列,是指一切通过软件手段更改.配置器件内部连接结构和逻辑单元 ...

- VUE环境搭建、创建项目、vue调试工具

环境搭建 第一步 安装node.js 打开下载链接: https://nodejs.org/en/download/ 这里下载的是node-v6.9.2-x64.msi; 默认式的安装,默认 ...