zc702-自定义AXI-IP核实验

目的:

自定义一个IP核,通过AXI总线与ARM系统连接

环境:

Win7 32bit

Vivado2014.4.1

Xilinx sdk2014.4

开发板:

Zc702

第一步:

新建一个自定义的HDL模块,本实验新建一个16位加法器,保存为test.v,代码如下

module test(

input [15:0] a,

input [15:0] b,

input clk,

output reg [15:0] sum

);

always@(posedge clk)

begin

sum <= a +b ;

end

endmodule

第二步:

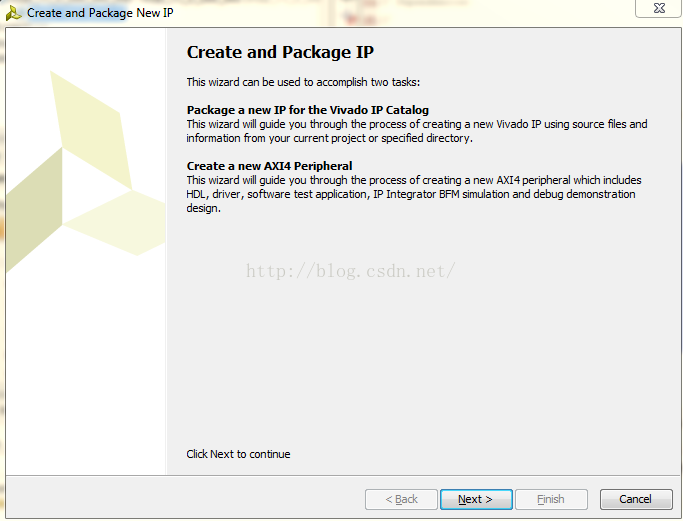

新建一个IP核,打开vivado,在tools中选中新建IP核

点击Next,

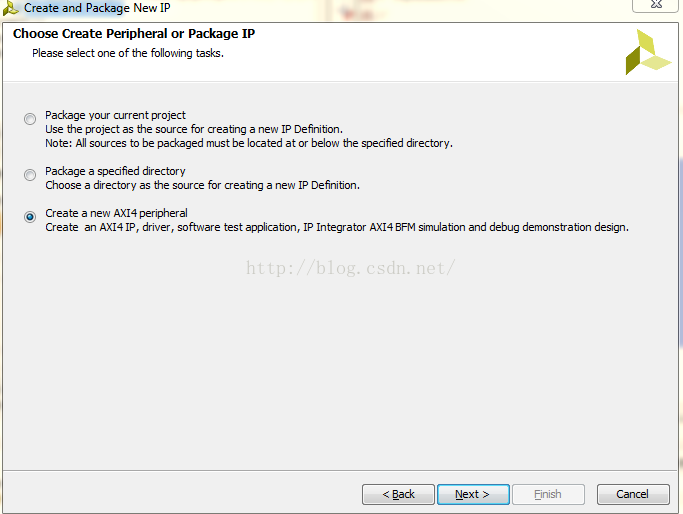

选中新建AXI外设选项,

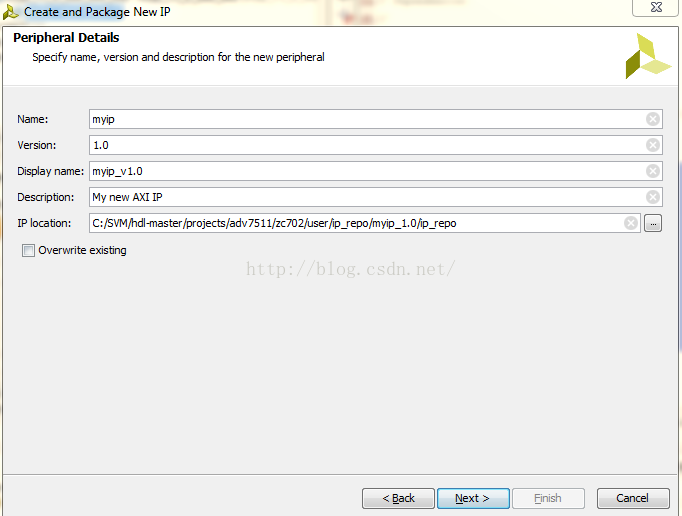

填好信息,点击next,

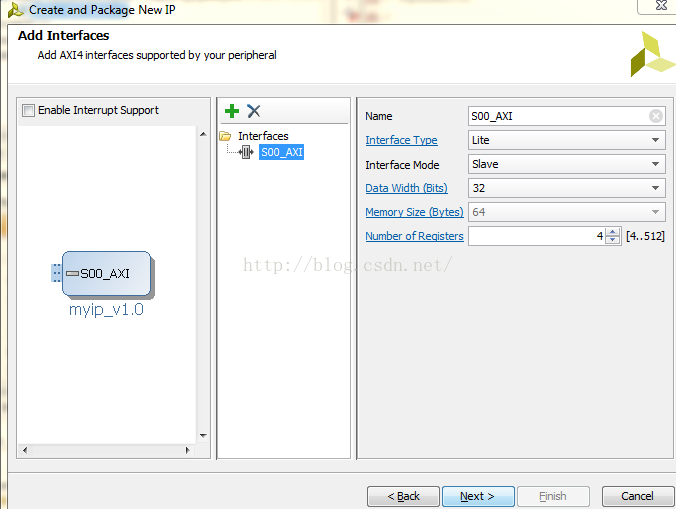

填好参数,这里就用默认的即可,

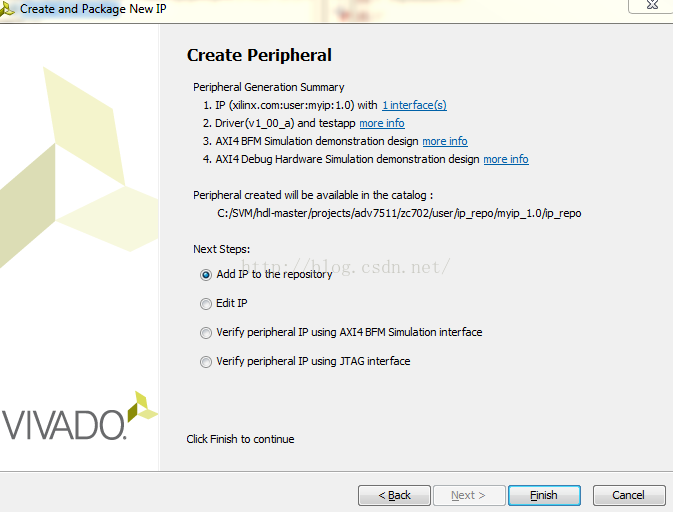

然后点击finish。

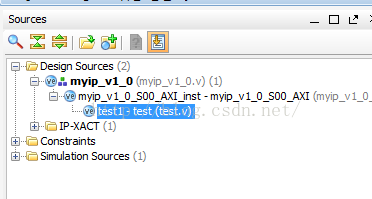

之后会打开一个这个新建的IP核工程,查看

新建的时候是没有test.v加入到工程的,双击myip_v1_0_AXI_inst-myip_v1_0_S00_AXI.v

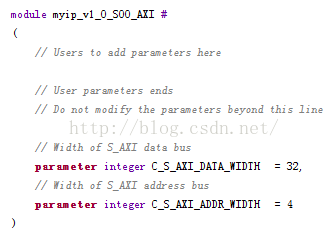

上面这段代码,主要就是定义了使用的参数,也是我们在新建IP核预先设置的参数,数据宽32位,地址宽4位;

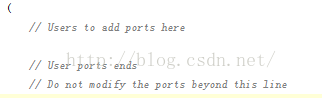

在参数设置之后,这段注释就是让用户可以添加需要的端口了,在本次实验中是不需要添加的;

看接下来的程序:

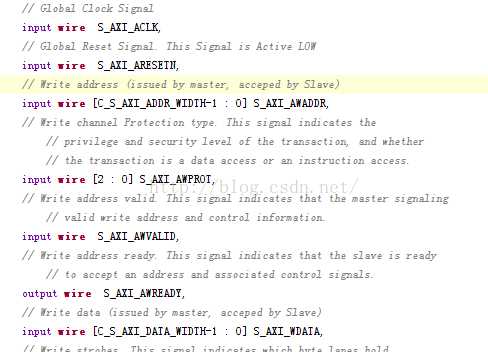

系统默认的第一个输入端口S_AXI_ACLK为时钟,然后S_AXI_ARESETN是复位;

接下来S_AXI_AWADDR是写地址,后面暂略,

从注释就可以看到是安全级别的选项,这个是AXI的标准后续再谈;

还有一个端口S_AXI_WDATA就是写入的数据;

部分端口这里就不说明了,可以直接看注释,直接看马上用到的几个端口:

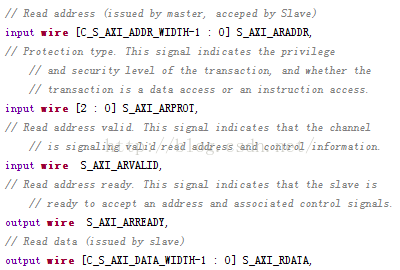

S_AXI_ARADDR是读IP核的地址,S_AXI_RDATA是被读的寄存器;

接下来看

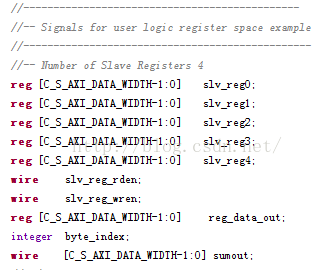

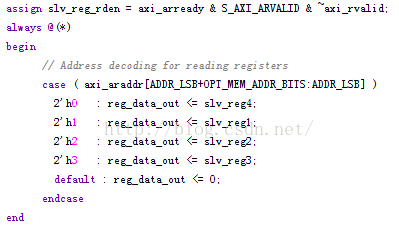

新建的时候会看到4个slv_reg寄存器,实验中又添加了一个

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg4;

又添加了一条:

wire [C_S_AXI_DATA_WIDTH-1:0] sumout;

主要是为了把test.v这个模块添加进来;

这几个寄存器在

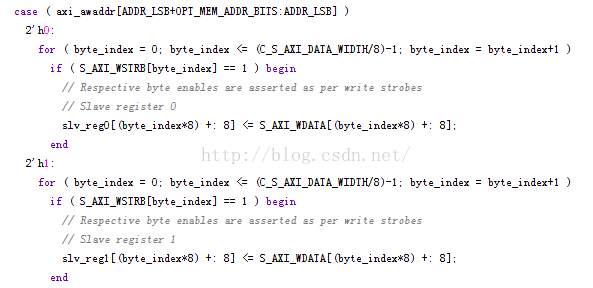

这几条代码显示,在往自定义的IP核内写数据是会将数据写到刚才定义的几个寄存器内的,当然这些寄存器用户都是可以自己改的,这个实验就不更改了;

那么,用户是往哪一个地址写数据呢?那么看这里:

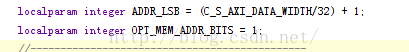

根据上面的定义,

ADDR_LSB=2,OPT_MEM_ADDR_BITS =1;

也就是往地址段axi_awaddr[3:2]部分写的话就会将数据写入这4个寄存器,同理在读数据的时候也是,具体看代码即可。

前面看到是用户写数据及其IP核接收到的数据寄存器,下面是IP核的输出数据,也就是用户在读IP核时被读的寄存器:

这里在实验中,做了一些更改,将slv_reg0,变为了slv_reg4;

最后在用户逻辑部分,添加例化的模块。

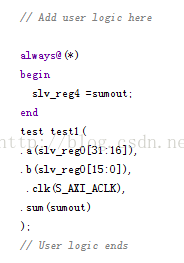

然后

到这界面之后,查看左侧的检查选项是否都已经打勾,没打勾的话选中哪一个选项做一些简单确认即可完成,最后打包IP核,保存为zip的格式。

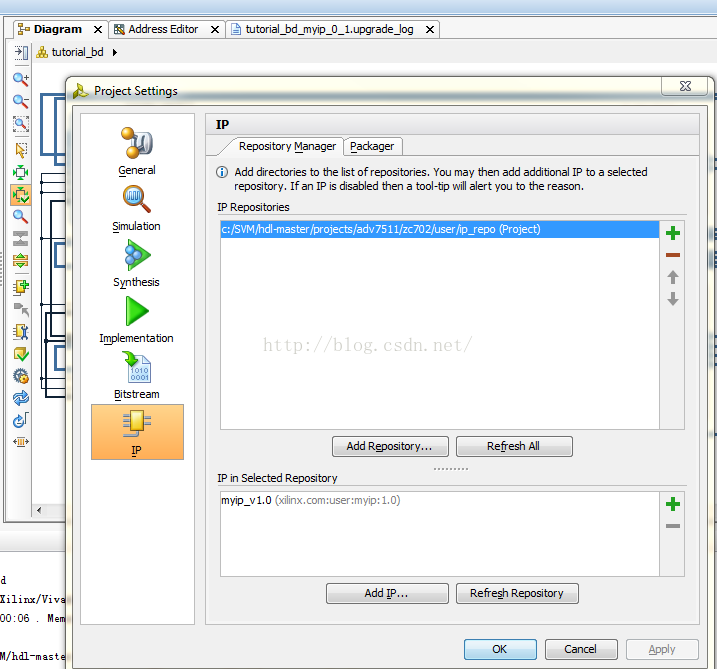

将IP核工程关闭,新建一个系统文件或者打开一个example工程,在工程内添加新建的ip核,当然需要将新建的ip核包含在工程内,如图:

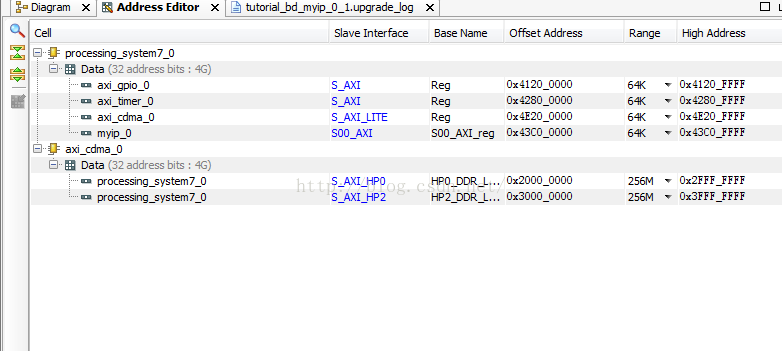

在工程内添加自己的IP之后,自动分配一下地址:

然后确认无误,,生成bitstream。

稍等片刻之后,没有报错,然后export hardware,之后再launch SDk,

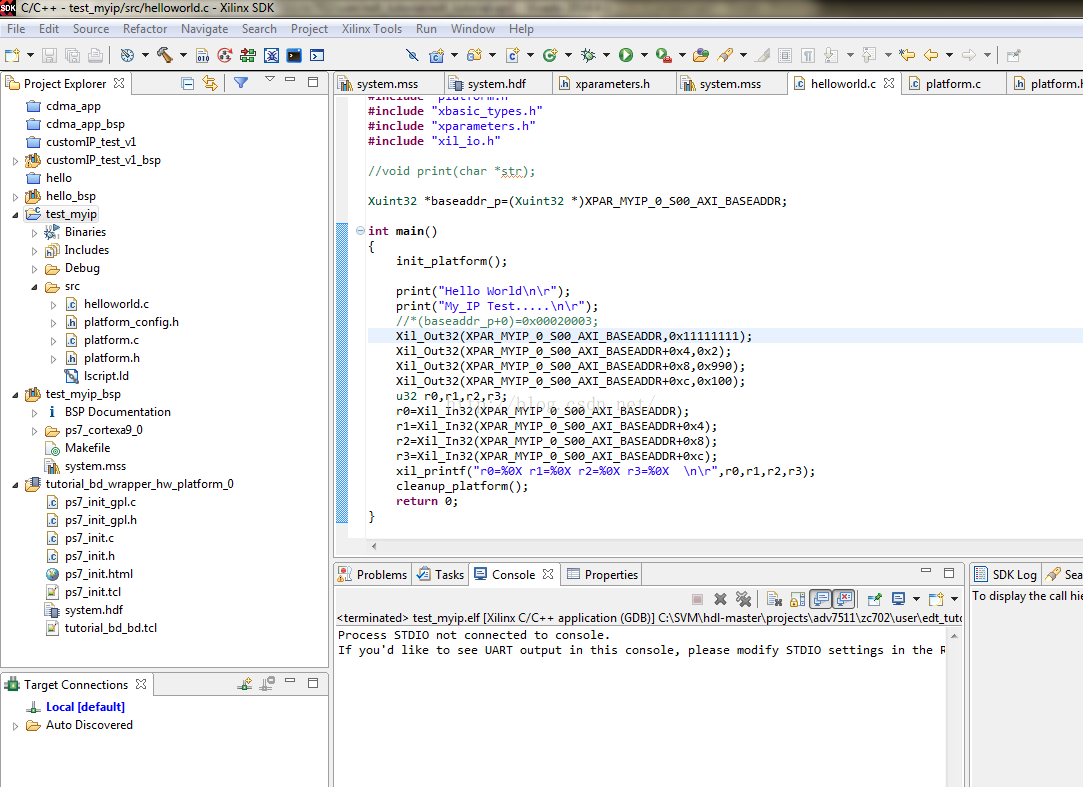

打开SDK后,需要新建一个application,

用最简单的helloworld工程样板即可,然后修改代码:

#include <stdio.h>

#include "platform.h"

#include "xbasic_types.h"

#include "xparameters.h"

#include "xil_io.h"

Xuint32*baseaddr_p=(Xuint32*)XPAR_MYIP_0_S00_AXI_BASEADDR;

int main()

{

init_platform();

print("Hello World\n\r");

print("My_IP Test.....\n\r");

//*(baseaddr_p+0)=0x00020003;

Xil_Out32(XPAR_MYIP_0_S00_AXI_BASEADDR,0x11111111);

Xil_Out32(XPAR_MYIP_0_S00_AXI_BASEADDR+0x4,0x2);

Xil_Out32(XPAR_MYIP_0_S00_AXI_BASEADDR+0x8,0x990);

Xil_Out32(XPAR_MYIP_0_S00_AXI_BASEADDR+0xc,0x100);

u32r0,r1,r2,r3;

r0=Xil_In32(XPAR_MYIP_0_S00_AXI_BASEADDR);

r1=Xil_In32(XPAR_MYIP_0_S00_AXI_BASEADDR+0x4);

r2=Xil_In32(XPAR_MYIP_0_S00_AXI_BASEADDR+0x8);

r3=Xil_In32(XPAR_MYIP_0_S00_AXI_BASEADDR+0xc);

xil_printf("r0=%0X r1=%0X r2=%0Xr3=%0X \n\r",r0,r1,r2,r3);

cleanup_platform();

return0;

}

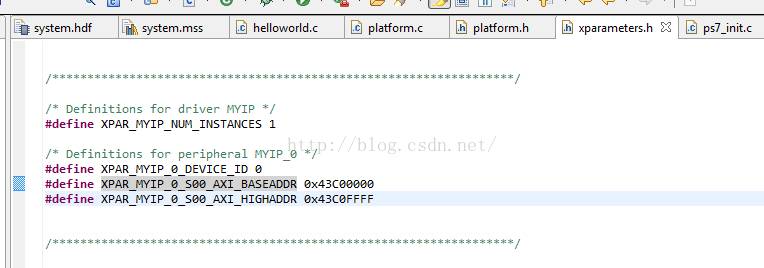

添加的xparameters.h头文件包含了自定义的IP的系统地址:

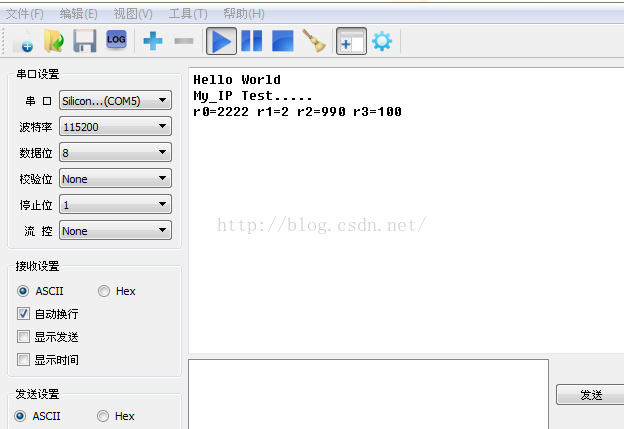

编译之后,先将bit文件下载到fpga,然后run,看到

好了,实验结束。

转载:https://blog.csdn.net/shushm/article/details/49536845

zc702-自定义AXI-IP核实验的更多相关文章

- ZYNQ自定义AXI总线IP应用——PWM实现呼吸灯效果

一.前言 在实时性要求较高的场合中,CPU软件执行的方式显然不能满足需求,这时需要硬件逻辑实现部分功能.要想使自定义IP核被CPU访问,就必须带有总线接口.ZYNQ采用AXI BUS实现PS和PL之间 ...

- vagrant public_network 自定义静态 ip配置方法

Vagrant 创建虚拟化开发环境 Vagrant是一个基于Ruby的工具,用于创建和部署虚拟化开发环境.它 使用Oracle的开源VirtualBox虚拟化系统,使用 Chef创建自动化虚拟环境. ...

- 自定义AXI总线形式SPI接口IP核,点亮OLED

一.前言 最近花费很多精力在算法仿真和实现上,外设接口的调试略有生疏.本文以FPGA控制OLED中的SPI接口为例,重新夯实下基础.重点内容为SPI时序的RTL设计以及AXI-Lite总线分析.当然做 ...

- 自定义电脑IP地址

一台电脑有了ip地址才能上网,ip就是电脑的标识,在互联网中就是其中的一份子. 默认情况下电脑会自动获取IP地址,当无法自动获取或与网络IP地址相冲突时,就要自行设置电脑静态IP地址. 如下图步骤:

- ZYNQ笔记(7):AXI从口自定义IP封装

使用 AXI_Lite 从口实现寄存器列表的读写,并且自己封装为一个自定义 IP,以便以后使用.本次记录的是 M_AXI_GP0 接口,此接口是 ARM 作为主机,FPGA 作为从机,配置 FPGA ...

- 一步一步学ZedBoard & Zynq(四):基于AXI Lite 总线的从设备IP设计

本帖最后由 xinxincaijq 于 2013-1-9 10:27 编辑 一步一步学ZedBoard & Zynq(四):基于AXI Lite 总线的从设备IP设计 转自博客:http:// ...

- vivado设计四:自定义IP核测试

在vivado设计三中:http://blog.chinaaet.com/detail/37177已经建立了vivado工程和封装好了自定义IP核. 那么接下来,我们对这个自定义IP核进行测试了:我们 ...

- 第三章 VIVADO 自定义IP 流水灯实验

第二章里面已经说过了,MIZ701 PL部分没有输入时钟,因此驱动PL资源必须是通过PS来提供时钟,所以这个流水灯实验也得建立一个最小系统了,然后再添加一个流水灯的自定义IP. 3.0本章难度系数★★ ...

- WinBox软路由的自定义IP设定

软路由ros(MIKRTIK)安装简单步骤 由于本主也是刚刚接触软路由这个硬件方面的知识.所以也是略知皮毛而已,今天通过网上的学习,然后自己总结了一下怎么在软路由中设定一个自定义IP ...

随机推荐

- 自定义Map.Entry的Comperator实现字符频率降序排序

leetCode (#451,middle) java实现 class Solution { public String frequencySort(String s) { Map<Charac ...

- STRING DELIMITED BY SIZE

The following COBOL program depicts the use of STRING DELIMITED BY SIZE IDENTIFICAT ...

- oracle 重复只保留一条

DELETE FROM xx WHERE ROWID NOT IN (SELECT MIN(ROWID) FROM xx GROUP BY xx, xx);

- Oracle FM FM09999999 确保8位数字 即使全是0

Select TO_CHAR(12.123,'0999.999'),TO_CHAR(123,'FM09999999') FROM DUAL; TO_CHAR(12.123,'0999.999') TO ...

- UVA 2519 Radar Installtion

思路: #include<cstdio> #include<iostream> #include<cmath> #include<algorithm> ...

- spring boot + jpa + bootstrap + thymeleaf 简单的增删改查Demo

对springboot和bootstrap初学者来说是一个不错Demo 下载地址:点击进入下载Demo 首页(http://localhost:8081) 增加 编辑 搜索

- h5中input的request属性提示文字字段

<input type="password" class="form-control" name="passWord" require ...

- unique_ptr_c++11

unique_ptr 替代了原来的auto_ptr,指向对象具有唯一性,即同一时间只能有unique_ptr指向给定对象(和auto_ptr不同是禁止拷贝语义,通过移动语义替代) unique_ptr ...

- db2 merge update

DB2 Merge 语句的作用非常强大,它可以将一个表中的数据合并到另一个表中,在合并的同时可以进行插入.删除.更新等操作.我们还是先来看个简单的例子吧,假设你定义了一个雇员表(employe),一个 ...

- JS_高程7.函数表达式(2)递归

递归函数:一个函数通过名字调用自身的情况构成的.eg: //递归实现阶乘 function factorial(num){ if(num <= 1){ return 1; }else{ retu ...