HDLbits——Lfsr5

Build this LFSR. The reset should reset the LFSR to 1

module top_module(

input clk,

input reset, // Active-high synchronous reset to 5'h1

output reg [4:0] q

);

always @(posedge clk) begin

if(reset==1'b1)begin

q <= 5'h1;

end

else begin

q <= {0^q[0],q[4],q[3]^q[0],q[2:1]};

end

end

endmodule

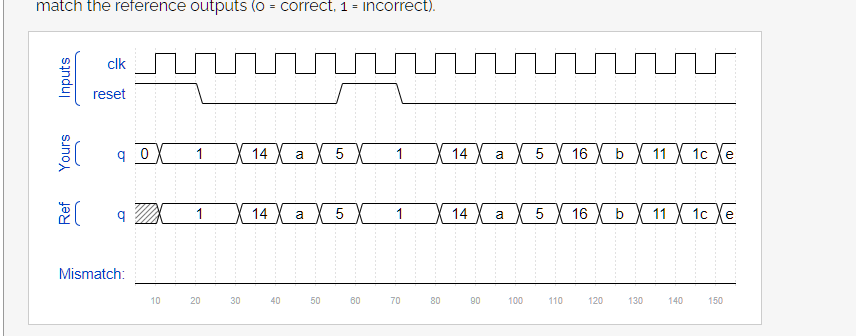

测试波形

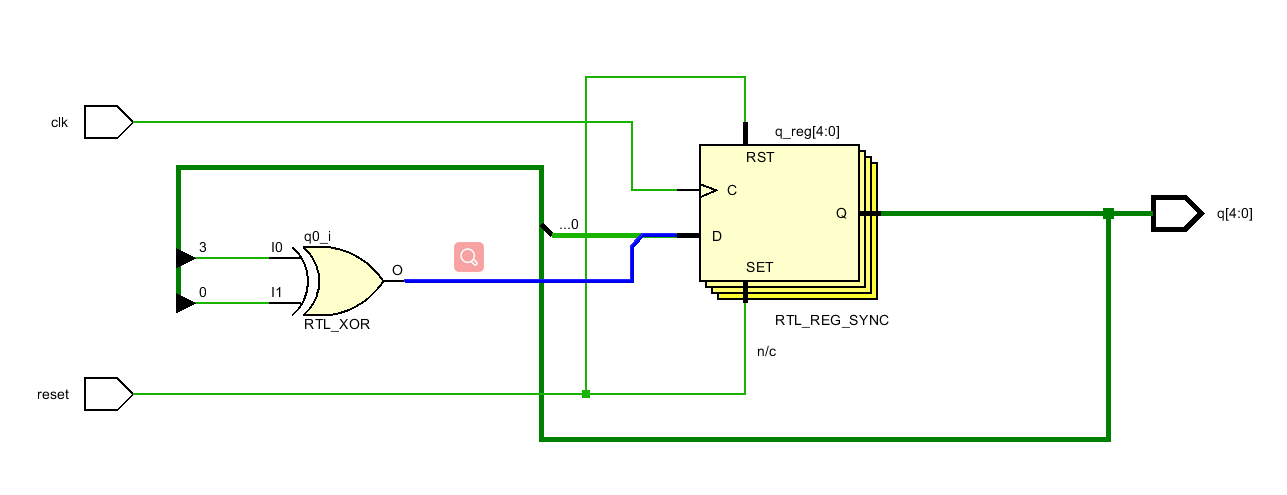

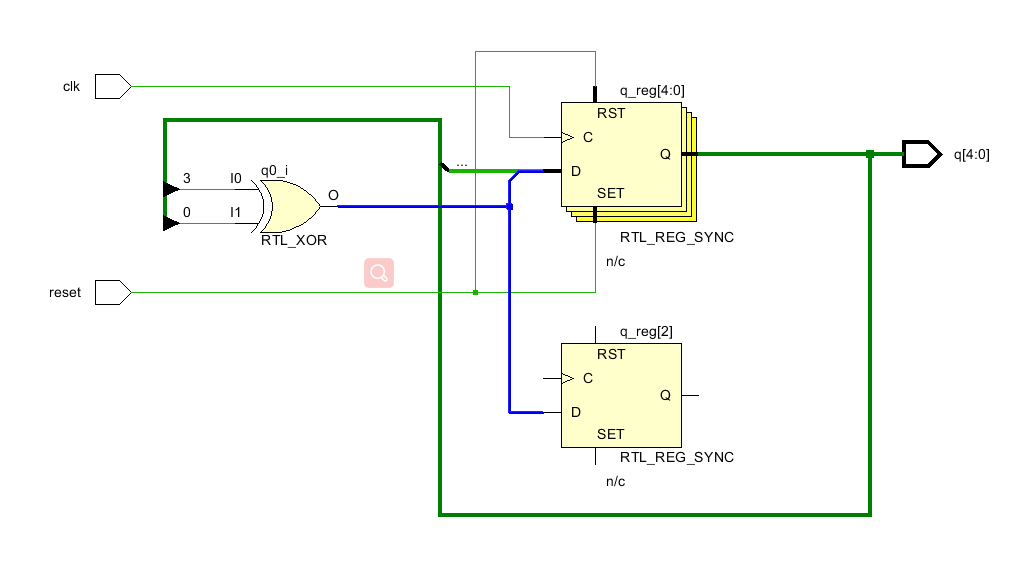

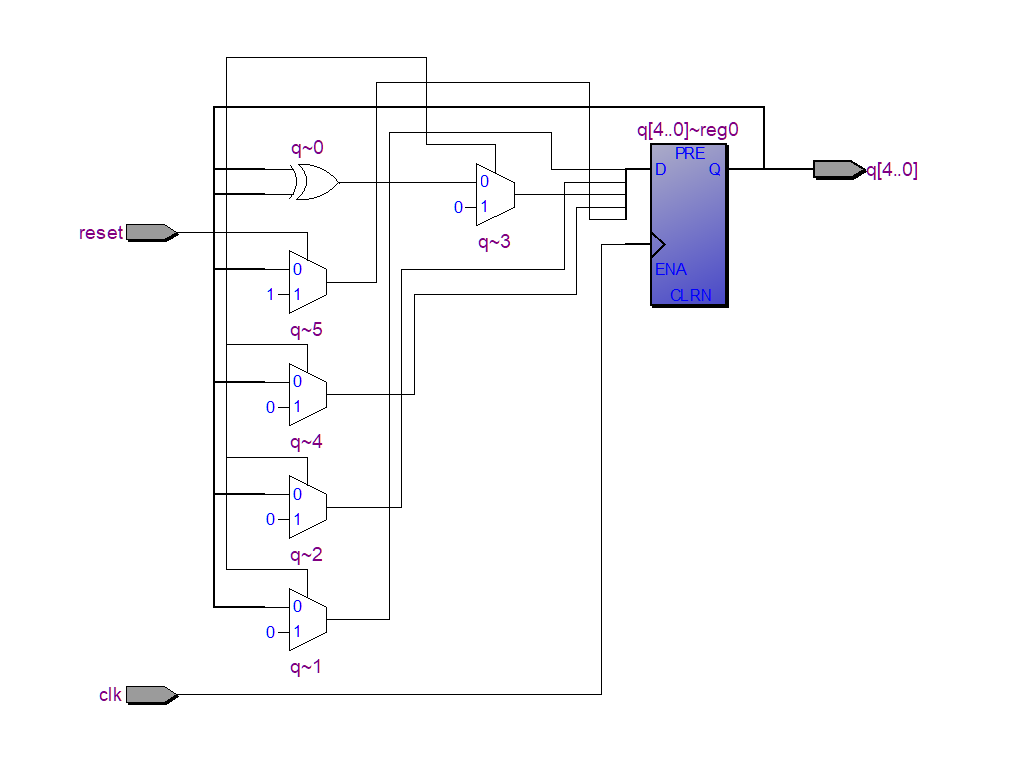

原理图:

HDLbits——Lfsr5的更多相关文章

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- HDLBits答案——Circuits

1 Combinational Logic 1.1 Basic Gates 1.1.1 Exams/m2014 q4h module top_module ( input in, output out ...

- HDLBits答案——Verification: Writing Testbenches

1 clock module top_module ( ); reg clk; dut U1(.clk(clk)); initial begin clk = 0; end always begin # ...

- HDLBits答案——Verification: Reading Simulations

1 Finding bugs in code 1.1 Bugs mux2 module top_module ( input sel, input [7:0] a, input [7:0] b, ou ...

- HDLBits答案——Verilog Language

Verilog Language 1 Basics 1.1 Wire module top_module( input in, output out ); assign out = in; endmo ...

- HDLBits答案——Getting started

Getting started 1 Step one module top_module( output one ); // Insert your code here assign one = 1' ...

- verilog常见错误列表

Error/Warning 来源:https://hdlbits.01xz.net/wiki/ 题目: 1.Quartus Warning 10235: Warning (): Verilog HDL ...

- Verilog HDL

https://wenku.baidu.com/view/9943b7acf524ccbff1218463.html https://hdlbits.01xz.net/wiki/Main_Page h ...

- Verilog设计技巧实例及实现

Verilog设计技巧实例及实现 1 引言 最近在刷HDLBits的过程中学习了一些Verilog的设计技巧,在这里予以整理.部分操作可能降低代码的可读性和Debug的难度,请大家根据实际情况进行使用 ...

- 入行数字IC验证的一些建议

0x00 首先,推荐你看两本书,<"胡"说IC菜鸟工程师完美进阶>(pdf版本就行)本书介绍整个流程都有哪些岗位,充分了解IC行业的职业发展方向.<SoC设计方法 ...

随机推荐

- SAP 采购订单行项目客制化字段增强

需求: 在采购订单行项目中新增客制化字段,区分采购的项目中的物料是量产还是研发物料 开发步骤 主要使用二代增强出口:MM06E005 创建增强项目 事务码T-code:CMOD 创建项目ZEMM001 ...

- VUE学习-优化过渡

过渡(优化) 可复用的过渡 <transition> 或者 <transition-group>为根的组件 Vue.component('my-special-transiti ...

- python 链接云端数据库/远程数据库 可以使用原始Odbc

class MySqlOdbc: def __init__(self): self.sqlhead = None # 当前数据链接句柄 self.mycursor = None # 当前游标 &quo ...

- hexo-theme-tree

Hexo 主题 Tree 一个简洁的主题,主要功能是 "树状导航" + "树状目录",可选配"评论"和"阅读量"功能,支 ...

- 关于java业务限流组件的应用推广

可参考的链接如下: 限流算法对比.网关限流实践总结(https://segmentfault.com/a/1190000020745218) 高并发下常见的限流算法(https://www.jians ...

- scrollIntoView()方法将元素滚动到浏览器窗口的可见区域

TIPS:容器可滚动时才有用! 语法 element.scrollIntoView(); // 等同于element.scrollIntoView(true) element.scrollIntoVi ...

- redis-creating server tcp listening socket 127.0.0.1:6379: bind No error

安装redis,出现如下错误: 解决方法: 步骤1:命令行下输入:redis-cli.exe(注意不是redis-server.exe) 然后输入:shutdown exit 退出后输入.\redis ...

- windows 系统进行升级之后,如何删除 Windows.old 文件夹。

首先用鼠标右键点击 C 盘,在弹出的下拉列表里找到"属性"并点击它. 步骤阅读 2 在打开的 C 盘属性里的常规找到"磁盘清理",点击它打开. 步骤阅读 3 这 ...

- Java基础学习:8、构造器(构造方法)和this

一.构造器: 1.定义:构造器是类的特殊方法,它的主要作用是完成对象的初始化. 即在创建对象时初始化对象. 本质是方法. 2.特点: a.方法名和类名一致. b.无返回值. c. ...

- grep的正则匹配使用方式

grep正则匹配的命令方式如下 $ grep 'pattern1\|pattern2' filename 或 $ grep -E 'pattern1|pattern2' file grep默认是区分大 ...