FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习,将感悟记于此,如有错误,欢迎指出、讨论。

一、关于时钟引脚

FPGA芯片一般有好几组时钟引脚 CLK [0..N] [p,n],我的理解是:首先,时钟必须由外部晶振通过CLK引脚输入到FPGA的时钟网络,至于选用哪一组CLK,主要看FPGA哪个bank对时钟要求最为苛刻;其次,一般用p端,n端由quartus置位三态;再次,对于简单的系统,只有一组CLK输入作为系统主时钟,其他时钟引脚空置,或者作为某些高带载能力的时钟的输出口(是否可作为输出口,要看芯片手册);然后,复杂系统,可以有不同源的时钟分别从不同CLK引脚输入,只是猜想,没实践过,个人认为这样不好,因为FPGA的核心就是同步;另外,不要把CLK引脚和全局时钟、区域时钟什么的混为一谈,一个是时钟输入引脚,一个是内部时钟走线;最后,CLK引脚进去的走线肯定进过优化的(H型铜皮,专用的、直达每个触发器的布线资源),所以能做到小的抖动和偏斜,带载能力

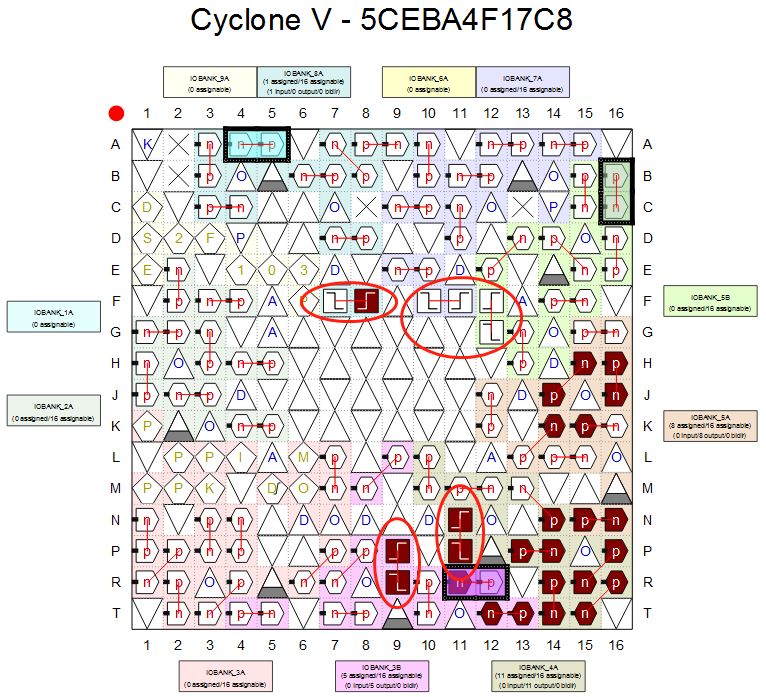

图1

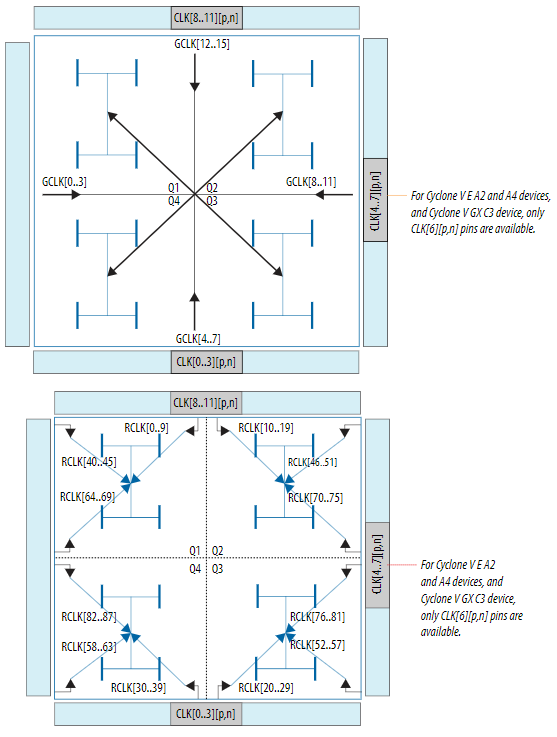

图2

图1所示:红圈为时钟输入引脚,当然,从时钟引脚输入的时钟必定首先进入全局时钟网络,再进一步驱动区域时钟,或者由PLL进行分/倍频==;三个黑色方框内PLL输出引脚,我的理解是:这几组引脚的布线也经过了优化,可以使PLL分/倍频后输出的时钟信号质量较好。

图2所示:CLK9p作为系统唯一的外部输入时钟源,图3

图4

******注意******

- 常规操作:外部晶振—>时钟引脚—>PLL—>区域时钟、各个模块、输出(待验证和完善,我也迷)。

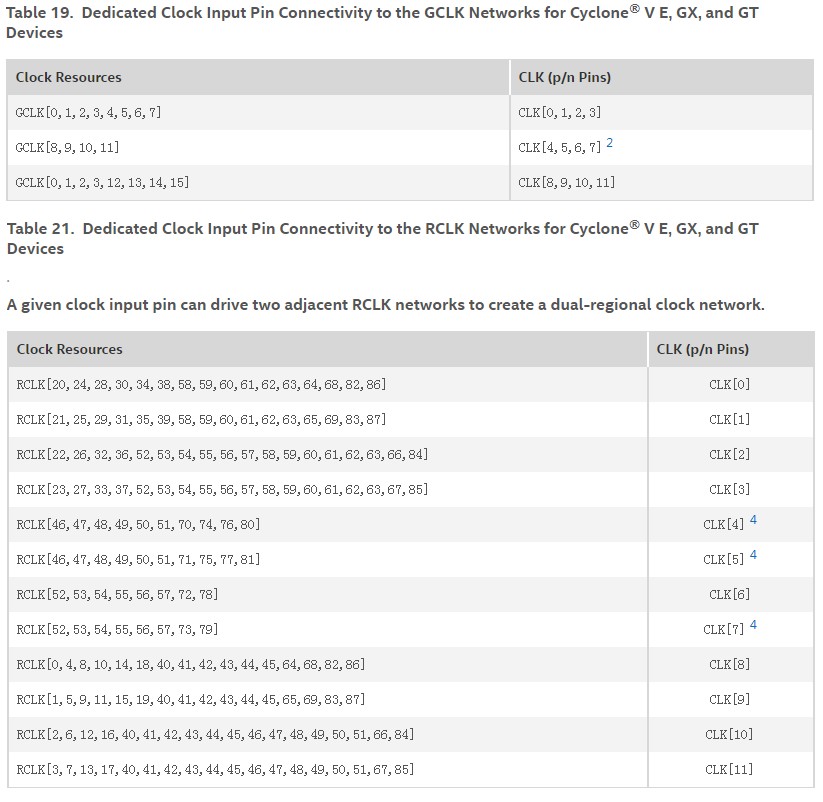

- 关于CLK引脚选择:不是所有的CLK引脚都可以连接到所有的全局/区域时钟网路,见图5。

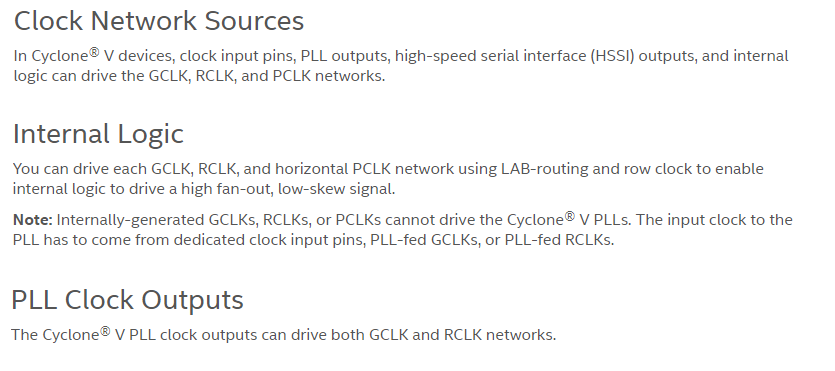

- 关于PLL:不是所有始终都可以驱动PLL,详见手册,如图6所示。

图5

图6

三、时钟资源的使用、分配

20181101提出

- 疑问:编写逻辑电路,或者布局布线时,我怎么知道某个时钟具体使用了哪种、哪个网络?以及怎么人为地控制使用具体某个网络?

20181102补充

- 除非是时钟资源(尤其是全局时钟资源)紧张,或者需要进行时序优化,否则,一般不用过于关心这些资源怎么使用的,quartus会根据电路逻辑,自动选择最优的布局布线。

- 实际上,根据硬件电路和逻辑电路,也能推断出用了多少全局时钟、区域时钟。

- 比如:clk0=50MHz,然后它在几个always中都被用到,而这几个always占用的逻辑资源分布在不同的区域,那么这个时钟应该是全局时钟;再比如:clk1=100MHz,它只在一个always里被使用,或使用它的逻辑资源都在一个区域,那么clk1应该是区域时钟。

- https://www.cnblogs.com/zuilangsanshu/

FPGA系列之一:Cyclone V中的时钟资源的更多相关文章

- 三叔学FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

- 三叔学FPGA系列之二:Cyclone V中的POR、配置、初始化,以及复位

对于FPGA内部的复位,之前一直比较迷,这两天仔细研究官方数据手册,解开了心中的诸多疑惑,感觉自己又进步了呢..... 原创不易,转载请转原文,注明出处,谢谢. 一.关于POR(Power-On ...

- FPGA开发时钟资源评估需要考虑的问题

在第一个独立开发的FPGA项目中,使用了Altera平台的三速以太网IP,工作在100M模式下,外部输入的PHY时钟频率为25MHz. 由于在前期没有注意这个外部输入的时钟,导致最后不得不在板子上飞线 ...

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- Xilinx Altera FPGA中的逻辑资源(Slices VS LE)比较

前言 经常有朋友会问我,“我这个方案是用A家的FPGA还是X家的FPGA呢?他们的容量够不够呢?他们的容量怎么比较呢?”当然,在大部分时候,我在给客户做设计的时候,直接会用到最高容量的产品,因为我们的 ...

- 友晶Altera Cyclone V GX Starter Kit开发板使用ADC-第一篇

1. 拿到板子在,做工很好,属于GX系列,GX应该是高速收发器 2. 去探究下GX是什么用途,大约有6个型号,这个板子是5CGXFX5,有77 LE逻辑单元,这个收发器不知道是什么?6个 3.125G ...

- Xilinx FPGA全局时钟和全局时钟资源的使用方法

对FPGA的全局时钟了解不多,遂转载一篇文档: http://xilinx.eetop.cn/?action-viewnews-itemid-42 目前,大型设计一般推荐使用同步时序电路.同步时序电路 ...

- SSE 系列内置函数中的 shuffle 函数

SSE 系列内置函数中的 shuffle 函数 邮箱: quarrying@qq.com 博客: http://www.cnblogs.com/quarryman/ 发布时间: 2017年04月18日 ...

- Spartan6系列之Spartan6系列之芯片时钟资源深入详解

1. 时钟资源概述 时钟设施提供了一系列的低电容.低抖动的互联线,这些互联线非常适合于传输高频信号.最大量减小时钟抖动.这些连线资源可以和DCM.PLL等实现连接. 每一种Spartan-6芯片提 ...

随机推荐

- python 全栈开发,Day120(路由系统, 实例化Flask的参数, 蓝图(BluePrint), before_request after_request)

昨日内容回顾 1.Flask: from flask import Flask app = Flask(__name__) # 从源码中可以看出,Flask集成的run方法是由werkzeug中的ru ...

- oracle查询出来的时间吸附为每5min

to_char(PACKET_TIME,'yyyy-mm-dd hh24:')||floor(to_char(PACKET_TIME,'mi')/5 )*5||':00' as start_time, ...

- jq:翻页时,保存上页多选框checkbox选中状态

这里主要讲一种:中间的 checkbox 是 通过Ajax调出的. 则翻页时,为了保存上页的选定状态,可在页面中定义一个变量,用来存储选中状态的值. <input class="cli ...

- poj 2485 求最小生成树中 最长的一条边

Sample Input 1 //T 3 //n0 990 692 //邻接矩阵990 0 179692 179 0Sample Output 692 prim # include <iostr ...

- 第一个Struts2实例之hello world!

Struts官网:http://struts.apache.org/ Struts2框架预先实现了一些功能 1:请求数据自动封装 2:文件上传的功能 3:对国际化功能的简化 4 ...

- Eclipse中打包maven项目-war包方式

IntelliJ IDEA打包成war(包括maven项目)点击打开链接 首先要在maven项目中的pom.XML中配置好需要的配置: <project xmlns="http://m ...

- hdu3261

题意: 求至少出现k次的最长字符串(可重复) 题解: 后缀数组维护height数组只要找连续k个的最小值 代码: #include <cstdio> #include <algori ...

- NDK 开发实例一(Android.mk环境配置下)

在我写这篇文章的时候,Android Studio已经是2.3版本了,已经集成CMake 编译工具, 用户只需在 新建项目的时候,添加选项(Include C++ support),Andr ...

- Codeforces 1041F Ray in the tube (看题解)

Ray in the tube 感觉是套路题.. 如果确定一个差值x我们如何取确定答案呢, 我们把a[ i ] -> a[ i ] % (2 * x), 把b[ i ] -> (b[ i ...

- BZOJ5047 空间传送装置 2017年9月月赛 最短路 SPFA

欢迎访问~原文出处——博客园-zhouzhendong 去博客园看该题解 题目传送门 - BZOJ5047 题意概括 概括??~别为难语文做一题错两题的我了…… 题解 我们发现,对于某一种装置,有c种 ...