SoC FPGA JTAG电路设计 要点

JTAG协议制定了一种边界扫描的规范,边界扫描架构提供了有效的测试布局紧凑的PCB板上元件的能力。边界扫描可以在不使用物理测试探针的情况下测试引脚连接,并在器件正常工作的过程中捕获运行数据。

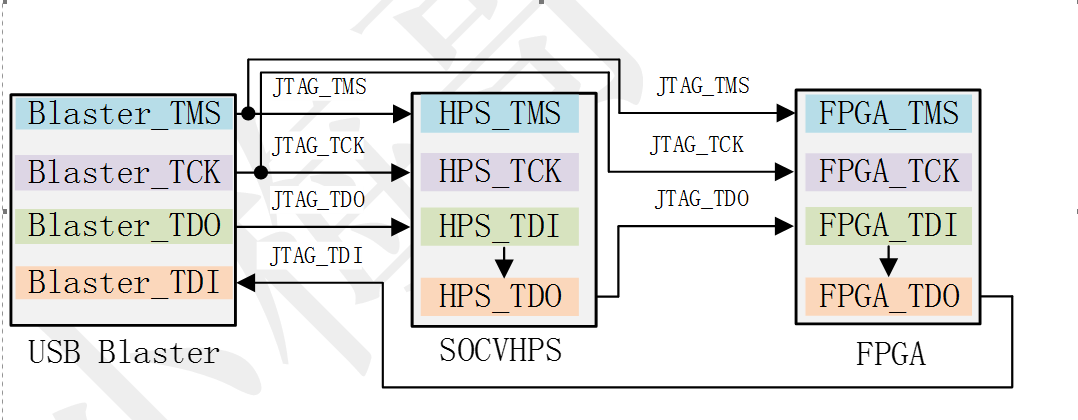

SoC FPGA作为在同一芯片上同时集成了FPGA和HPS的芯片,其JTAG下载和调试电路相较于单独的FPGA或ARM处理器都有一些差异,但是同时两者又有紧密的联系。AC501-SoC开发板上的JTAG链同时连接了FPGA和HPS。使用时,仅需一个JTAG链路,就能同时调试FPGA和HPS。FPGA和HPS各自有其独立的JTAG信号引脚,电路设计时使用了一种串行链的方式来将两者连接到一起,如图xxx所示:

以下为4个JTAG信号的功能说明:

|

管脚名称 |

管脚类型 |

说明 |

|

TDI |

测试数据输入 |

指令以及测试和编程数据的串行输入管脚的。数据在TCK 的上升沿移入。如果在电路板上不需要JTAG 接口,可以通过将此管脚连接至VCC来禁用JTAG。TDI 管脚具有内部弱上拉电阻(通常为25KΩ)。 |

|

TDO |

测试数据输出 |

指令以及测试和编程数据的串行数据输出管脚。数据在TCK的下降沿移出。如果数据没有从器件中被移出,此管脚处于三态。如果在电路板上不需要JTAG接口,悬空此管脚以禁用 JTAG 电路。 |

|

TMS |

测试模式选择 |

提供的控制信号输入管脚,控制信号用来控制TAP状态机的跳变。状态机跳变发生在 TCK 的上升沿。因此,TMS必须在 TCK 的上升沿之前被设置。 TMS 在 TCK 的上升沿中被评估。如果在电路板上不需要 JTAG 接口,JTAG 电路被禁用连接此管脚至 VCC。 TMS 管脚具有内部弱上拉电阻 (通常为25KΩ)。 |

|

TCK |

测试时钟输入 |

边界扫描电路的时钟输入脚。一些操作发生在上升沿,而其它的则发生在下降沿。如果在电路板上不需要JTAG 接口,JTAG 电路被禁用连接此管脚至 GND。 TCK 管脚具有内部弱下拉电阻。 |

使用JTAG配置或调试一个器件时,根据用户选定的器件,编程软件(Quartus Programmer或DS-5中提供的调试器)会旁路所有其它的器件。在旁路模式下,器件通过一个旁路寄存器将编程数据从 TDI 管脚传至 TDO 管脚,即通过TDI送入器件的配置数据会在一个时钟周期之后呈现在TDO上。而如果将TDO端口输出的数据再次接入另个器件的TDI端口,则能够直接对下一个器件进行调试了。而每一个器件都有其JTAG ID,通过JTAG ID能够辨识具体调试哪个器件。

在图xxx(上图)可以看到,由USB Blaster的TDO输出的数据首先是接入到了HPS的TDI端口,然后由HPS的TDO端口流出的数据又接到了FPGA的TDI端口上,最后数据再由FPGA的TDO端口流出,回到USB Blaster的TDI端口,形成了完整的数据回路。

当需要通过Quartus Programer来配置或调试FPGA部分时,会设置直接旁路HPS部分,由HPS的TDI端口流入的数据会在一个时钟周期后出现在HPS的TDO端口上,再进入HPS的TDO端口所连接的FPGA的TDI端口。从而向FPGA的各个寄存器中写入或读取出数据,通过FPGA的TDO端口输出,流入到USB Blaster的TDI端口,完成对FPGA的调试。

当需要通过DS-5中的仿真器来调试HPS部分时,会设置直接旁路FPGA部分,由HPS的TDI端口流入的数据直接作用在HPS上,对HPS的相应的寄存器进行读写,结果数据从HPS的TDO端口流出,再流入FPGA的TDI端口,由于此时FPGA的JTAG功能处于旁路状态,TDI端口流入的数据会直接由FPGA的TDO端口流出,进入USB Blaster的TDI端口,完成对HPS的调试。

SoC FPGA JTAG电路设计 要点的更多相关文章

- SoC FPGA开发板的FPGA配置数据下载和固化

小梅哥编写,未经许可,严禁用于任何商业用途 2018年7月2日星期一 soc fpga的烧写和固化方式与传统的纯fpga固化方式即存在形式上的相同,也存在细节上的差异,特整理此文. AC501-So ...

- Intel Cyclone SoC FPGA介绍

3.1 Intel Cyclone SoC FPGA介绍 3.1.1 SoC FPGA的基本概念 Intel Cyclone V SoC FPGA是Intel PSG(原Altera)于2013年发布 ...

- 关于Xilinx FPGA JTAG下载时菊花链路中的芯片数量

关于Xilinx FPGA JTAG下载时菊花链路中的芯片数量 emesjx | 2014-08-13 13:13:30 阅读:1793 发布文章 当一个系统中含有多片(2片以上)Xil ...

- CPLD和FPGA中不同电压的JTAG电路设计注意事项

在初次的cpld电路设计的时候,遇到了这样的一个问题,整个系统是3.3V的系统,选用的cpld是XC9536-10VQ44C,芯片供电电压5V.他的io可以配置成3.3V和5V两种形式,因此,选用的时 ...

- [原创]FPGA JTAG工具设计(一)

先来看不同JTAG方案,下载配置QSPI Flash所耗时间 基于FTDI方案,JTAG下载时间为494sec JTAG chain configuration ------------------- ...

- 【转载】FPGA算法映射要点

近期一直在学习利用FPGA完成算法的定点运算,转载些相关的博客方面回顾查找.本博文原文链接为:https://blog.csdn.net/u013989284/article/details/7899 ...

- [原创]FPGA JTAG工具设计(二)

经过前期打样 基于FT2232H的JTAG &UART板级已经初步形成 在Viado环境和ISE(13.2+)环境可以使用 速度支持10MHz/15MHz/30MHz 在ISE iMpact下 ...

- sobel算法的Soc FPGA实现之框架分析(二)

重点分析一.AXI_VDMA_1 之前一直认为这个就是内含有DDR的ip核(......最近才搞懂是个啥),后来经过对FDMA的分析发现这就是个框架,通AXI总线挂载到bus总线,可以实现PL端FPG ...

- 《FPGA全程进阶---实战演练》第一章之FPGA介绍

1 什么是FPGA FPGA也即是Field Programmable Gate Array的缩写,翻译成中文就是现场可编程门阵列.FPGA是在PAL.GAL.CPLD等可编程器件的基础上发展起来的新 ...

随机推荐

- Numpy 基础知识

1.使用ipython --pylab 自动加载 Numpy.Scipy.Matplotlib模块. 创建数组a = arange(10) b = arange(10,dtype='f')c = ar ...

- java列表转成 int[] 的格式

java 稀疏矩阵中输入的索引系列和对应的值系列需要用 int[] r_indices = new int[featureIdxList.size()]; 的数据格式. 但是实际中可能实现没法确定 f ...

- Mysql通过SQL脚本复制表

create table if not exists t_dest like t_src 其中,t_src是要复制的原始表,t_dest是要创建的新表.

- Retrofit2.0+RxJava2.0问题

问题1:java.lang.IllegalStateException: Expected a string but was BEGIN_OBJECT at line 1 column 2 path ...

- python3 django连接mysql,同步表结构

第一步:安装PyMySQ代替MySQLdb pip3 install PyMySQL 然后在工程目录的__init__.py中填写下面两句话 import pymysql pymysql.inst ...

- 2014年可用的TRACKER服务器大全

udp://tracker.openbittorrent.com:80/announceudp://tracker.publicbt.com:80/announcehttp://pubt.net:27 ...

- Honeycomb

Honeycomb http://codeforces.com/gym/102028/problem/F time limit per test 4.0 s memory limit per test ...

- python的paramiko模块简单应用

用法1,SSHClient 分别可以使用密码和秘钥登陆,然后执行命令,并且获取执行结果 import paramiko #创建一个SSH对象 ssh = paramiko.SSHClient() #允 ...

- php Pthread 多线程 (三) Mutex 互斥量

当我们用多线程操作同一个资源时,在同一时间内只能有一个线程能够对资源进行操作,这时就需要用到互斥量了.比如我们对同一个文件进行读写操作时. <?php class Add extends Thr ...

- jxl 创建excel

public static void performanceExcel(String sCurrPath,List<Record> list, String begin,String en ...