verilog注释及vscode插件terosHDL

模型功能

- 实现代码的注释的方法

- 基于vscode的文档自动生成

模型框图

`timescale 1ns / 1ps

/*

*/

// *******************************************************************************

// Company: Fpga Publish

// Engineer: FP

//

// Create Date: 2024/03/24 12:39:43

// Design Name:

// Module Name: verilog_demo

// Project Name:

// Target Devices: ZYNQ7010 | XCZU2CG | Kintex7

// Tool Versions: 2021.1 || 2022.2

// Description:

// *

// Dependencies:

// *

// Revision: 0.01

// Revision 0.01 - File Created

// Additional Comments:

//

// *******************************************************************************

module verilog_demo #(

//mode

parameter MD_SIM_ABLE = 0,

//number

//width

parameter WD_ERR_INFO = 4

)(

//! system signals

input i_sys_clk ,

input i_sys_resetn,

//! @virtualbus uart_interface @dir out

output m_uart_0_mtx, //! uart master tx

input m_uart_0_mrx, //! uart master rx

//! @end

//! error info feedback

output [WD_ERR_INFO-1:0] m_err_verilog_info1

);

//========================================================

//function to math and logic

//========================================================

//localparam to converation and calculate

//========================================================

//register and wire to time sequence and combine

// ----------------------------------------------------------

//

//========================================================

//always and assign to drive logic and connect

//========================================================

//module and task to build part of system

//========================================================

//expand and plug-in part with version

//========================================================

//ila and vio to debug and monitor

endmodule

/* end verilog

*/

实现步骤

- verilog的注释语法和C语言一样

- 文件头注释模型源自vivado自动生成的模板

- 端口列表的注释语法源自vscode的插件terosHDL

- 为了统一和适应verilog描述的特点,将注释分为两层:

- 结构层: // ================

- 内容层: // ----------------

- 结构层负责划分verilog的语法区域,使得语法的调用顺序满足要求

- 常数声明 》 变量声明 》 逻辑赋值 》 模块调用 》 任务调度 》 插入逻辑 》 在线调试

- 虽然大部分的编辑器都支持赋值先于声明,但是modelsim不支持,为了兼容,还是要求设计结构保持最规范的顺序

- 内容层则是负责将各个独立的内容在某个结构中的分布区分出来

- 大部分的情况下,一个内容会分布在多个结构中

- 为了方便查找,可以对相同的内容进行编号,方便查找

- 当然,也可以简单的作为分割逻辑功能的分割线

- markdown的拓展

- 如源码所示,利用双语法注释,可以实现markdown的注释

- 目前主要是用于插入一些复杂的计算公式和需要成表格的注释

- 当然,也可以进行状态机的插入,但是terosHDL可以自动识别,所以该功能就没有很大的必要

- terosHDL的拓展

- 需要归入文档的注释需要在//后面增加!符号,常规注释直接使用//

- 一般来说,除了逻辑实现方法这类需要和代码一起阅读的注释,其他的注释都需要加入文档

- 这个更多取决于文档的要求,可以根据个人的代码规范进行区分

- 笔者更喜欢使用vscode将所有非判断注释都加入文档

- 插入时序图

- 这个语法可以在插件的帮助文档中获取

- 当然,如果用过wavedrom这个基于json的时序图绘制软件,那就会简单很多

- 具体的例子如下:

//! { signal: [

//! { name: "clk", wave: "P......" },

//! { name: "bus", wave: "x.==.=x", data: ["head", "body", "tail", "data"] },

//! { name: "wire", wave: "0.1..0." }

//! ],

//! head:{

//! text:'WaveDrom example',

//! tick:0,

//! every:2

//! }}

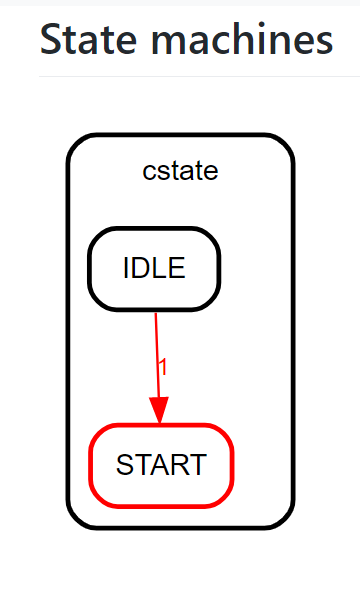

- 插入状态机

- terosHDL支持自动识别状态机并插入到对应的位置

- 同时会显示状态机的跳转条件,可以用于快速地分析模块的逻辑

- 具体的效果如下:

/* @begin state machine */

//state name

localparam IDLE = 0;

localparam START = 1;

//state variable

reg [3:0] cstate = IDLE;

//state logic

always @(posedge i_sys_clk)

if(!i_sys_resetn)

begin

cstate <= IDLE;

end

else

begin

case(cstate)

IDLE : if(1) //whether goto next state

begin

if(1) //which state to go

begin

cstate <= START;

end

end

default: cstate <= IDLE;

endcase

end

/* @end state machine */

- 除了文档外,还有一些原理图查看、仿真模板生成等功能

- 这些功能笔者一般在vivado完成,就没有进行过多的探索,这个可能需要java的支持,感兴趣可以自行按照教程添加

最终效果

调用接口

- 无调用模型库

verilog注释及vscode插件terosHDL的更多相关文章

- VSCODE 插件初探

写在前面 分享一个vscode插件background(用于改变背景).点击直接跳到vscode插件开发步骤 做vscode的插件,很久就有这个想法了,但是一直因为这样,那样的事情耽误,放弃了N次.不 ...

- 精选!15 个必备的 VSCode 插件(前端类)

精选!15 个必备的 VSCode 插件(前端类) 就像大多数 IDE 一样,VSCode 也有一个扩展和主题市场,包含了数以千计质量不同的插件.为了帮助大家挑选出值得下载的插件,我们针对性的 ...

- 个人向 - vscode插件记录

现在用的编译器的是vscode,本身这个编译器很小,很多功能都没有,需要自己下载一些插件来完善功能,不知不觉下载的插件也有三十多个了,感觉需要记录一下. tips:1. vscode插件的安装位置:’ ...

- 2019.1.7 Mac的Vscode插件总结

Vscode插件 通用插件 Chinese 配置中文界面 HTML Snippets H5代码片段以及提示 HTML CSS Support 让 html 标签上写class 智能提示当前项目所支持的 ...

- 玩转VSCode插件之Remote-SSH

前言 每当更换电脑就要从新搭建一遍开发环境... 每当拉完最新代码程序在本地跑不起来的时候就要检查服务器和开发电脑的环境... 每当服务器上出Bug的时候就想如果可以能够调试服务器代码多好啊.. 你是 ...

- 用VSCode插件来一键填满Github的绿色格子吧-AutoCommit

autoCommit 一个用于Git自动commit的VSCode插件,它可以用来补充之前忘记提交commit,帮助你把首页的绿色格子填满. 使用效果 使用本插件来控制commit次数. 如下图,你甚 ...

- 干货:用好这13款VSCode插件,工作效率提升10倍

文章每周持续更新,原创不易,「三连」让更多人看到是对我最大的肯定.可以微信搜索公众号「 后端技术学堂 」第一时间阅读(一般比博客早更新一到两篇) 大家好我是lemon, 马上进入我们今天的主题吧. 又 ...

- 全栈工程师-史上最强VSCODE插件-提高开发效率

当你点进来的时候 ,你可能是被标题吸引进来的,也有可能是 偶然间,看到的,首先恭喜你,已经准备好向全栈开发工程师靠近 ,那我们不说废话,直接开始,咱们先从安装步骤开始讲起 ,因为有些人连插件在哪都不知 ...

- 30 个极大提高开发效率超级实用的 VSCode 插件

Visual Studio Code 的插件对于在提升编程效率和加快工作速度非常重要.这里有 30 个最受欢迎的 VSCode 插件,它们将使你成为更高效的搬砖摸鱼大师.这些插件主要适用于前端开发人员 ...

- 知乎vscode插件修改和重新编译

需求来源 vscode插件修改代码要怎样重新编译并安装到vscode中? 起源于我使用一个vscode插件,它可以在vscode中发布文章到知乎上,然后我修改了插件的部分源代码,希望在vscode中安 ...

随机推荐

- Windows也能拥有好用的命令行吗?Powershell+Terminal折腾记录(v1.0版本)

PS:本文写于2021年,现在已经是2024年,有了很多新变化,我在接下来的文章里会继续更新. 前言 Windows一向以图形化操作入门容易著称,所以对于命令行的支持一直为人所诟病,比起Linux或者 ...

- Thinkpad笔记本指点杆(小红点)自动漂移的问题

Dell, HP, Thinkpad在高端商务机上会配备指点杆(小红点), 有很多人是指点杆的忠实用户, 因为工作时可以双手不离键盘, 非常方便. 在指点杆的使用过程中, 有时候会遇到指点杆自己漂移的 ...

- 【Unity3D】Renderer Feature简介

1 3D 项目迁移到 URP 项目后出现的问题 3D 项目迁移至 URP 项目后,会出现很多渲染问题,如:材质显示异常.GL 渲染不显示.多 Pass 渲染异常.屏幕后处理异常等问题.下面将针对这 ...

- Oracle高级队列介绍

原始链接:http://www.oracle-developer.net/display.php?id=411 oracle高级队列介绍 高级队列Advanced Queuing(AQ)在oracle ...

- MASM32 - PlaySound的实现

MASM安装教程: https://blog.csdn.net/u010486308/article/details/105495848 代码参考: .model flat, stdcall opti ...

- File.delete()和Files.delete(Path path)的区别

文件删除时可以选择File.delete()和Files.delete(Path path),这两个方法到底有什么区别呢? //删除暂存的pdfFile file =new File(pdfFilen ...

- ZYNQ核心板及其底板开源啦!

Hello-FPGA ZYNQ 设计开源啦! 开源ZYNQ核心板 + 底板 硬件设计.软件设计,软件设计使用裸机演示,演示了如何使用AXI DMA等关键dma 模块 欢迎加QQ 讨论 94755958 ...

- Redis高级数据类型

## 1.Redis相关配置信息 服务器端设定 设置服务器以守护进程的方式运行 daemonize yes|no 绑定主机地址 (只能此ip访问) bind 127.0.0.1 设置服务器端口号 po ...

- Alertmanager钉钉告警

一.部署alertmanager 1.1 创建目录 mkdir -p /deploy/app/alertmanager/config chmod -R 777 /deploy/app/alertman ...

- windows下如何结束Tomcat进程

问题描述: 使用IDEA启动java中的SSM项目之后,服务正常运行.操作过程中不小心把IDEA 开发工具给关闭啦,导致tomcat没有正常停止,使用的端口8080仍然被占用.再次 打开IDEA,启动 ...