PicoRV32-on-PYNQ-Z2: An FPGA-based SoC System——RISC-V On PYNQ项目复现

本文工程:

https://bhpan.buaa.edu.cn:443/link/4B08916BF2CDB42DB78976BCCDB712E2

1.准备工作

下面以LOCATION代表本地源存储库的安装目录,以home/xilinx代表在PYNQ-Z2开发板上的目录

下载Vivado2017.4

由于最初的源工程是利用Vivado2017.4来创建的,可能也有一些方法可以在其他版本打开,但没有原始工程的xpr文件,所以下载了一个Vivado2017.4,网上的安装教程很多。下载两个源存储库:

①

git clone https://github.com/drichmond/RISC-V-On-PYNQ

其中,RISC-V-On-PYNQ中的Picrov32是以子模块的形式链接在仓库中,需要通过下面的链接下载后再传入RISC-V-On-PYNQ中相应的位置。

https://github.com/YosysHQ/picorv32/tree/9b6ea045f9b539b0f708d71962716e5dde865181

或者可以通过下面的命令直接递归下载子文件夹

git clone --recursive https://github.com/drichmond/RISC-V-On-PYNQ

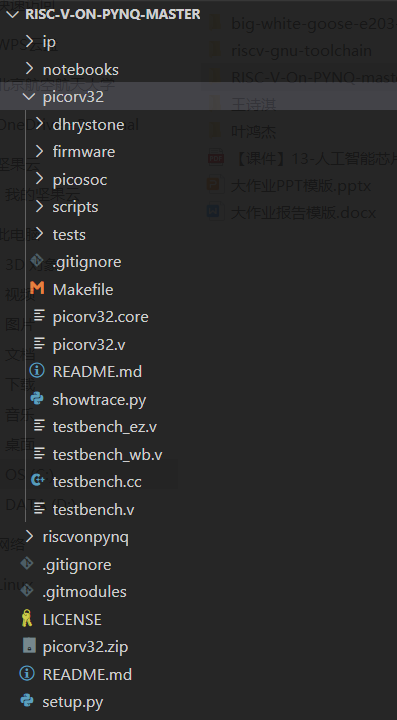

最后RISC-V-On-PYNQ中的目录结构应如下图所示

②

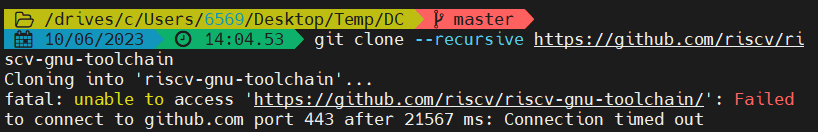

git clone --recursive https://github.com/riscv/riscv-gnu-toolchain \home\xilinx\riscv-gnu-toolchain

此为RISC-V工具链,在下载过程中可能会遇到以下报错:

单纯的网络连接不稳定,可以网页开个github试下,什么时候能打开了,这边也就通了。

若报错Git 客户端无法验证服务器证书的有效性,因此无法建立与服务器的安全连接,可以使用以下命令来配置 Git 客户端:

git config --global http.sslVerify false

git config --global https.sslVerify false

以及如果网络一直不太好的话,据说有这个方法可以通过增加缓存大小来提速(因为没有对比测试过,所以我也不太确定这个有没有大用つ﹏⊂)

git config --global http.postBuffer 524288000

再如果说,一直出现各种报错的话,可以将本工程文件中主目录下的makefile文件通过WinSCP传入PYNQ-Z2,并在相应目录下执行

make download-tools

此为自动下载的脚本,来源于Picorv32工程,可以判断目录下的递归文件夹是否安装,但也会由于网络连接问题重开,如果说网络问题是在无法解决,gitee上据说有相应的库,可能会好一些。

2.生成RISC-V处理器比特流

- 将Picrov32封装成为Vivado IP:

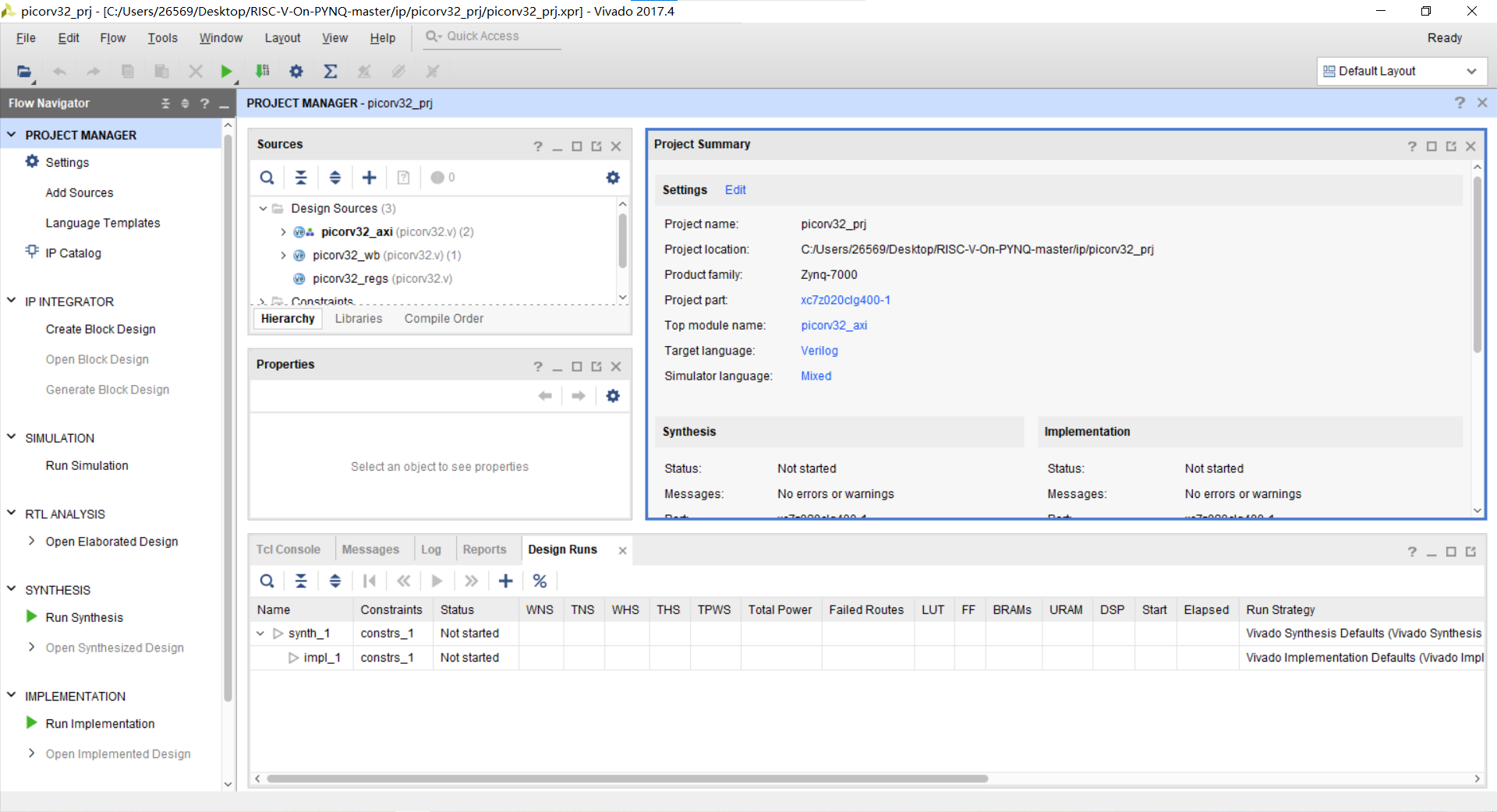

使用Vivado 2017.4创建一个工程:

Project name: picorv32_prj

Project location: LOCATION/RISC-V-On-PYNQ/ip/

Project Type: RTL Project

Source files: picorv32.v LOCATION/RISC-V-On-PYNQ/picorv32

Constraint files: None

parts: xc7z020clg400-1

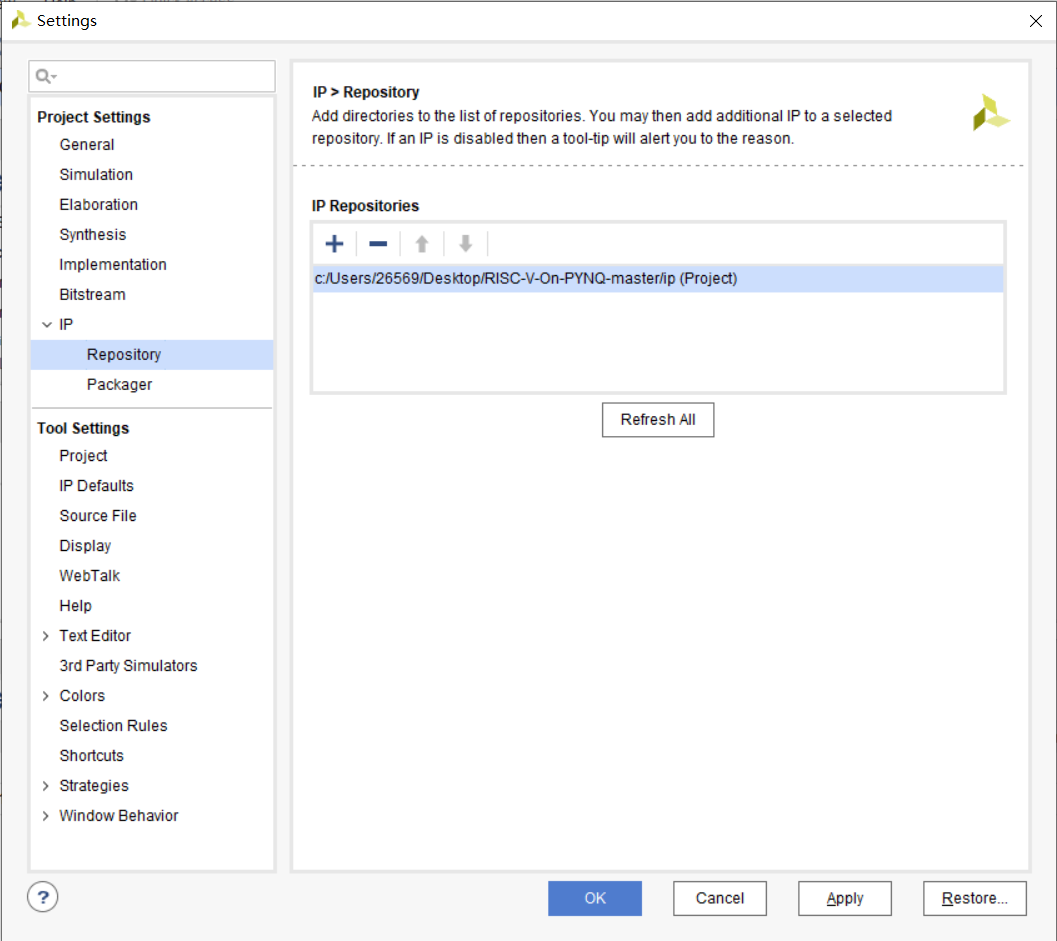

将自定义接口IP添加到Vivado工程:Flow Navigator->PROJECT MANAGER->Settings

将该工程封装为IP核:Tools -> Create and Package New IP…

Packaging Options: Package your current project

IP location: LOCATION/RISC-V-On-PYNQ/ip/picorv32_tut

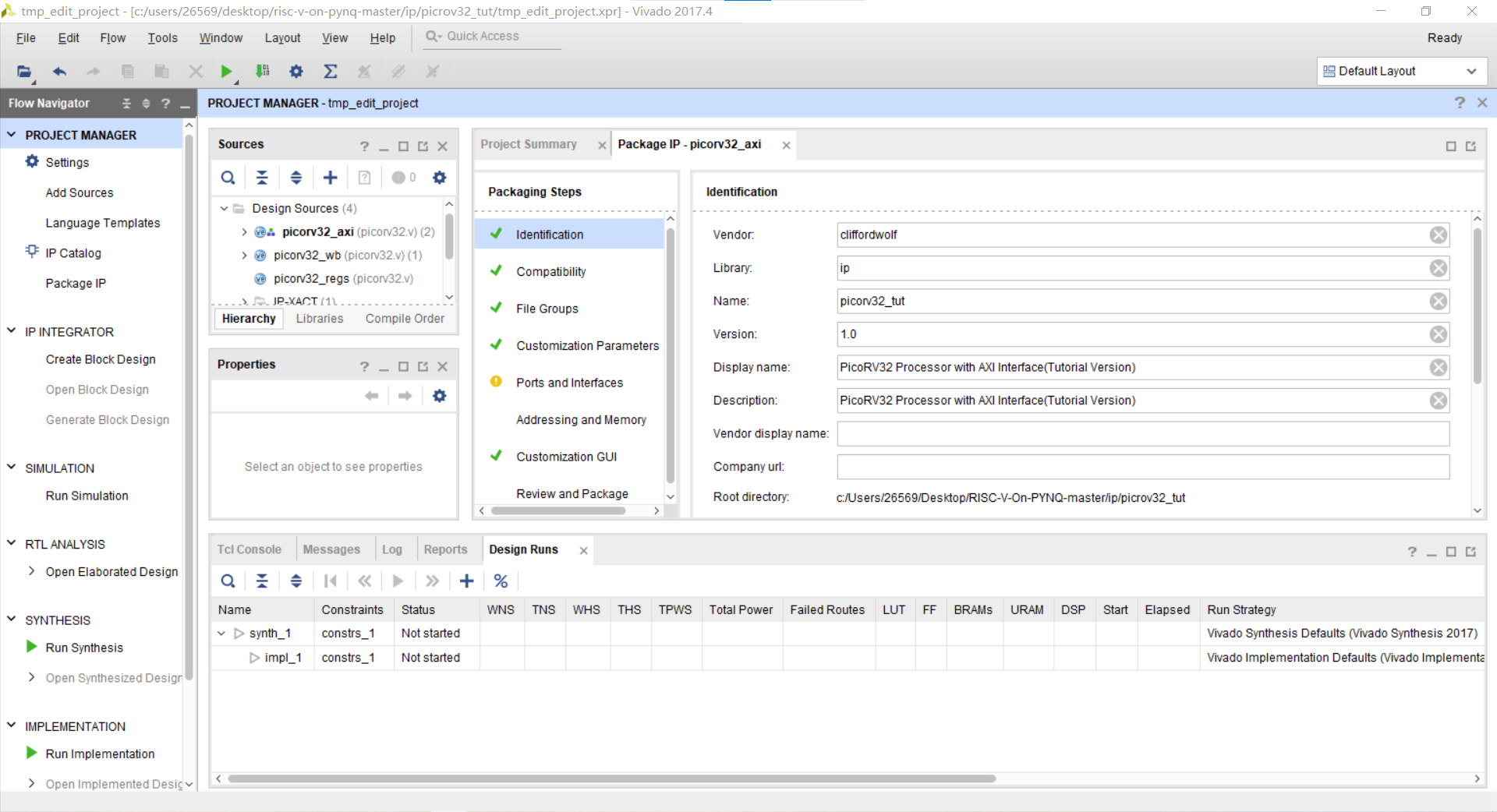

Identification:

Vendor: cliffordwolf

Library: ip

Name: picorv32_tut

Display name: PicoRV32 Processor with AXI Interface(Tutorial Version)

Vendor display name: PicoRV32 Processor with AXI Interface(Tutorial Version)

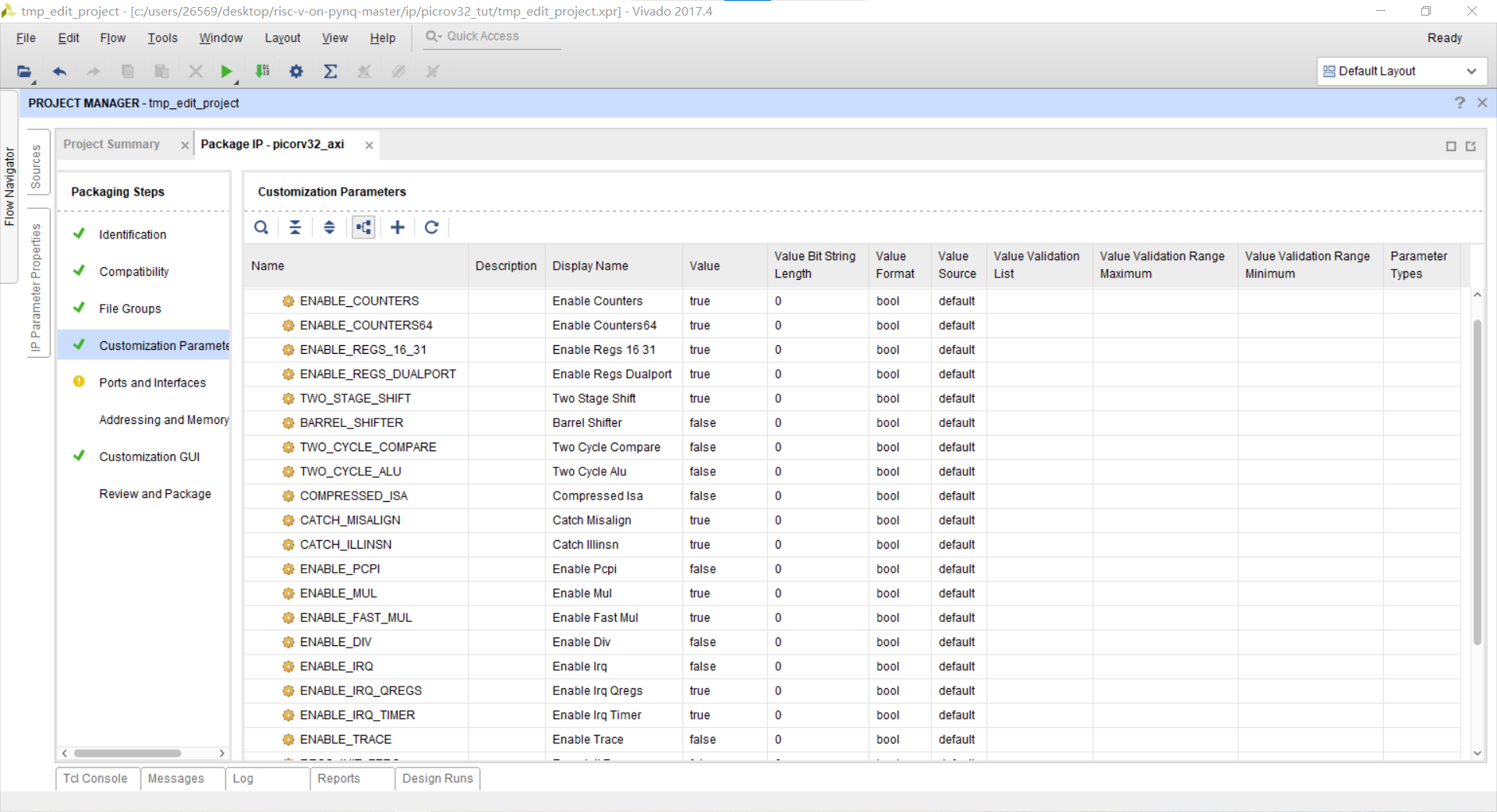

Customization Parameters:

就所有参数值的格式均改为bool,并按照图中所示的值对参数值进行修改

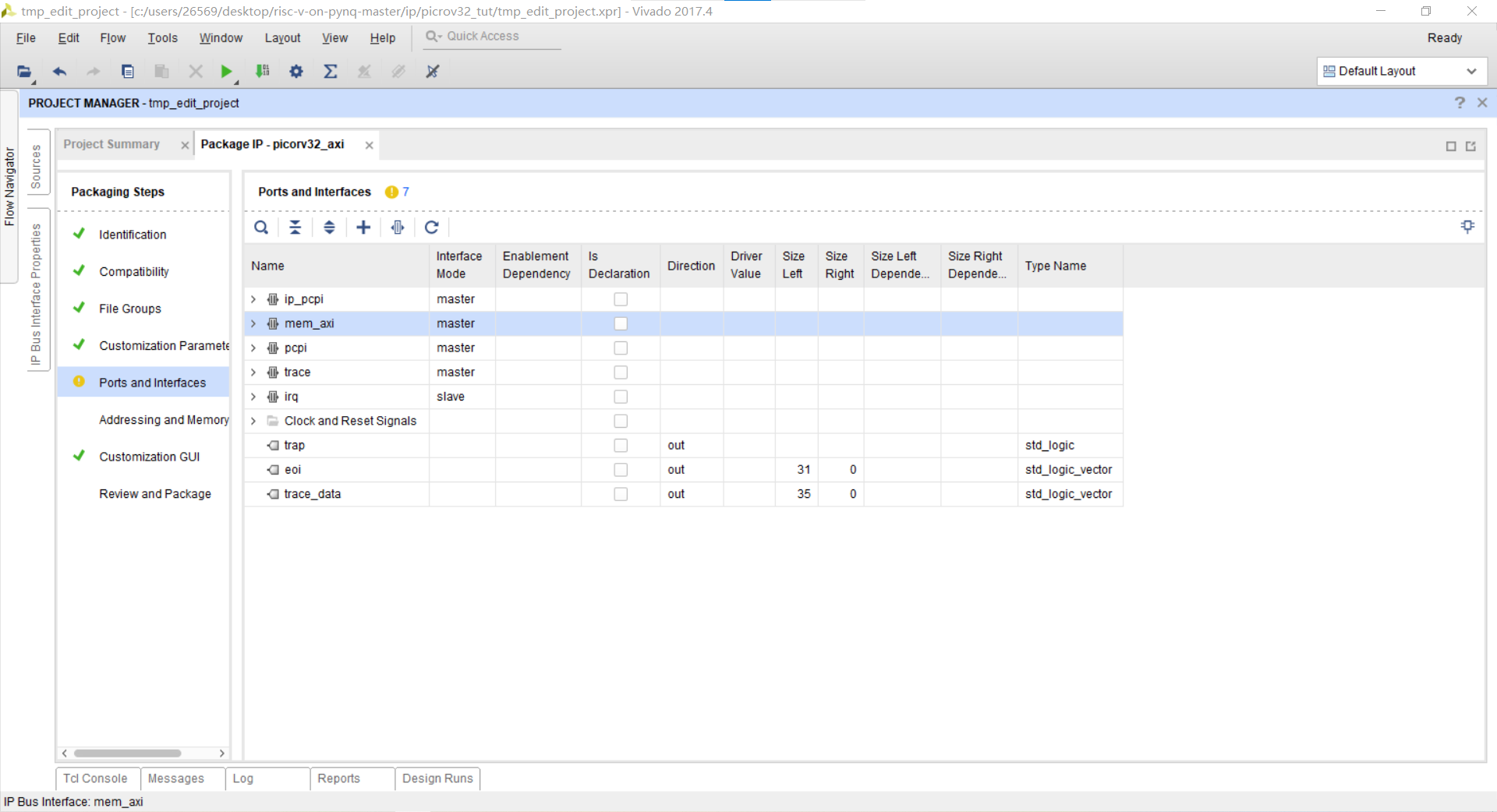

Ports and Interfaces:

右键mem_axi->Edit Interface…

**General:**

Interface Definition: aximm_rtl

**Port Mapping:**

AWADDR - mem_axi_awaddr

AWPROT - mem_axi_awprot

AWVALID - mem_axi_awvalid

AWREADY - mem_axi_awready

WDATA - mem_axi_wdata

WSTRB - mem_axi_wstrb

WVALID - mem_axi_wvalid

WREADY - mem_axi_wready

BVALID - mem_axi_bvalid

BREADY - mem_axi_bready

ARADDR - mem_axi_araddr

ARPROT - mem_axi_arprot

ARVALID - mem_axi_arvalid

ARREADY - mem_axi_arready

RDATA - mem_axi_rdata

RVALID - mem_axi_rvalid

RREADY - mem_axi_rready

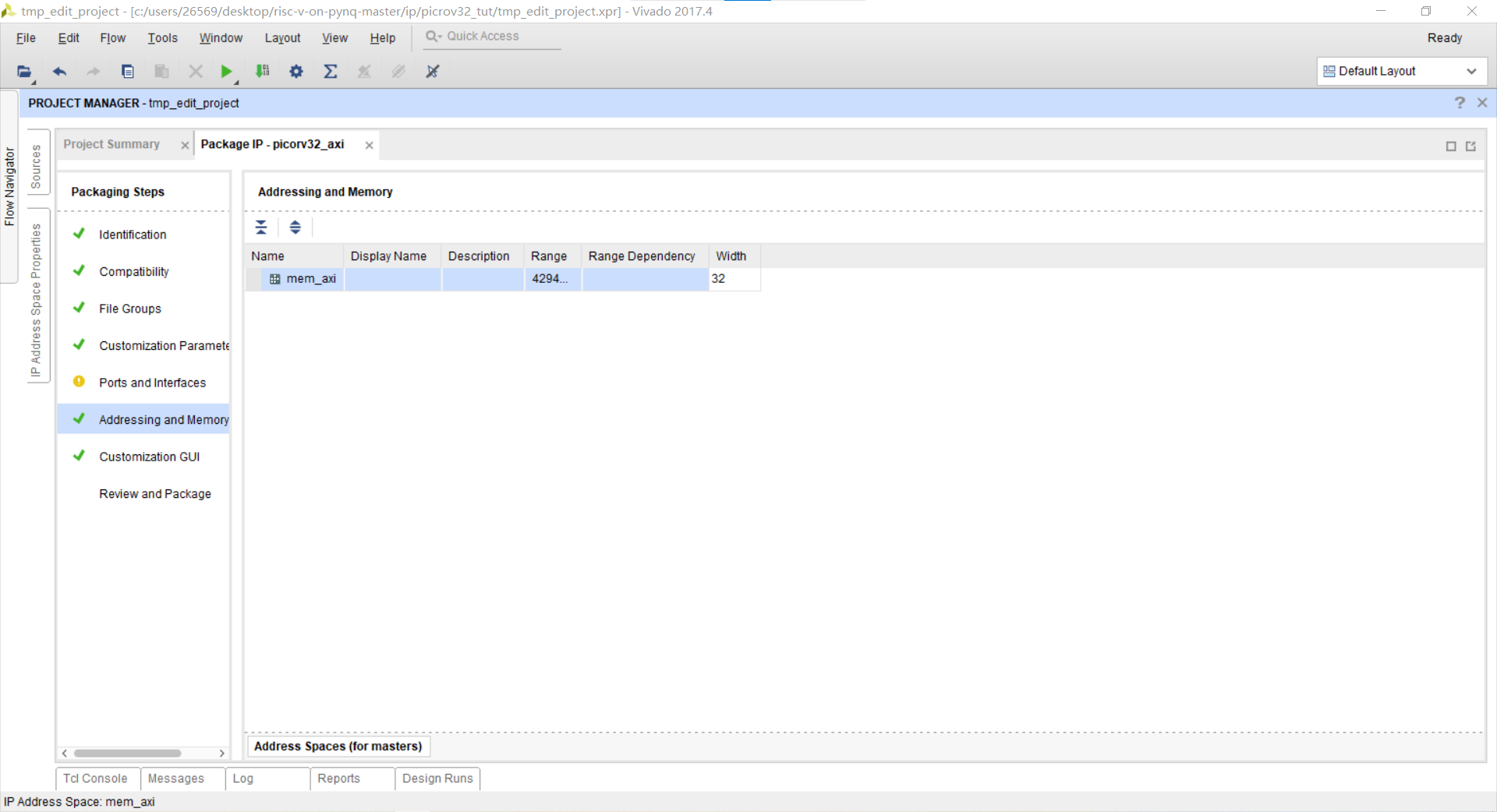

Addressing and Memory:

运行Addressing and Memory Map Wizard,选择mem_axi,相关设置如下图所示

Review and Package:

点击Package IP即可。

- 为PYNQ-Z2创建RISC-V比特流:

将LOCATION/RISC-V-On-PYNQ/riscvonpynq/目录下的PYNQ-Z1.xdc文件的72,73行改为如下:

set_property -dict {PACKAGE_PIN P15 IOSTANDARD LVCMOS33} [get_ports arduino_iic_scl_io]

set_property -dict {PACKAGE_PIN P16 IOSTANDARD LVCMOS33} [get_ports arduino_iic_sda_io]

在目录LOCATION/RISC-V-On-PYNQ下右键打开MobaXterm,执行以下命令:

make synth

vivado tutorial/tutorial.xpr

若报错没有make命令,则可\(apt-get\) \(make\)进行安装;

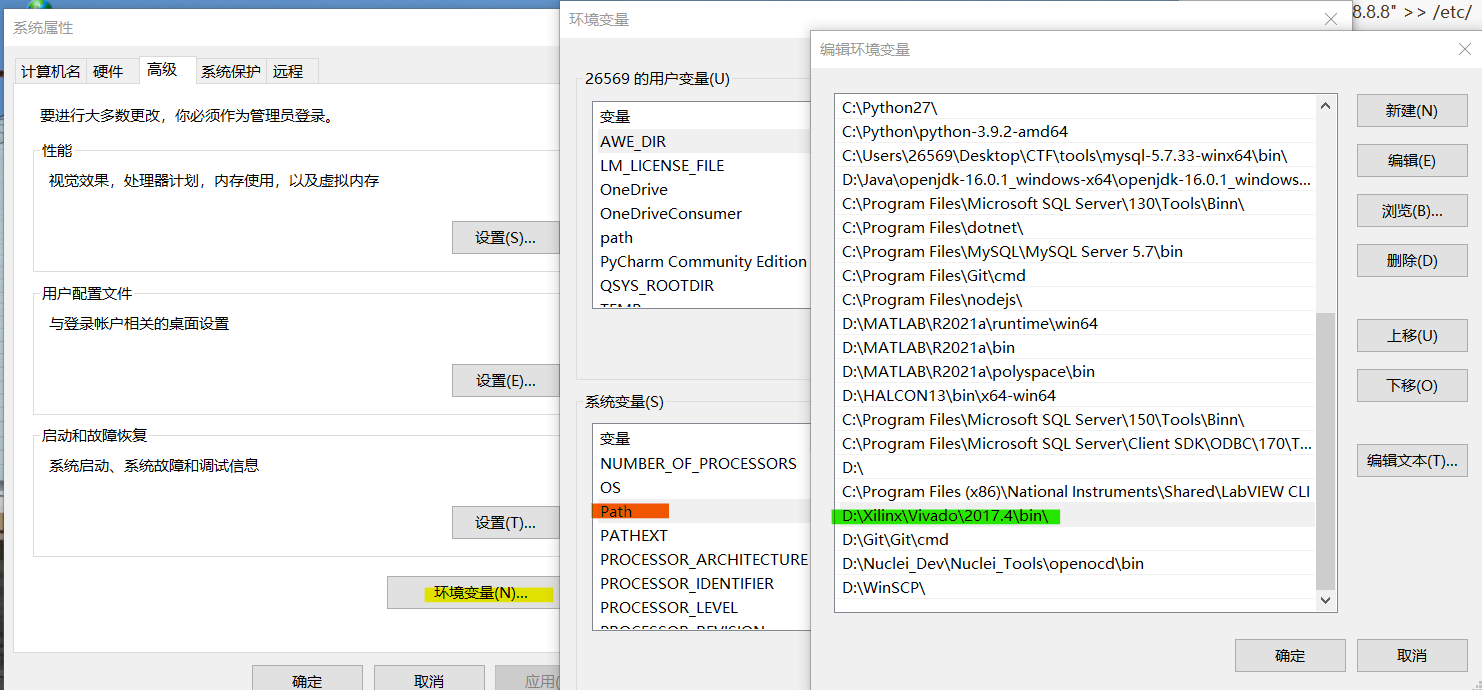

若报错没有vivado命令,则是由于未将Vivado添加到环境变量中,找到Vivado的安装目录下的bin目录,按下图所示添加到环境变量中,

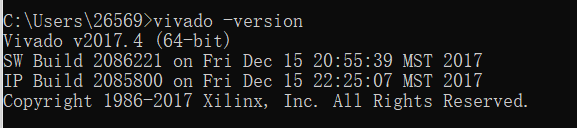

Win+R打开cmd,输入\(vivado\) \(-version\)检查环境变量是否配置成功,成功则有如下显示

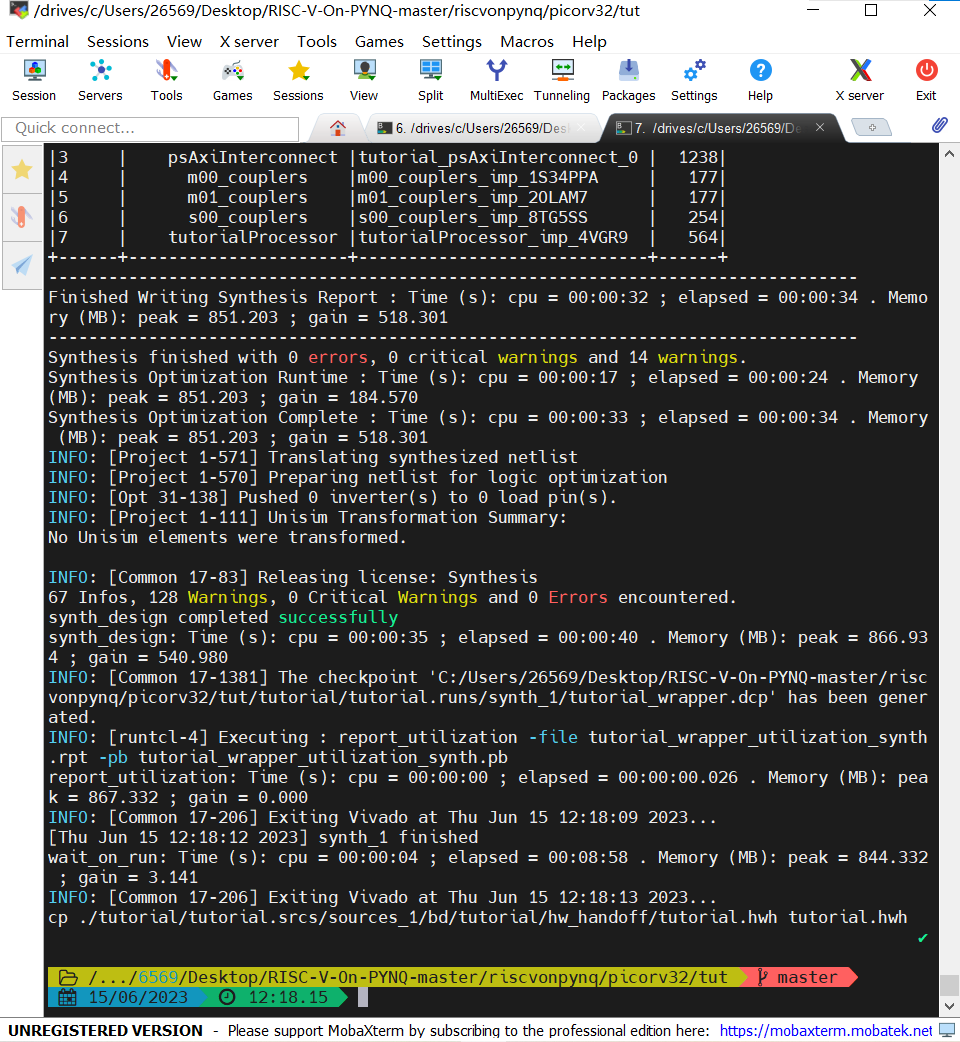

执行上面的第一条命令,vivado将进行创建工程并综合,综合结果如下,即可输入第二条命令打开工程

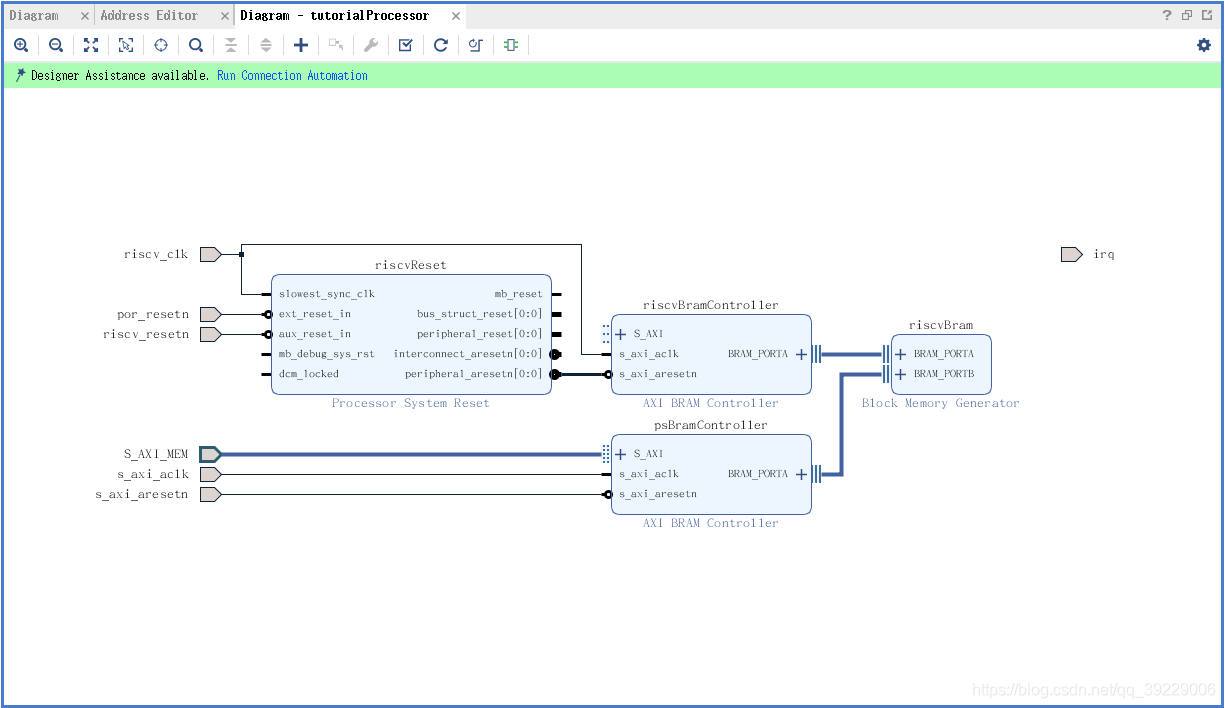

执行命令完成后将打开tutorial.xpr工程,打开其中的tutorial.bd文件

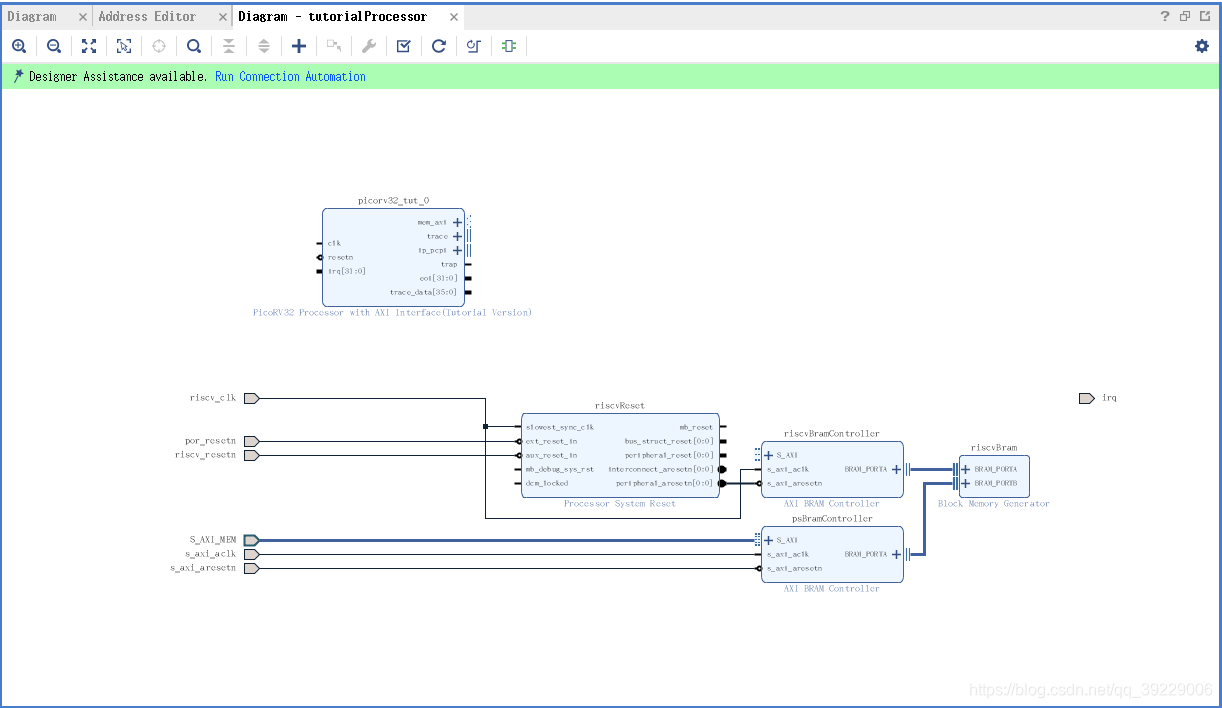

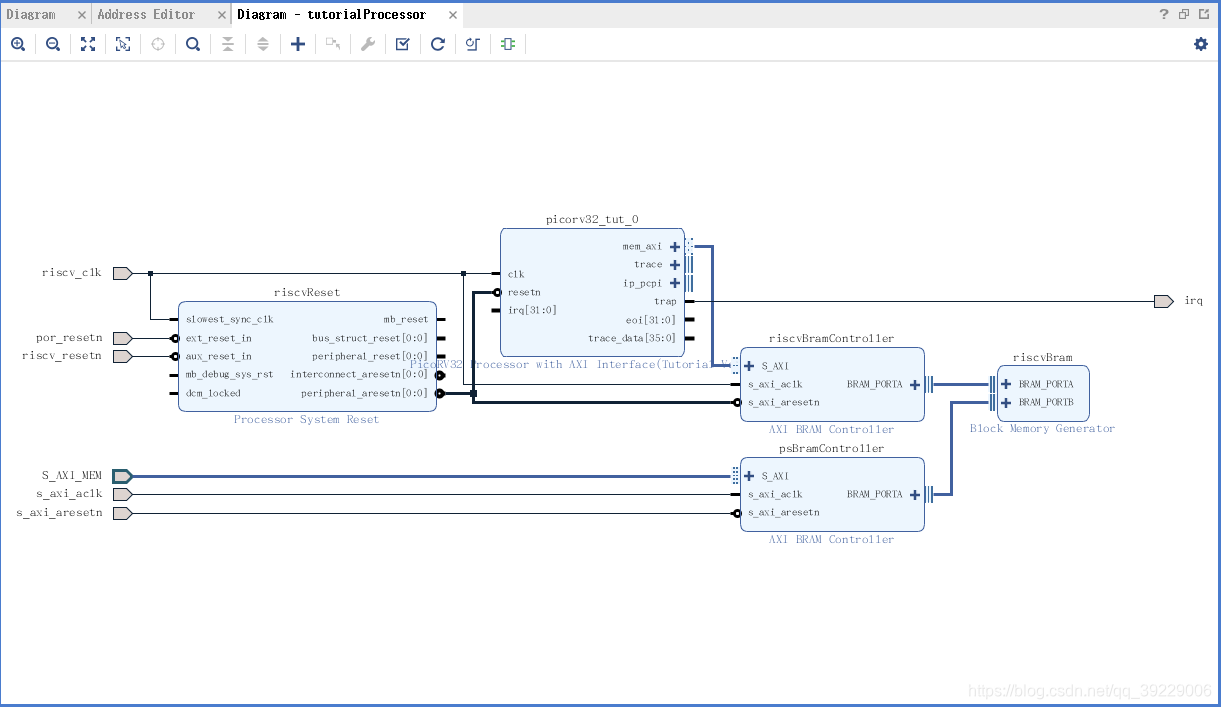

双击tutorialProcessor:

点击+号 , 将PicoRV32 Processor with AXI Interface (Tutorial Version) IP添加进去:

双击端口mem_axi,修改其频率为50000000。

并按照下图连线:

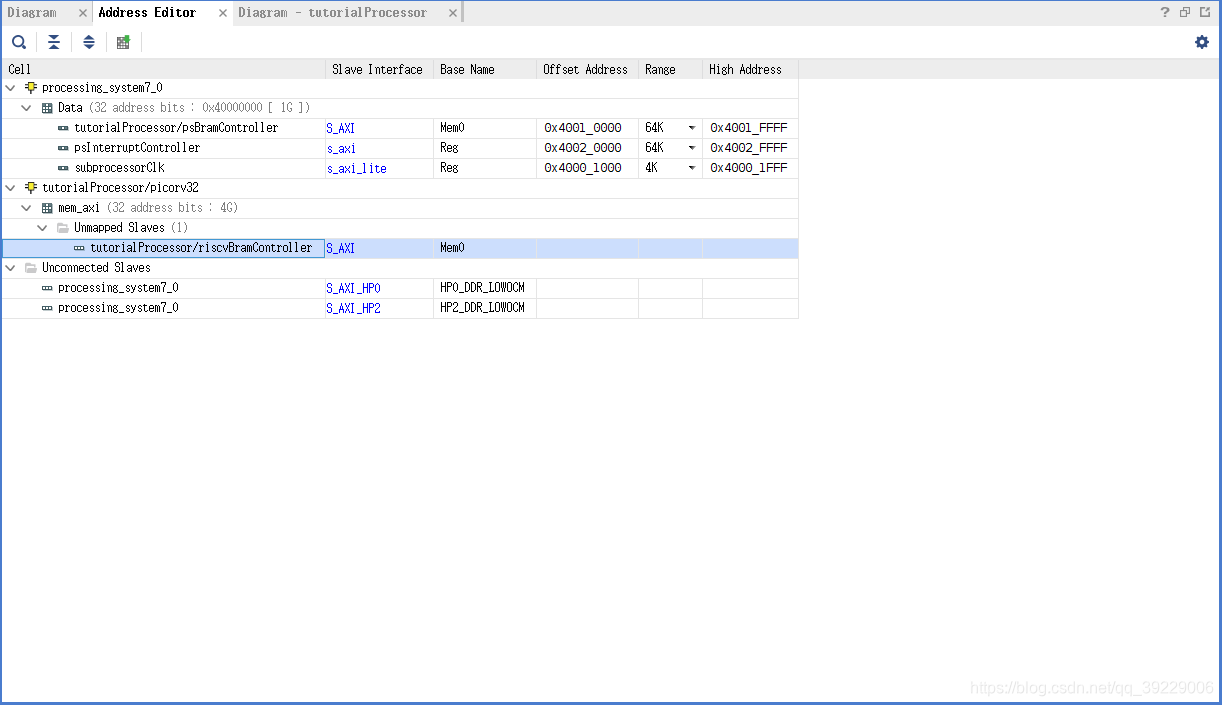

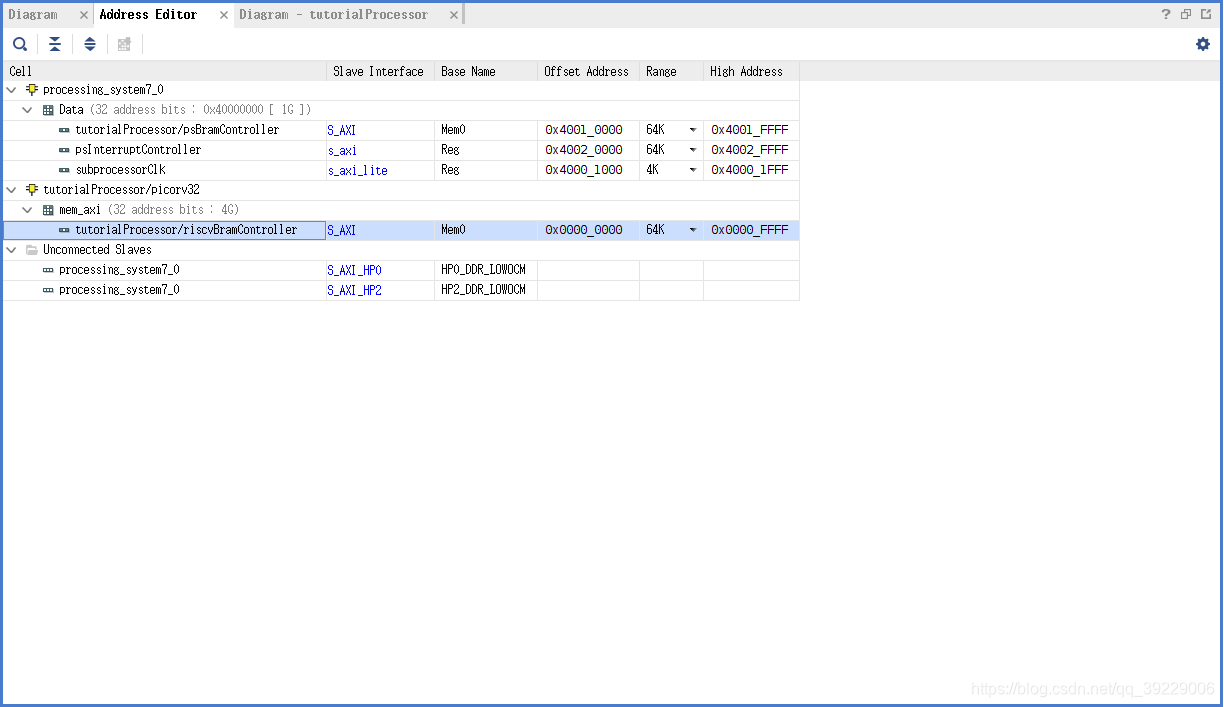

进入Address Editor窗口,分配地址映射:

右击tutorialProcessor/riscvBramController->Assign Address

Offset Address: 0x0000_0000

High Address: 0x0000_FFFF

运行Tools-Validate Design,提示有warning直接跳过

点击Generate Bitstream生成比特流文件,文件位置为:\(/tut/tutorial/tutorial.runs/impl\_1\),将tutorial_wrapper.bit文件转移到tut目录下,并改名为tutorial.bit

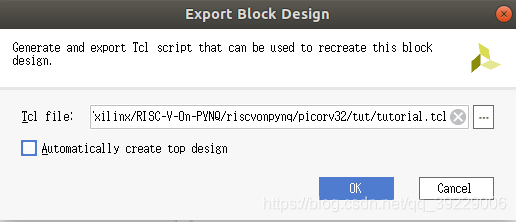

点击File->Exports…->Export Block Design,导出设计到tcl文件中并覆盖之前的文件,同时需确保Automatically create top design没有被勾选

将操作完成的整个工程放到PYNQ-Z2的home/xilinx目录下

3.在PYNQ-Z2上编译RISC-V GCC工具链

- 工具链的下载:

在按照官方例程进行下载时,出现了很多的报错问题,反复尝试了很多次都未能解决,而且经常由于网络连接问题而重开。

最终在上面的参考博客中找到了整个工具链的自动安装脚本,即工程主目录下的Makefile文件。

在目标安装目录下执行命令

make download-tools

便开始了漫长的下载过程,期间在安装完一个子模块后可能会卡住然后报错,这种情况绝大多数是因为网络原因造成的,如果失败了可以再执行一次上述的命令,当一个子模块安装好,重新执行命令时会自动跳过安装好的模块,继续下一个模块的安装。

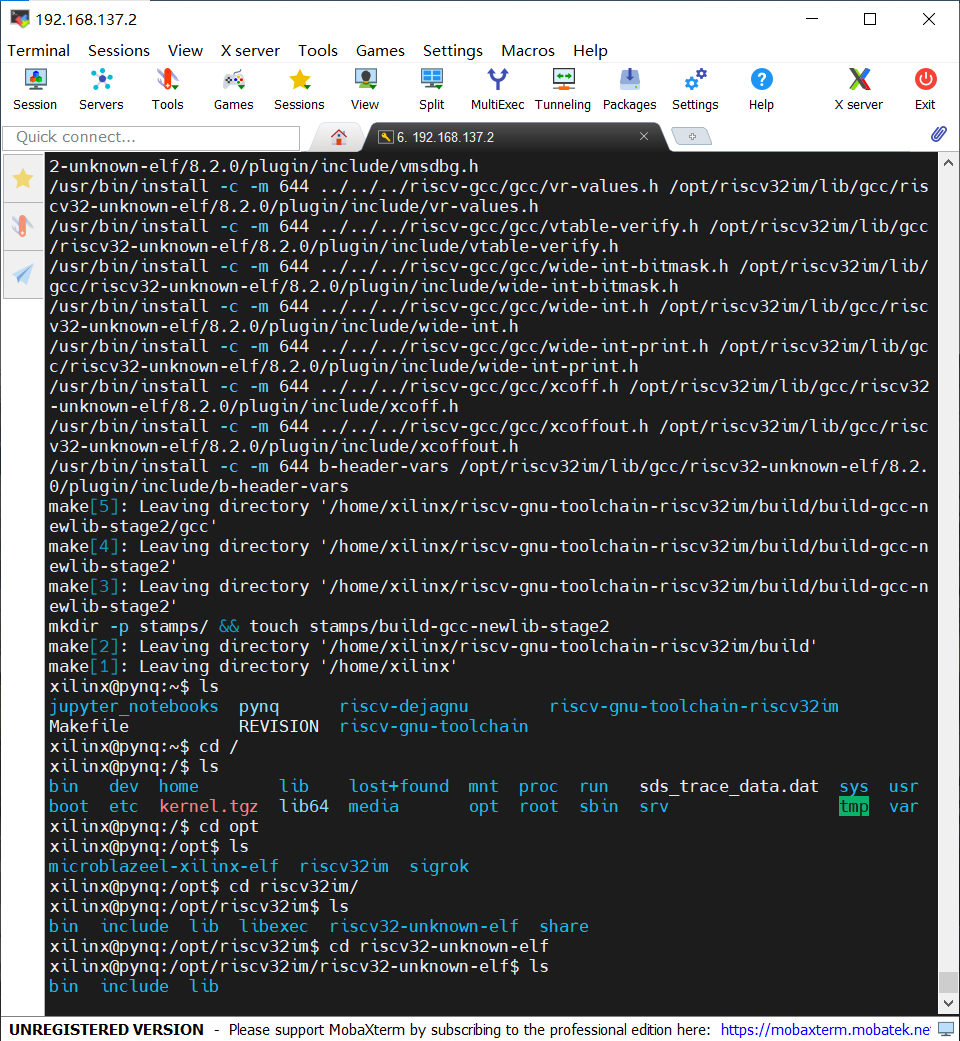

在安装完所有的模块后,执行如下命令,便可以构建一个纯RV32IM CPU的完整工具链了

make -j$(nproc) build-riscv32im-tools

回车后在命令行输入YES即可执行。

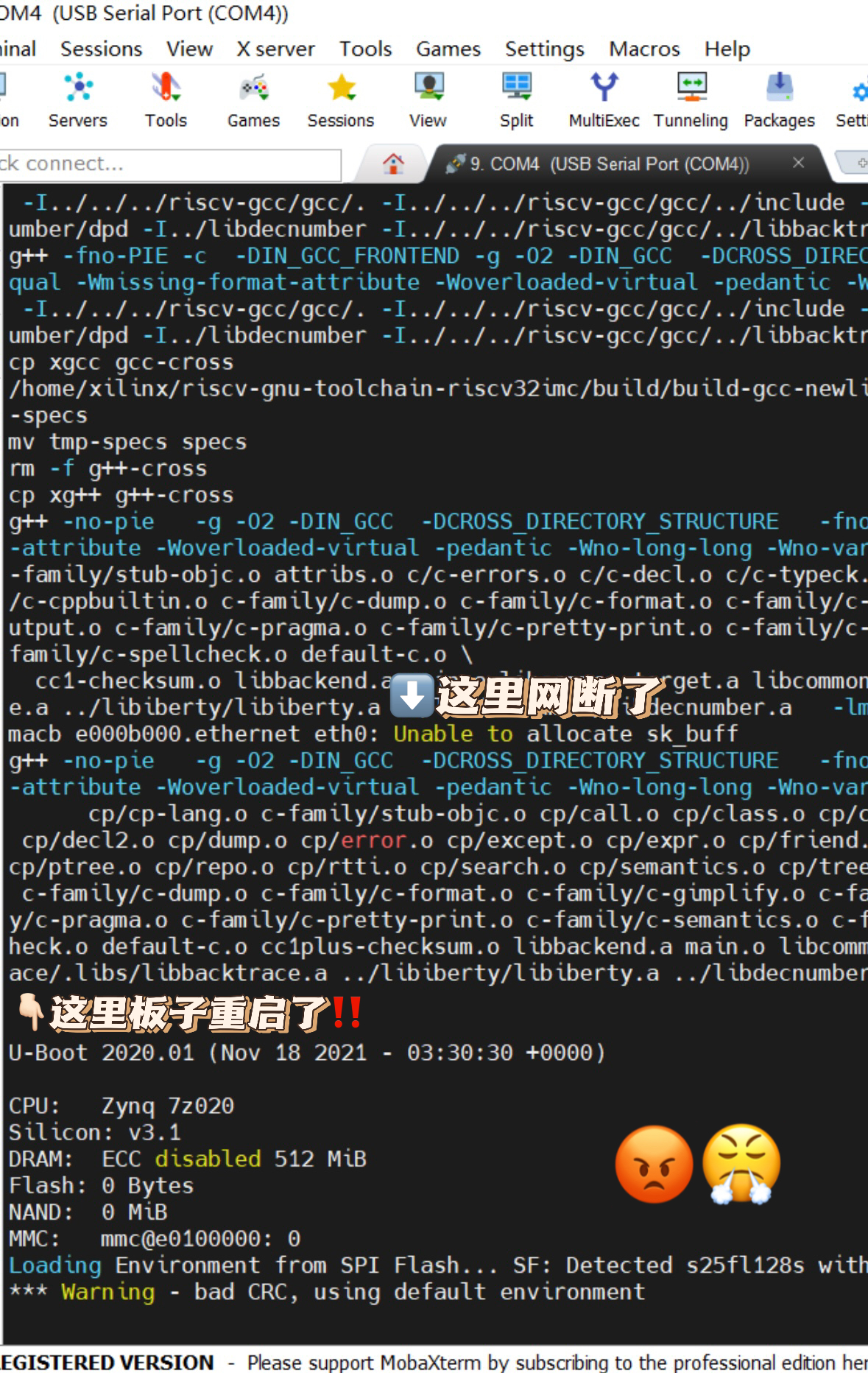

该步骤会等待的时间较长,去问了相关的博主,他们的编译时间大概在1h左右,猜测可能是由于我是通过PYNQ联网的原因,我的执行时间大概在四五个小时左右,过程中最好别碰,一断网那种心碎

编译成功后的界面如下

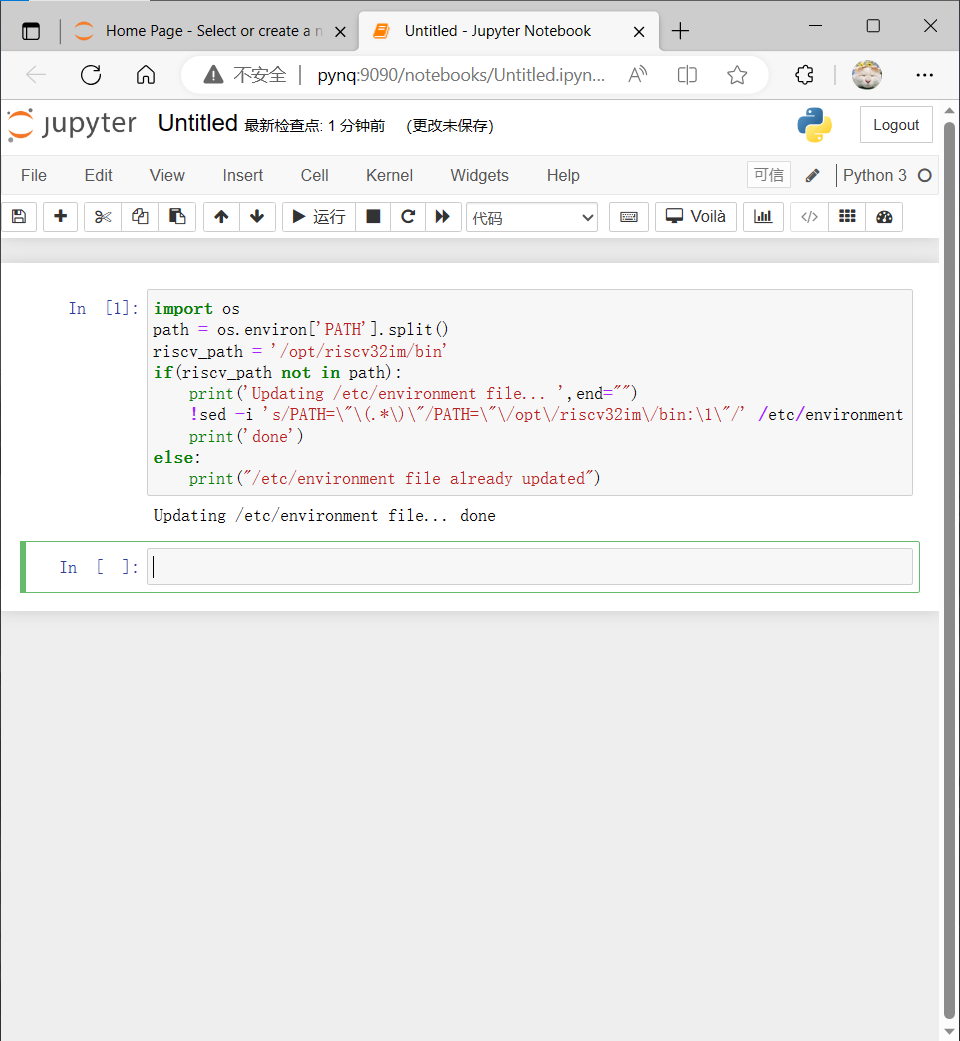

执行下面语句将编译生成的\(opt/riscv32im/bin\)配置到环境变量中,在JupyterNotebook中执行如下代码

import os

path = os.environ['PATH'].split()

riscv_path = '/opt/riscv32im/bin'

if(riscv_path not in path):

print('Updating /etc/environment file... ',end="")

!sed -i 's/PATH=\"\(.*\)\"/PATH=\"\/opt\/riscv32im\/bin:\1\"/' /etc/environment

print('done')

else:

print("/etc/environment file already updated")

显示 Updating /etc/environment file… done即配置完成。

重启PYNQ-Z2:

```

shutdown -r now #如在JupyterNotebook中,前面需要加感叹号!

```

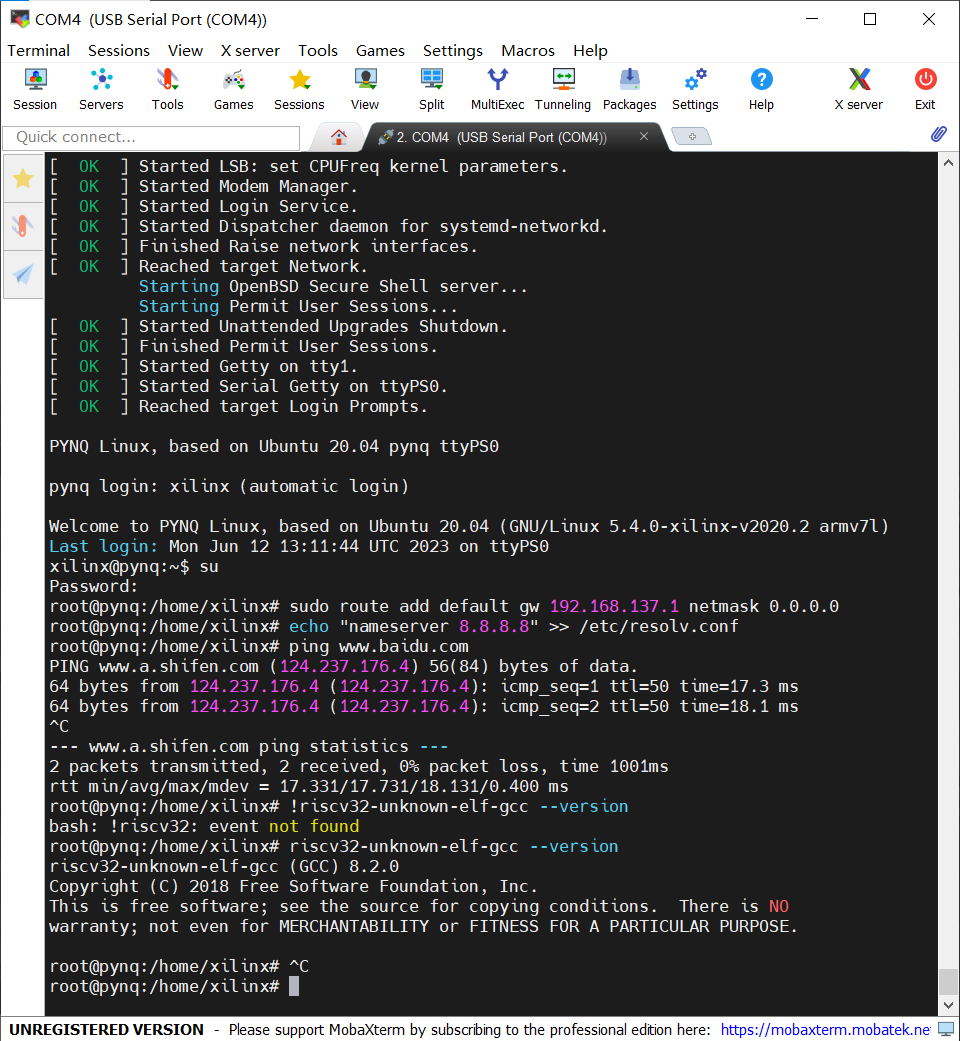

重启后确认RISC-V工具链已成功安装

```

riscv32-unknown=elf-gcc --version

```

显示版本号即成功安装

4.测试

在\(home/xilinx/RISC-V-On-PYNQ/riscvonpynq/picorv32/tut/\)目录下创建tutorial.py文件,文件内容如下

from pynq import Overlay, GPIO, Register

import os

import inspect

from riscvonpynq.Processor import BramProcessor

#--------

class TutorialOverlay(Overlay):

"""Overlay driver for the PicoRV32 bram Overlay

Note

----

This class definition must be co-located with the .tcl and .bit

file for the overlay for the search path modifications in

riscvonpynq.Overlay to work. __init__ in riscvonpynq.Overlay uses

the path of this file to search for the .bit file using the

inspect package.

"""

pass

class TutorialProcessor(BramProcessor):

"""Hierarchy driver for the PicoRV32 BRAM Processor

Note

----

In order to be recognized as a RISC-V Processor hierarchy, three

conditions must be met: First, there must be a PS-Memory-Mapped

Block RAM Controller where the name matches the variable

_bram. Second, the hierarchy name (fullpath) must equal the

variable _name. Finally, there must be a GPIO port with the name

_reset_name.

Subclasses of this module are responsible for setting _name (The

name of the Hierarchy), _bits (Processor bit-width), _proc

(Processor Type Name)

This class must be placed in a known location relative to the

build files for this processor. The relative path can be modified

in __get_path.

"""

_name = 'tutorialProcessor'

_proc = 'picorv32'

_bits = 32

@classmethod

def checkhierarchy(cls, description):

return super().checkhierarchy(description)

def __get_path(self):

"""Get the directory path of this file, or the directory path of the

class that inherits from this class.

"""

# Get file path of the current class (i.e. /opt/python3.6/<...>/stream.py)

file_path = os.path.abspath(inspect.getfile(inspect.getmodule(self)))

# Get directory path of the current class (i.e. /opt/python3.6/<...>/stream/)

return os.path.dirname(file_path)

def __init__(self, description, *args):

"""Return a new Processor object.

Parameters

----------

description : dict

Dictionary describing this processor.

"""

build_path = os.path.join(self.__get_path(), "build")

reset_value = 0

super().__init__(build_path, reset_value, description, *args)

在\({home/xilinx/RISC-V-On-PYNQ/riscvonpynq/picorv32/tut/}\)目录下创建__init__.py文件,文件内容如下

from . import tutorial

from . import build

将../bram/build拷贝到../tut/build中

在JupyterNotebook中执行以下代码设置当前工作路径为\(home/xilinx/RISC-V-On-PYNQ\)

import os

os.chdir("/home/xilinx/RISC-V-On-PYNQ/")

print(os.getcwd())

执行下面代码导入Overlay

import sys

sys.path.insert(0, '/home/xilinx/RISC-V-On-PYNQ/riscvonpynq/picorv32/')

from tut.tutorial import TutorialOverlay

overlay = TutorialOverlay("/home/xilinx/RISC-V-On-PYNQ/riscvonpynq/picorv32/tut/tutorial.bit")

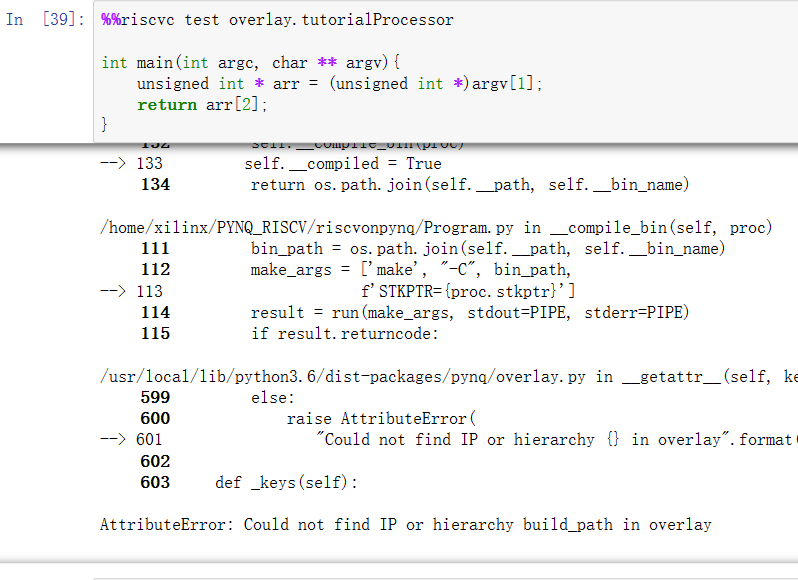

若没有报错执行以下代码,进行移植的测试

%%riscvc test overlay.tutorialProcessor

int main(int argc, char ** argv){

unsigned int * arr = (unsigned int *)argv[1];

return arr[2];

}

但在这里我一直遇到下图的报错,问了很多人都没能解决

如果有大佬做过这个项目,还请方便的话指点俺一下下つ﹏⊂,阿里嘎多!

PicoRV32-on-PYNQ-Z2: An FPGA-based SoC System——RISC-V On PYNQ项目复现的更多相关文章

- ARM、MCU、DSP、FPGA、SOC各是什么?区别是什么?(转)

ARM ARM处理器是Acorn计算机有限公司面向低预算市场设计的第一款RISC微处理器.更早称作Acorn RISC Machine.ARM处理器本身是32位设计,但也配备16位指令集,一般来讲比等 ...

- 【RS】Deep Learning based Recommender System: A Survey and New Perspectives - 基于深度学习的推荐系统:调查与新视角

[论文标题]Deep Learning based Recommender System: A Survey and New Perspectives ( ACM Computing Surveys ...

- 三叔学FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

- FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

- 论文笔记: Deep Learning based Recommender System: A Survey and New Perspectives

(聊两句,突然记起来以前一个学长说的看论文要能够把论文的亮点挖掘出来,合理的进行概括23333) 传统的推荐系统方法获取的user-item关系并不能获取其中非线性以及非平凡的信息,获取非线性以及非平 ...

- filebench - File system and storage benchmark - 模拟生成各种各样的应用的负载 - A Model Based File System Workload Generator

兼容posix 接口的文件系统中我们不仅要测试 posix 接口是否兼容.随机读,随机写,顺序读,顺序写等读写模式下的性能.我们还要测试在不同工作负载条件下的文件系统的性能的情况:Filebench ...

- SoC FPGA开发板的FPGA配置数据下载和固化

小梅哥编写,未经许可,严禁用于任何商业用途 2018年7月2日星期一 soc fpga的烧写和固化方式与传统的纯fpga固化方式即存在形式上的相同,也存在细节上的差异,特整理此文. AC501-So ...

- Intel Cyclone SoC FPGA介绍

3.1 Intel Cyclone SoC FPGA介绍 3.1.1 SoC FPGA的基本概念 Intel Cyclone V SoC FPGA是Intel PSG(原Altera)于2013年发布 ...

- 谈谈IC、ASIC、SoC、MPU、MCU、CPU、GPU、DSP、FPGA、CPLD

IC (integrated circuit) 集成电路:微电路.微芯片.芯片:集成电路又分成:模拟集成电路(线性电路).数字集成电路.数/模混合集成电路: 模拟集成电路:产生.放大.处理各种模拟信号 ...

- 【资讯】天啦鲁,这十余款创客设计居然由FPGA搞定 [转]

按理说‘高大上’的FPGA,多出现在航天航空(如火星探测器).通信(如基站.数据中心).测试测量等高端应用场景.但麦迪却也发现,近期,在很多创客的作品内部都有FPGA的影子.这或许也从侧面看出,打从总 ...

随机推荐

- 全网最详细中英文ChatGPT-GPT-4示例文档-人工智能助手从0到1快速入门——官网推荐的48种最佳应用场景(附python/node.js/curl命令源代码,小白也能学)

目录 Introduce 简介 setting 设置 Prompt 提示 Sample response 回复样本 API request 接口请求 python接口请求示例 node.js接口请求示 ...

- day118:MoFang:根据激活/未激活的状态分别显示树桩&种植植物&解锁树桩&化肥/修剪/浇水/宠物粮小图标数字的显示

登录 1.根据激活状态和未激活状态分别显示树桩 2.用户使用植物道具进行果树种植 3.解锁树桩 4.化肥/修剪/浇水/宠物粮小图标显示 种植栏的功能实现 1. 客户端需要的植物相关参数: 总树桩数量, ...

- CVE-2022-21454:漏洞整改mysql5.7.37升级至5.7.38 tar包升级

问题描述:对数据库服务器进行漏扫,发现一些中高位漏洞需要整改,有些数据库需要升级到最新版 漏洞修改指导链接:https://www.oracle.com/security-alerts/cpuapr2 ...

- VScode连接GPU服务器进行深度学习

VScode连接GPU服务器进行深度学习 最近用台式机跑一些小的深度学习项目,发现越来越慢了,由于一些原因,有时候需要我进行现场作业但是我的笔记本是轻薄本(Thinkpad YYDS)不带显卡,百 ...

- Python_13 接口测试openpyxl和表操作

一.openpyxl 安装 pip install openpyxl 在Terminal中输入 excel操作步骤 找到目标excel 打开 读取数据.编辑excel单元格 保存 关闭 open ...

- antv x6 神奇的图片边框

昨天才把html节点中的图片转成base格式的,今天就发现一个用户体验的问题:那么是啥呢?就是我从左侧的树形菜单中拖拽节点的时候(鼠标按下也是同样问题),发现节点的图片区域那里会出现一个边框,持续时间 ...

- [Pytorch框架] 2.5 循环神经网络

文章目录 2.5 循环神经网络 2.5.1 RNN简介 RNN的起因 为什么需要RNN RNN都能做什么 2.5.2 RNN的网络结构及原理 RNN LSTM GRU 2.5.3 循环网络的向后传播( ...

- Word中使用ChatGPT,写文档如有神助

[部署教程]国内网络可用,最强 ChatGPT 学术论文写作工具原创****付费 简介 Word GPT Plus 是一个集成了 chatGPT 模型的 Word 插件.它允许你基于你在文档中写的内容 ...

- Yolov5 根据自己的需要更改 预测框box和蒙版mask的颜色

1.首先找到项目中 utils/plots.py 文件,打开该代码 将原来的 Colors类注释掉(或删掉),改成如下Colors类 class Colors: def __init__(self): ...

- 2022-11-26:给定一个字符串s,只含有0~9这些字符 你可以使用来自s中的数字,目的是拼出一个最大的回文数 使用数字的个数,不能超过s里含有的个数 比如 : 39878,能拼出的最大回文数是

2022-11-26:给定一个字符串s,只含有0~9这些字符 你可以使用来自s中的数字,目的是拼出一个最大的回文数 使用数字的个数,不能超过s里含有的个数 比如 : 39878,能拼出的最大回文数是 ...