从头学起Verilog(二):时序逻辑基础与回顾

引言

时序逻辑对于数字电路设计十分重要,本文针对数字电路中的时序逻辑部分进行了系统的回顾。

存储器件

由于时序逻辑的输出不但受当前输入影响,还受之前的输入的影响,所以需要有存储单元对以前的输入进行存储。

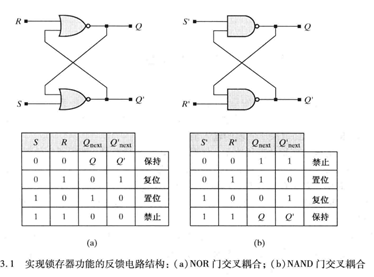

SR锁存器(set-reset)---电平敏感器件

实际在Verilog中,很多情况应该避免使用锁存器,也应该避免无意中被综合成锁存器。

NOR门交叉耦合的锁存器,一方面输入11时,输出逻辑不是互反的;另一方面逻辑从11->00引发竞争,会导致输出无法预测所以避免11;

NAND门交叉耦合的苏存取,输入00时,输出逻辑不是互反的,而且从00->11引发竞争,所以避免00。

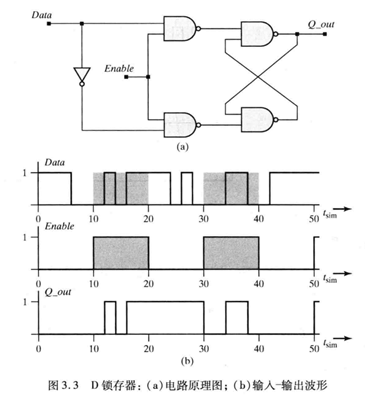

透明锁存器

透明锁存器也成为D锁存器,通过增加一级带使能的与非门电路,实现了输入是否影响到输出的控制。

D锁存器输入反向后连接到另一端,避免了禁止的输入和不稳定的输出

触发器

边沿敏感器件,数据的动作通过某个信号的边沿进行同步。

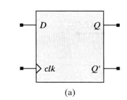

D触发器

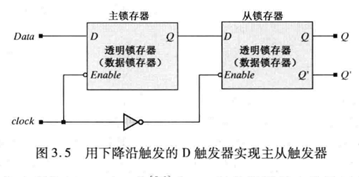

主从触发器

可通过两个透明锁存器实现。当clock变为低电平时,Data通过主锁存器到达Q1;clock由低电平变为高电平时,主锁存器锁存,Data通过从锁存器到达输出。

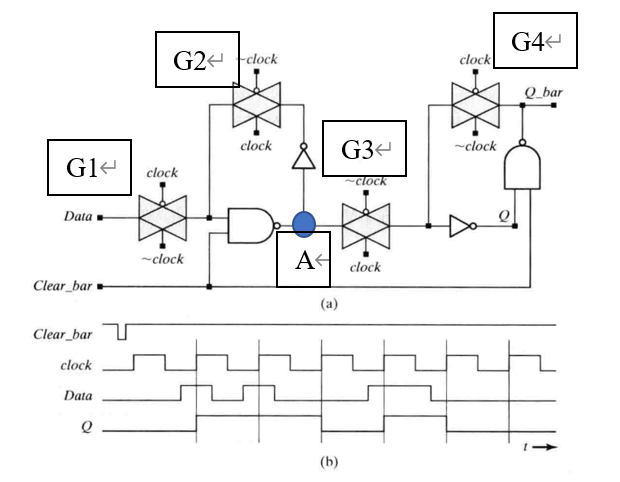

主从触发器还可以通过CMOS工艺中的传输门(TG Gate)实现

分析:

1、清零状态,A点为1,Q_bar为1,Q为0

2、Clock低电平时,G1开,G2关,G3关,G4开,Data信号输入到主锁存器输入端。Clock上升沿来临,G1关,G2开实现触发和锁存。

3、G2开的同时G3开,A点信号穿过G3,取反后到达Q;G4实现输出锁存。

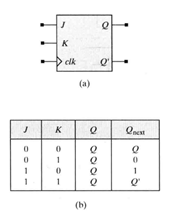

其他触发器

JK触发器,00保持,11翻转,10置数,01清零。

T触发器,将JK触发器的JK端连接在一起,实现输入0保持,输入1翻转。

总线与三态器件

总线:连接系统中多个功能单元多条连线的信号通道。大大减小系统物理资源和板级空间。

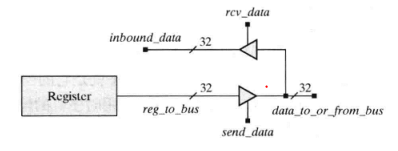

三态器件:硬件上实现了总线和电路中的动态接口,使能时作为数据通路,否则开路(Hi-Z)。

三态器件用于电路与总线隔离,如图。send_data为高时,电路向总线输出数据;rcv_data为高时,从总线接收数据。

时序机设计和状态转移图

时序机

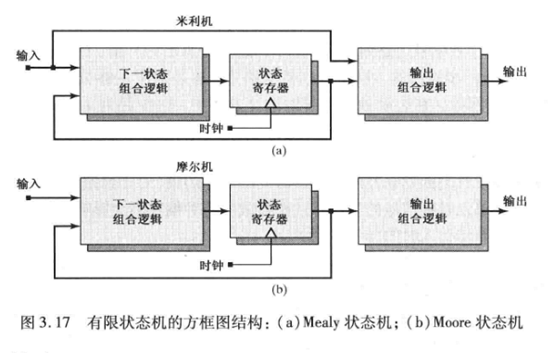

时序机的下一步行为或动作由当前输入和当前状态描述。

Mealy状态机下一状态取决于当前输入和当前状态。

Moore状态机下一状态取决于当前输入和当前状态,但输出仅取决与当前状态。

比较

1、Moore机比Mealy机多出一个延迟周期(Mealy机能够对输入进行实时监测),但输入信号的噪声可能对输出的信号产生一定影响。

2、一般来说,Moore型状态机状态多一些。

状态转移图(个人觉得这一部分很关键,但自己也没有十分掌握好,后面通过理解加深逐渐来补充这部分内容吧)

这里以一个例子来说明手工方法来设计状态机的步骤:

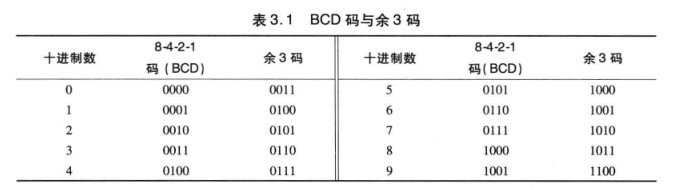

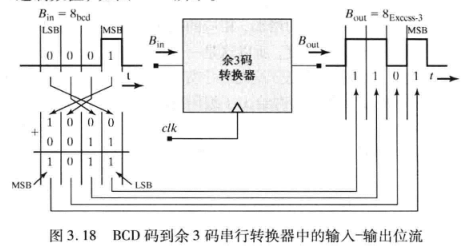

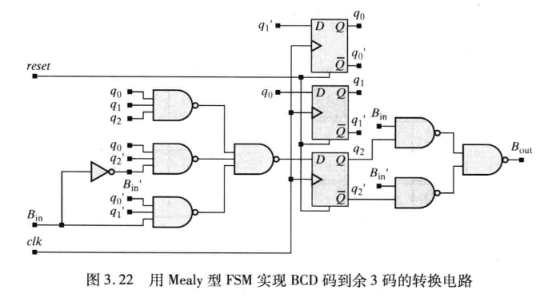

例:BCD码到余3码的转换(余3码是在BCD码的基础上加3,得到的自补码)

在设计时需要注意的是,位流先从最低位输入和输出。

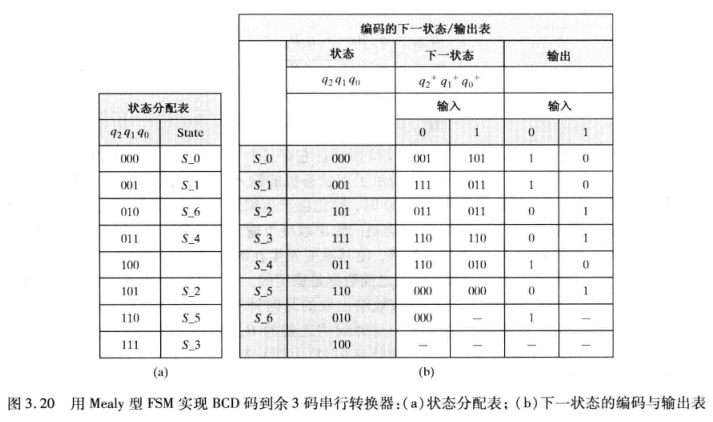

根据表得到状态转移图(这部分自己做的也不够好)。需要列出状态和状态转移关系,合并等价状态,根据以下原则分配对应码字代表状态。

状态编码分配原则:

1、 某个特定的输入,两个状态跳到同一个状态,则分配相邻码字

2、 相邻状态分配相邻码字

3、 某个特定输入,有相同的输出,分配相邻码字

根据状态转移图并分配状态后,得到“当前状态-不同输入下下一状态-不同输入下输出”的表格。

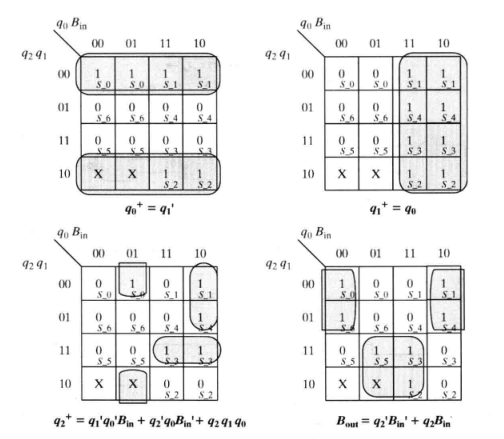

根据上表,分别画出“下q2q1q0Bout的下一状态-q2q1q0qin的当前状态”卡诺图,得到q2q1q0qin的布尔表达式。

根据卡诺图得到的四个表达式,画出对应的硬件实现。利用三个触发器,分别存储三个状态位。其余利用组合逻辑实现。

状态化简和等价状态

等价状态:时序机两个状态对所有可能的输入都有相同的输出和下一状态(即状态表两个状态有关的行是完全相同的),则称为两个状态等价。

删除并保留仅一个等价状态可使得状态转移图得到化简。但两个状态行不完全相同也可能是等价状态(即需要某些等价消除后才能看出该两个状态行等价)。

总结

本文介绍了数字电路中时序逻辑部分的基础内容,但很大一部分仍需要练习和补充。如果有看客发现错误希望大家能够指出,大家共同进步!

从头学起Verilog(二):时序逻辑基础与回顾的更多相关文章

- 从头学起Verilog(三):Verilog逻辑设计

引言 经过了组合逻辑和时序逻辑的复习,终于到了Verilog部分.这里主要介绍Verilog一些基础内容,包括结构化模型.TestBench编写和仿真.真值表模型. 这部分内容不多,也都十分基础,大家 ...

- 从头学起Verilog(一):组合逻辑基础与回顾

引言 该部分主要回顾了本科时数字电路中组合逻辑电路部分,内容相对简单和基础. 内容主要包括:布尔代数相关知识,卡诺图,最大项与最小项,竞争和冒险以及一些常见模块 数字电路中的逻辑 组合逻辑:输出可以表 ...

- 从头学pytorch(十二):模型保存和加载

模型读取和存储 总结下来,就是几个函数 torch.load()/torch.save() 通过python的pickle完成序列化与反序列化.完成内存<-->磁盘转换. Module.s ...

- 从头开始学JavaScript (十二)——Array类型

原文:从头开始学JavaScript (十二)--Array类型 一.数组的创建 注:ECMAscript数组的每一项都可以保存任何类型的数据 1.1Array构造函数 var colors = ne ...

- 我的 FPGA 学习历程(09)—— 时序逻辑入门

讲到这篇时,组合逻辑就告一段落了,下面是一些总结: 描述组合逻辑时,always 语句中的敏感信号列表中需要列出全部的可能影响输出的变量 描述组合逻辑时,always 语句中的赋值总是使用阻塞赋值符号 ...

- FPGA学习笔记(六)—— 时序逻辑电路设计

用always@(posedge clk)描述 时序逻辑电路的基础——计数器(在每个时钟的上升沿递增1) 例1.四位计数器(同步使能.异步复位) // Module Name: coun ...

- Linux 从头学 01:CPU 是如何执行一条指令的?

作 者:道哥,10+年的嵌入式开发老兵. 公众号:[IOT物联网小镇],专注于:C/C++.Linux操作系统.应用程序设计.物联网.单片机和嵌入式开发等领域. 公众号回复[书籍],获取 Linux. ...

- verilogHDL设计中的同步时序逻辑

引用自夏宇闻教授 1.同步时序逻辑: 是指表示状态的寄存器组的值只能在唯一确定的触发条件发生改变. 只能由时钟的正跳变沿或者负跳变沿触发的状态机就是一例,always@(posedge clk). 1 ...

- Centos7系统配置上的变化(二)网络管理基础

原文 Centos7系统配置上的变化(二)网络管理基础 上篇简单介绍了CentOS 7 在服务和网络方面的一点变化,先前很多烂熟于心的操作指令已经不适用了,不管是否习惯,总要接受.熟悉这些变化. 写上 ...

随机推荐

- day67:Vue:es6基本语法&vue.js基本使用&vue指令系统

目录 Vue前戏:es6的基本语法 1.es6中的let特点 1.1.局部作用域 1.2.不存在变量提升 1.3.不能重复声明 1.4.let声明的全局变量不从属于window对象,var声明的全局变 ...

- day46 Pyhton 数据库Mysql 03

一内容回顾 存储引擎:主要描述的是数据存储的不同方式 innodb 支持事务\支持外键\行级锁\聚焦索引 myisam 不支持事务\不支持外键\表级锁\非聚焦索引 memory 只能在内存中存储表数据 ...

- MVC-WebApi配置 Swagger(Web Api可视化文档)

一.从创建MVC WebApi开始 第一步创建MVC WebApi就创建好了,接下来就进入正题,上干货 ================================================ ...

- ScanTailor-ScanTailor 自动矫正图像歪斜

ScanTailor 自动矫正图像歪斜 下面操作某一步可能会卡住,别担心情等待它处理完毕. New Project ... Input Directory "Browse" ...

- filebeat- 配置

wget https://mirrors.huaweicloud.com/filebeat/7.9.1/filebeat-7.9.1-linux-x86_64.tar.gz tar -zxvf fil ...

- spring cloud:通过client访问consul集群(spring cloud hoxton sr8 / spring boot 2.3.4)

一,为什么要搭建consul的client? 1,网上的很多资料,访问consul时用的单机模式,这样是不可以直接在生产环境中使用的 还有一些资料,搭建了consul的集群后,直接访问集群中的某一个i ...

- 第二十四章 Find命令详细介绍

一.Find 概述 可以根据文件的名称.文件大小.文件的修改时间.文件的类型.文件的权限.文件的属主属组.文件的目录层级进行查找 Find的语法: find [-H] [-L] [-P] [-Olev ...

- Python可迭代对象和迭代器对象

可迭代对象iterable: 对象字面意思:Python中一切皆对象.一个实实在在存在的值. 可迭代:更新迭代.迭代是一个重复的过程,每次重复是基于上一次的结果而继续的,每次都有新的内容. 可迭代对象 ...

- Linux基础命令列表

命令列表 A alias apt apt-get arp -n -s arping ab B bc basename bash -n -x bzip2 bunzip2 bzcat blkid brct ...

- (静默安装)Cent OS 6_5(x86_64)下安装Oracle 11g

Cent OS 6_5(x86_64)下安装Oracle 11g 1 硬件要求 1.1 内存 & swap 物理内存不少于1G 硬盘可以空间不少于5G swap分区空间不少于2G Mini ...