用嵌入式块RAM IP核配置一个双口RAM

本次设计源码地址:http://download.csdn.net/detail/noticeable/9914173

实验现象:通过串口将数据发送到FPGA 中,通过quartus II 提供的in system memory content editor 工具查看RAM中接收到的数据,当需要是,按下按键KEY0,将FPGA 的RAM 中存储的数据通过串口发送出去。

知识点:

(1)存储器IP核的使用(2)in system memory content editor 内存查看工具的使用

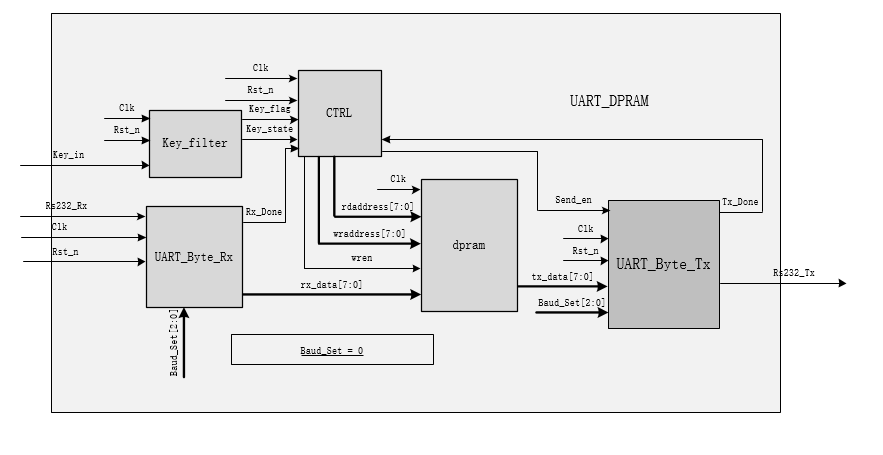

系统结构框图如下,如何绘制在http://www.cnblogs.com/noticeable/p/7248404.html可以进行查看

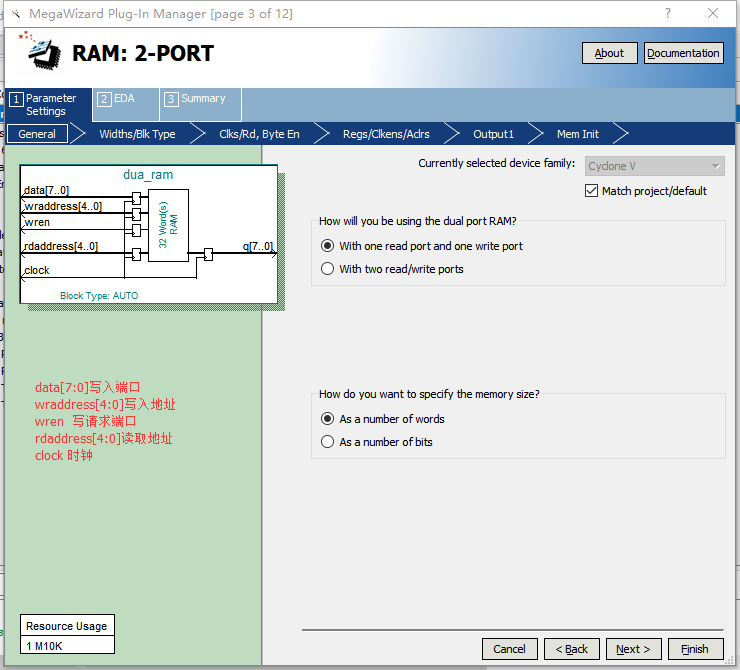

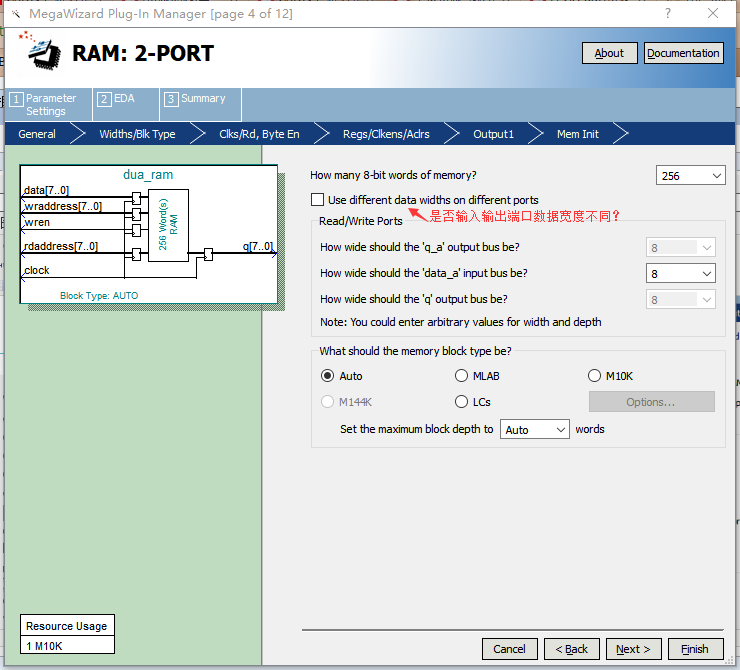

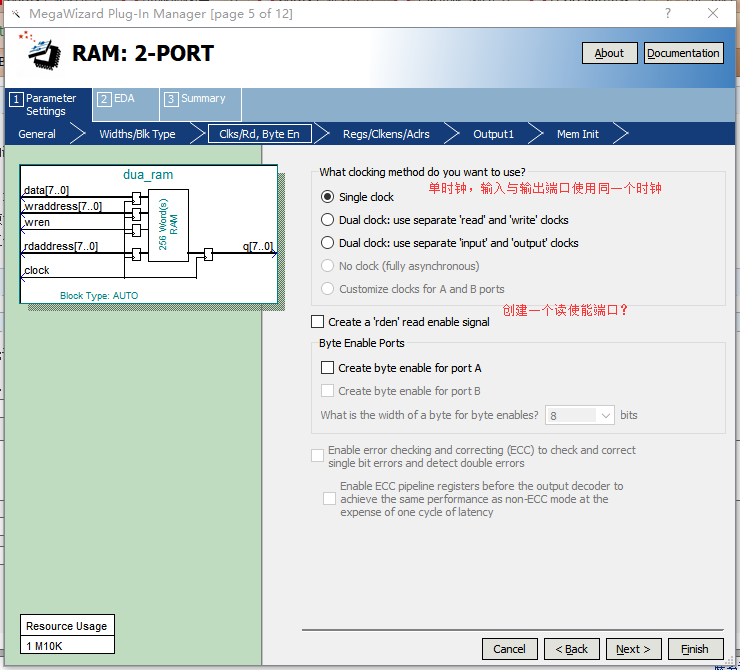

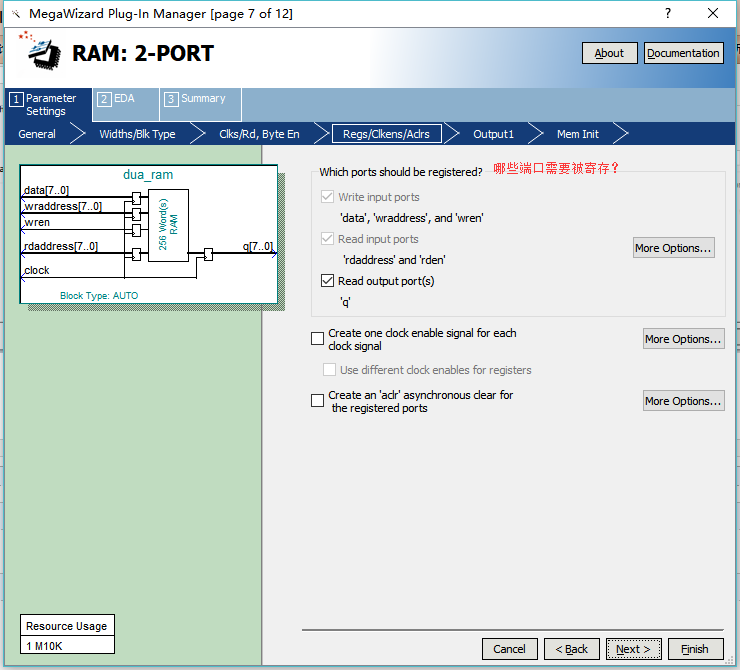

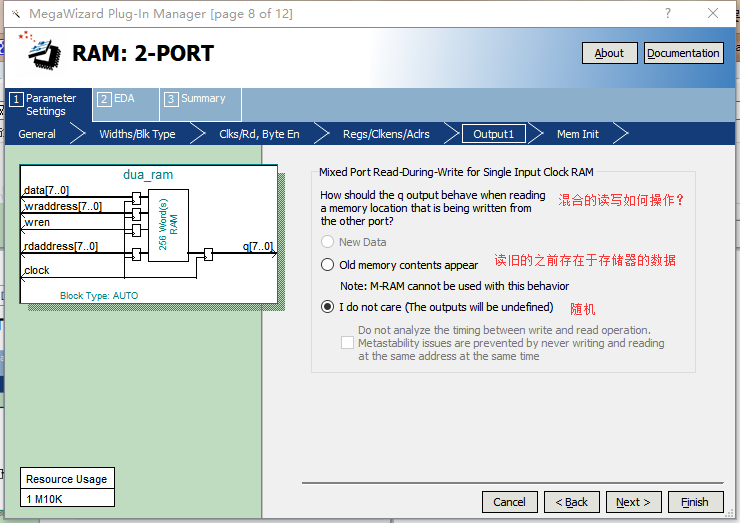

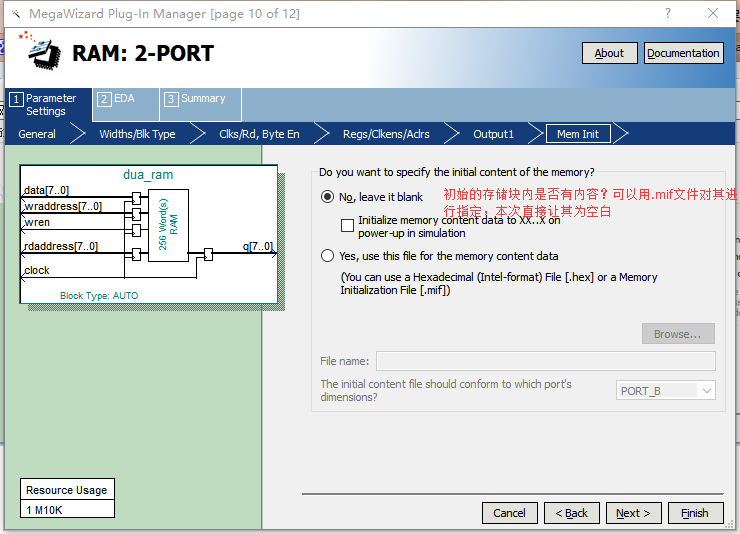

设计过程:复制之前写的uart工程,打开,添加menmoryIP核

然后直接next,直到finish,此时就可以将IP核添加完毕了。

然后直接next,直到finish,此时就可以将IP核添加完毕了。

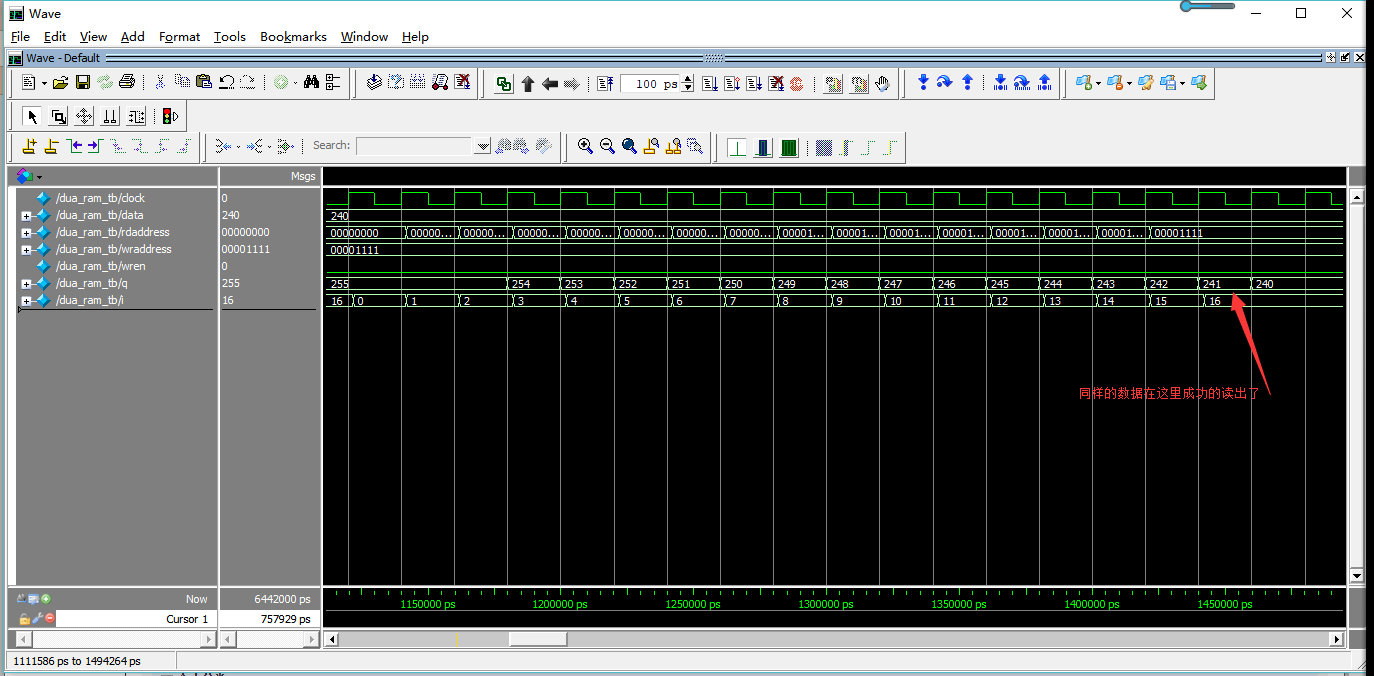

直接将IP核生成的文件设置为顶层文件,编写testbench文件对其进行仿真

`timescale 1ns/1ns

`define clock_period module dua_ram_tb;

reg clock;

reg [:]data;

reg [:]rdaddress;

reg [:]wraddress;

reg wren;

wire [:]q;

integer i;

dua_ram dua_ram0(

.clock(clock),

.data(data),

.rdaddress(rdaddress),

.wraddress(wraddress),

.wren(wren),

.q(q)

);//端口连接 initial clock=;

always#(`clock_period/)clock=~clock; initial begin

data=;

rdaddress=;

wraddress=;

wren=;

#(`clock_period*+);

for(i=;i<=;i=i+)begin // 写操作

wren=;

data=-i;

wraddress=i;

#(`clock_period);

end

wren=;

#(`clock_period*+);//延迟一段时间后进行读操作

for(i=;i<=;i=i+)begin // 读操作

rdaddress=i;

#(`clock_period);

end

#;

$stop;

end

endmodule

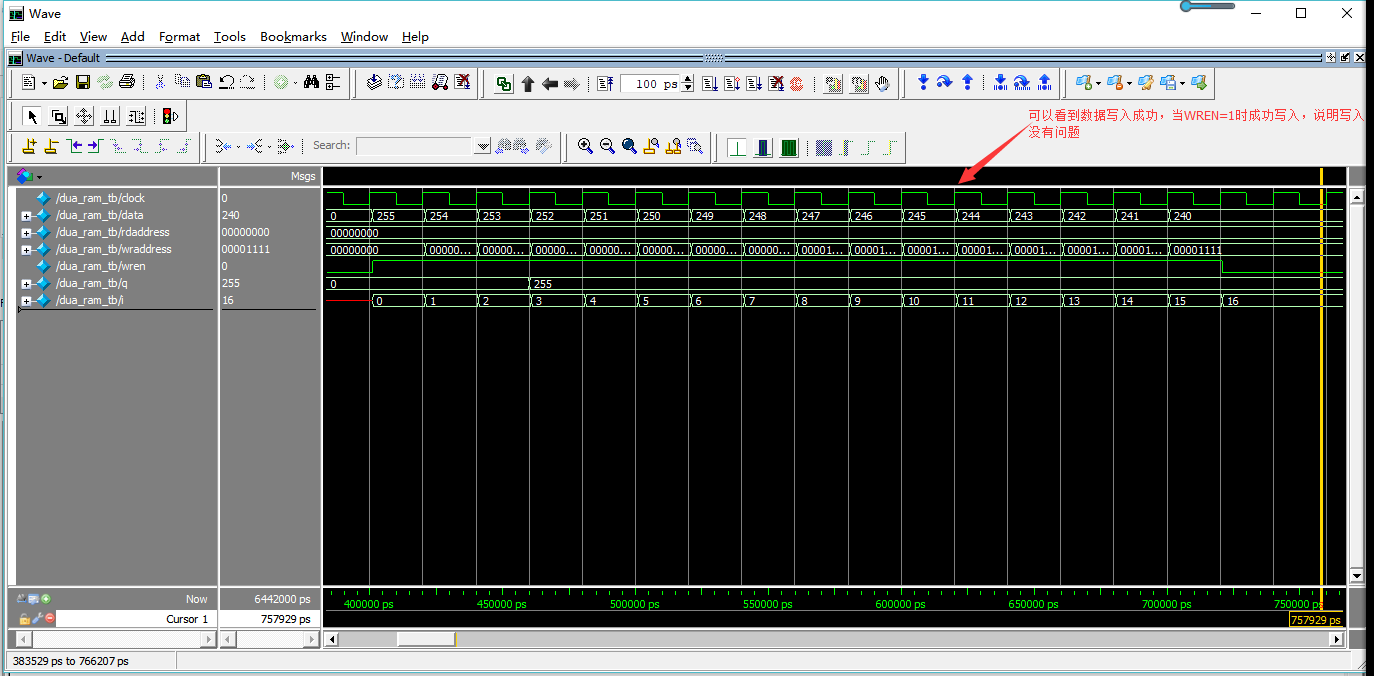

设置仿真脚本,点击仿真,进行前仿

仿真完了,可以对双口RAM有一个基本了解了,下面就将其添加到之前写的uart工程中

新建一个uart_dpram.v文件,并设置其为顶层文件,代码按照结构图进行编辑如下:

module uart_dpram(

clk,

rst_n,

key_in,

rs232_rx,

rs232_tx);

input clk;

input rst_n;

input key_in;

input rs232_rx; //串口读取端口

output rs232_tx; //串口写出端口 wire key_flag; //按键检测标志

wire key_state; //按键状态标志

wire rx_done; //读取完成标志

wire tx_done; //写出完成标志

wire send_en; //写出使能

wire [:]rdaddress,wraddress; //读地址和写地址

wire wren; //写入使能

wire [:]rx_data,tx_data; //待读取数据与发送数据 uart_tx uart_tx_a(

.clk(clk),

.rst_n(rst_n),

.send_en(send_en),

.baud_set('d0),

.tx_done(tx_done),

.rs232_tx(rs232_tx),

.data_byte(tx_data),

.uart_state()

); uart_rx uart_rx_a(

.clk(clk),

.rs232_rx(rs232_rx),

.baud_set('d0),

.rst_n(rst_n),

.data_byte(rx_data),

.rx_done(rx_done)

);

key_filter key_filter_a(

.clk(clk),

.rst_n(rst_n),

.key_in(key_in),

.key_flag(key_flag),

.key_state(key_state)

); dua_ram dua_ram_a(

.clock(clk),

.data(rx_data), //存储器入口是读取的数据

.rdaddress(rdaddress),

.wraddress(wraddress),

.wren(wren),

.q(tx_data) //存储器的出口是要写出的数据

);//端口连接

ctrl ctrl_a(

.clk(clk),

.rst_n(rst_n),

.key_flag(key_flag),

.key_state(key_state),

.rx_done(rx_done),

.tx_done(tx_done),

.rdaddress(rdaddress),

.wraddress(wraddress),

.wren(wren),

.send_en(send_en)

); endmodule

如代码中所说,ctrl模块没有定义,编译肯定是会报错的,下面继续编写ctrl 模块,新建一个ctrl.v文件,编辑如下:

module ctrl(

clk,

rst_n,

key_flag,

key_state,

rx_done,

tx_done,

rdaddress,

wraddress,

wren,

send_en

);//控制模块 input clk;

input rst_n;

input key_flag;

input key_state;

input rx_done;

input tx_done;

output reg[:]rdaddress;

output reg[:]wraddress;

output wren; //写入使能信号

output reg send_en; //发送使能 assign wren=rx_done; //读取完成的信号即可以写入了

reg do_send; //发送标志

reg r0_send_done,r1_send_done; //发送缓冲寄存器 always@(posedge clk or negedge rst_n)//写地址

if(!rst_n)

wraddress<='d0;

else if(rx_done) //每读取完一次,写入地址+1

wraddress<=wraddress+'d1;

else

wraddress<=wraddress; always@(posedge clk or negedge rst_n)

if(!rst_n)

do_send<=;

else if(key_flag&&!key_state) //如果按键按下一次,发送状态改变一次

do_send<=~do_send; always@(posedge clk or negedge rst_n)//读地址

if(!rst_n)

rdaddress<='d0;

else if(do_send&&tx_done) //发送状态为发送,且1byte数据已经发送完成了,则读地址+1

rdaddress<=rdaddress+'d1; always@(posedge clk or negedge rst_n)///ram读有两拍的延迟,所以加两级寄存器对发送使能进行缓存

if(!rst_n) begin

r0_send_done<='b0;

r1_send_done<='b0;

end

else begin

r0_send_done<=(do_send&&tx_done);

r1_send_done<=r0_send_done;

end always@(posedge clk or negedge rst_n)//发送使能

if(!rst_n)

send_en<=;

else if(key_flag&&!key_state)

send_en<='b1;

else if(r1_send_done)

send_en<=;

else

send_en<=; endmodule

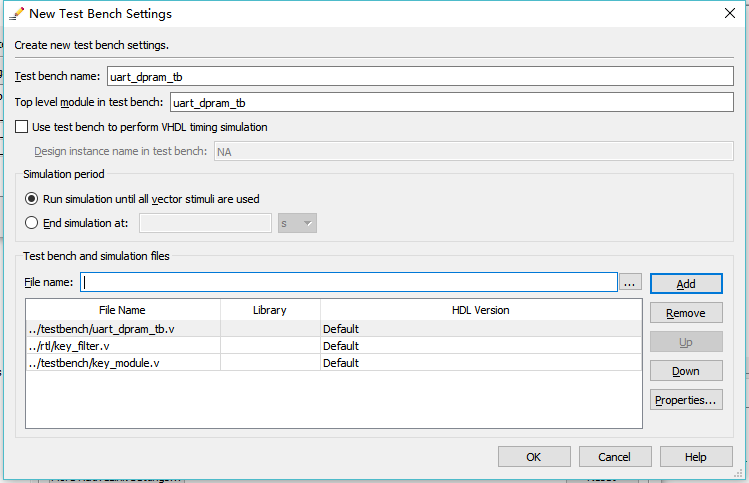

编写testbench文件进行仿真,将test9中的keymodule 复制到本工程的testbench文件夹下,并添加到工程中

`timescale 1ns/1ns

`define clock_period

module uart_dpram_tb;

reg clk;

reg rst_n;

wire key_in;

wire rs232_rx;

wire rs232_tx;

wire tx_done;

reg [:]data_byte_t;

reg send_en;

wire [:]baud_set;

reg press; assign baud_set = 'd0;

uart_dpram uart_dpram_1(

.clk(clk),

.rst_n(rst_n),

.key_in(rst_n),

.rs232_rx(rs232_rx),

.rs232_tx(rs232_tx)); uart_tx uart_tx1(

.clk(clk),

.rst_n(rst_n),

.send_en(send_en),

.baud_set(baud_set),

.tx_done(tx_done),

.rs232_tx(rs232_rx),

.data_byte(data_byte_t),

.uart_state()

); key_module key_module1(

.press(press),

.key(key_in)

);

initial clk=;

always#(`clock_period/) clk=~clk;

//发送数据

initial begin

rst_n = 'b0;

press = ;

data_byte_t = 'd0;

send_en = 'd0;

#(`clock_period*+)

rst_n='b1;

#(`clock_period*+) data_byte_t<='haa;

send_en<='d1;

#(`clock_period)

send_en<='d0; @(posedge tx_done)//等待传输完成的上升沿 #(`clock_period*)//重新发送

data_byte_t<='h55;

send_en<='d1;

#(`clock_period)

send_en<='d0;

@(posedge tx_done)//等待传输完成的上升沿

#(`clock_period*)//重新发送

data_byte_t<='hcc;

send_en<='d1;

#(`clock_period)

send_en<='d0; @(posedge tx_done)//等待传输完成的上升沿

#(`clock_period*)//重新发送

data_byte_t<='hff;

send_en<='d1;

#(`clock_period)

send_en<='d0; //按下按键读取发送出去的内容

@(posedge tx_done) #(`clock_period*); press = ;

#(`clock_period*)

press = ;

#(`clock_period*); end

endmodule

添加路径如下:

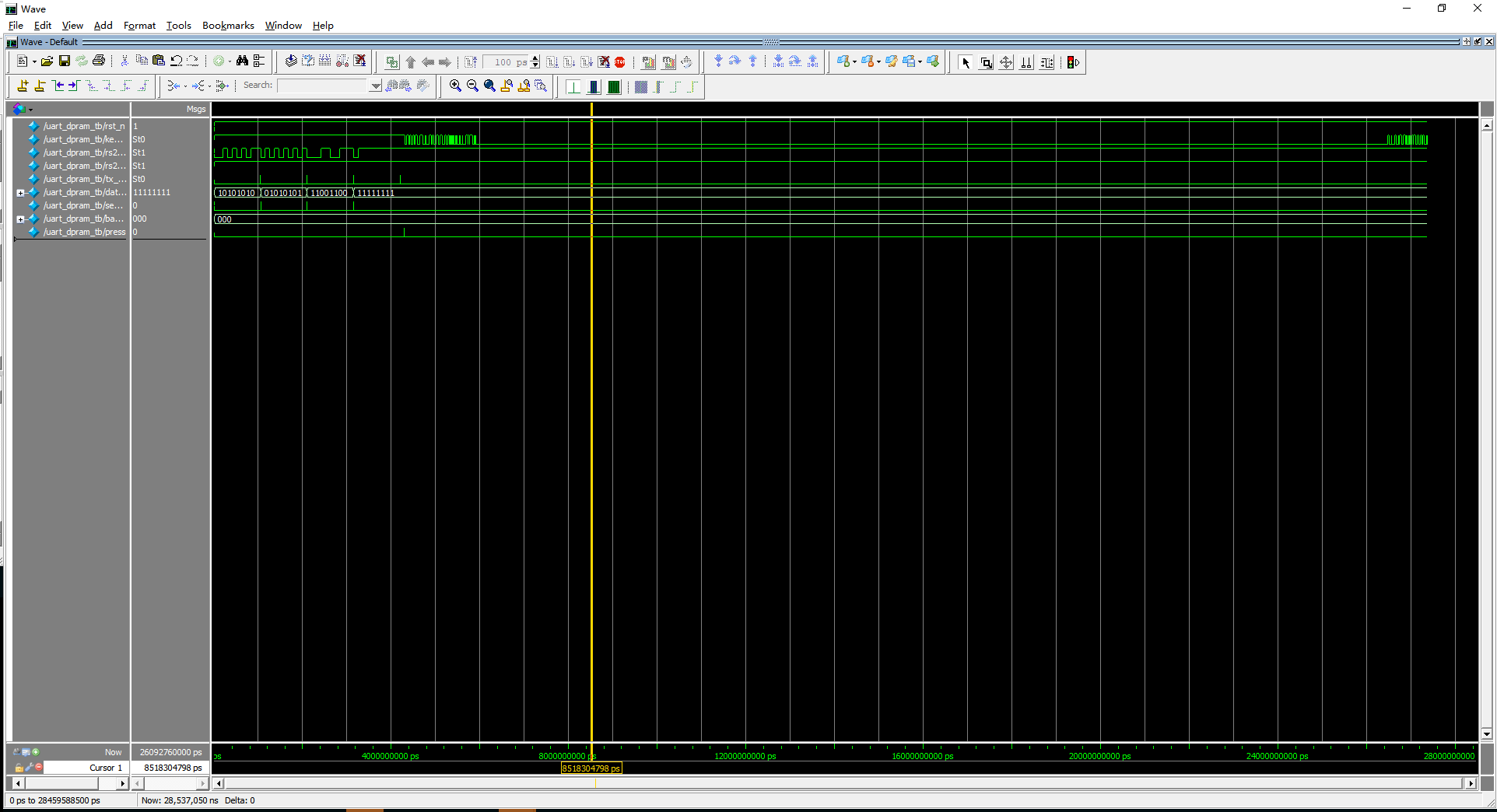

点击仿真,仿真结果如下

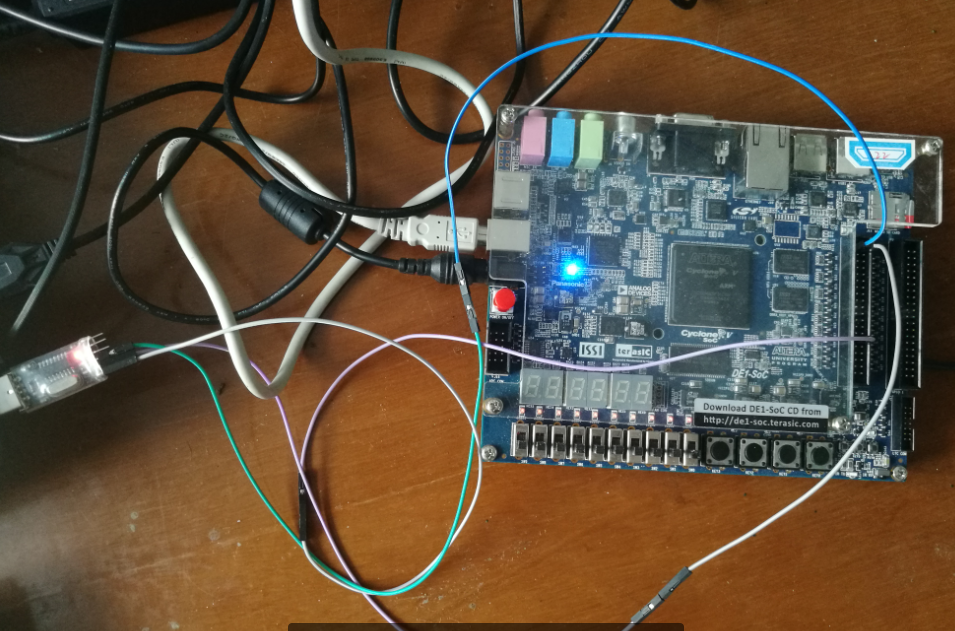

引脚配置,烧写程序,进行扳级验证,这里GPIO0_D0连接到USB_TTL的TXD,GPIO0_D1连接到USB_TTL 的RXD即可。

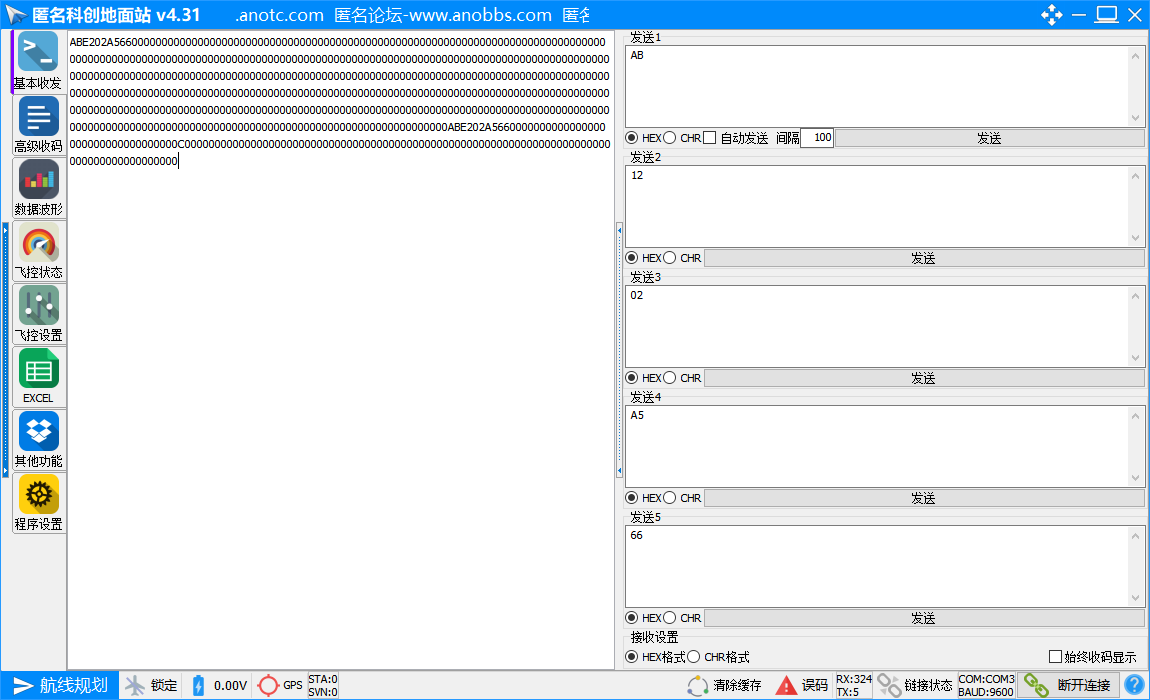

打开串口调试软件,连接USB-TTL模块,发送数据,按下按键KEY_1,FPGA不断把刚才发到ram中的数据读取出来,再按一下,停止发送,效果图如下所示

用嵌入式块RAM IP核配置一个双口RAM的更多相关文章

- 第7讲 SPI和RAM IP核

学习目的: (1) 熟悉SPI接口和它的读写时序: (2) 复习Verilog仿真语句中的$readmemb命令和$display命令: (3) 掌握SPI接口写时序操作的硬件语言描述流程(本例仅以写 ...

- SPI和RAM IP核

学习目的: (1) 熟悉SPI接口和它的读写时序: (2) 复习Verilog仿真语句中的$readmemb命令和$display命令: (3) 掌握SPI接口写时序操作的硬件语言描述流程(本例仅以写 ...

- 7 Series GTP IP核使用总结 IP核配置篇

FPGA内嵌收发器相当于以太网中的PHY芯片,但更灵活更高效,线速率也在随着FPGA芯片的发展升级.本文对7系列FPGA内部高速收发器GTP IP核的配置和使用做些简单的总结,以备后续回顾重用.本文是 ...

- 单口 RAM、伪双口 RAM、真双口 RAM、单口 ROM、双口 ROM 到底有什么区别呢?

打开 IP Catalog,搜索 Block Memory Generator,即可看到其 Memory Type 可分为 5 中,分别是单口 RAM(Single Port RAM).伪双口 RAM ...

- 双口RAM,值得研究

在FPGA设计过程中,使用好双口RAM,也是提高效率的一种方法. 官方将双口RAM分为简单双口RAM和真双口RAM. 简单双口RAM只有一个写端口,一个读端口. 真双口RAM分别有两个写端口和两个读端 ...

- FMC与FPGA双口ram通讯

硬件环境:ARM+FPGA通过FMC互联,STM32F767和 EP4CE15F23I7 FMC设置,STM的系统时钟HCLK为216MHz /* FMC initialization functio ...

- 单口RAM、双口RAM、FIFO

单口与双口的区别在于,单口只有一组数据线与地址线,因此读写不能同时进行.而双口有两组数据线与地址线,读写可同时进行.FIFO读写可同时进行,可以看作是双口. 双口RAM分伪双口RAM(Xilin ...

- 【iCore1S 双核心板_FPGA】例程十七:基于双口RAM的ARM+FPGA数据存取实验

实验现象: 核心代码: module DUAL_PORT_RAM( input CLK_12M, inout WR, input RD, input CS0, :]A, :]DB, output FP ...

- xilinx IP核配置,一步一步验证Xilinx Serdes GTX最高8.0Gbps

版权声明:本文为博主原创文章,未经博主允许不得转载. https://blog.csdn.net/u010161493/article/details/77658599 目录(?)[+] 之前 ...

随机推荐

- android toolbar效果3

Title居中,只有一个右边按钮 activity_main.xml: <?xml version="1.0" encoding="utf-8"?> ...

- Linux下编译安装FFmpeg

FFmpeg官网:http://www.ffmpeg.org 官网介绍 FFmpeg is the leading multimedia framework, able to decode, enco ...

- 一个linux 4.9,4.14内核的bbr带宽估计偏低问题

linux 4.9内核,bbr的带宽估计问题. 一个正常的bbr流量图: 对应的ttl图形: 一个异常的bbr流量图: 可以看出,异常的bbr流量图,出现了一个很低的带宽,且稳定在这个带宽10s左右, ...

- javascript隐式原型

上图是js原型关系图. javascript是一种基于对象的编程语言,但它与一般面向对象的编程语言不同,因为它没有class类的概念 什么是原型?? 我们每创建一个函数,它就会自带一个原型函数,这个原 ...

- ArcGIS自定义工具箱-清空工作空间

ArcGIS自定义工具箱-清空工作空间 联系方式:谢老师,135-4855-4328,xiexiaokui#qq.com 目的:删除工作空间里的要素类,栅格和独立表 使用方法: 例如"C:\ ...

- python re模块与正则表达式

首先要先继承re模块: import re re.findall() 方法 # 返回值为列表 \w 表示一个字符,为数字,字母,下滑线之一, \W匹配任意非数字,字母,下划线 print(re.fin ...

- centos7 安装php5.6

1.查看centos 版本 lsb_release -a LSB Version: :base-4.0-amd64:base-4.0-noarch:core-4.0-amd64:core-4.0-no ...

- Unity之AssetBundle打包

AssetBundle Resources:表示U3D自动将资源打成一个AssetBundle包,所有放在Resources下的文件夹都会打成一个AssetBundle包,资源非常大,Resource ...

- linux网络日志分析

1.清空日志的技巧 2.访问日志格式分析 3. web日志统计举例

- 框架和内嵌框架--->frameset 和 iframe 的文档对象

框架和内嵌框架分别用 HTMLFrameElemnt 和 HTMLIFrameElement 表示,它们在 DOM2 中有一个新属性----->contentDocument,是一个指针,表示框 ...