ARM_Core的处理器模式与寄存器,结构杂谈

ARM处理器的工作状态:ARM处理器有两种工作状态。在程序的执行过程中,处理器可以在两种工作状态之间切换,并且不影响

相应寄存器中的内容。

ARM状态,此时处理器执行32位对齐的ARM指令;BX指令,当操作数寄存器最低位为0时,进入ARM状态。

Thumb,此时处理器执行16位对齐的Thumb指令。BX指令,当操作数寄存器最低位为1时,进入Thumb状态。

BX(Branch Exchange):BX Rn; ##其中Rn可以是R0-R15中的任意一个。指令通过将寄存器Rn的内容拷贝到程序计数器PC

来完成4Gbyte的地址空间的跳转。

在进入异常中断后,ARM内核会自动切换到ARM状态,在异常中断处理程序入口的是ARM指令,

退出异常之后,根据异常之前的CPSR的值,来决定当前时arm状态还是thumb状态。

ARM处理器总是从ARM工作状态开始的。

ARM处理器的7中工作模式:

USE模式:正常用户模式。

FIQ模式:快速中断模式,支持高速数据传输。

IRQ模式:普通中断模式。

SVC模式:Supervisor模式,操作系统保护模式,处理软件中断swi,reset.

ABT模式:数据,指令中止模式。

UND模式:未定义模式,支持软件仿真。

SYS模式:系统模式,运行特权操作系统任务。

除用户模式之外的6中模式称为特权模式,特权模式下,程序可以访问所有的系统资源,可以任意的进行处理器模式的切换。

用户模式下不能访问一些受操作系统保护的系统资源,不能直接进行处理器模式切换,需要由应用程序产生异常处理。

特权模式中,除系统模式之外的5种模式称为异常模式。

之所以称之为异常模式,是因为这些模式都有自己的寄存器组。而user和sys mode共用一组寄存器组。

FIQ要比IRQ的响应快很多,首先FIQ的优先级比较高,再次ARM的FIQ会有自己更多的寄存器(r8_r12),由ARM自动保存。

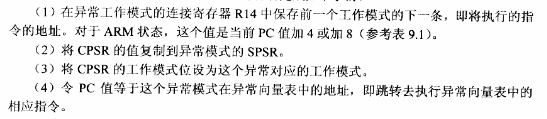

异常处理过程:将下一条指令存入LR寄存器,CPSR赋值到SPSR,强制设置CPSR运行位,跳转到异常处理函数。

返回:将LR中的值减相应的偏移量送到PC中,将SPSR的值复制到CPSR中。

异常向量表:0x0000_0000---复位Reset,进入SVC模式。

0x0000_0004---未定义指令,进入UND模式。

0x0000_0008---软件中断,进入SVC模式。

0x0000_000C---中止指令,进入ABT模式。

0x0000_0010---中止数据,进入ABT模式。

0x0000_0014---保留

0x0000_0018---IRQ中断,进入IRQ模式。

0x0000_001C---FIQ中断,进入FIQ模式。

异常与中断的区别和联系:

1. 中断可以看做异常的一种情况;

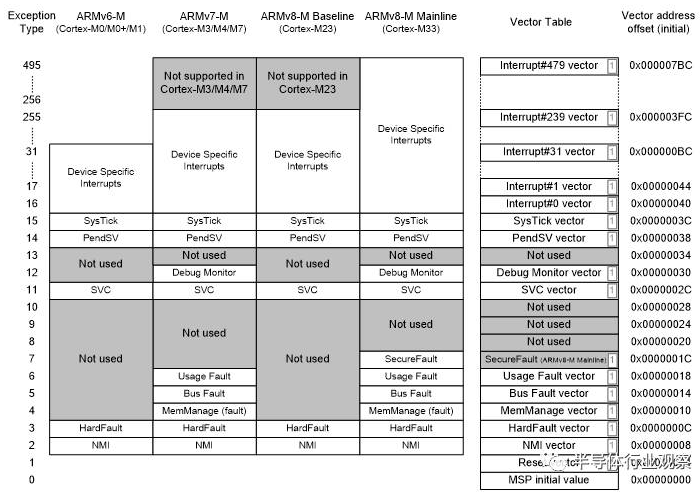

2. 中断是可以屏蔽的(CPSR的I位和F位分别屏蔽IRQ和FIQ),异常无法屏蔽。

3. 被动触发中断异常的情况会很多,中断异常指向的一般是中断向量表,根据中断ID在中断向量表中,找对应的中断服务子程序。

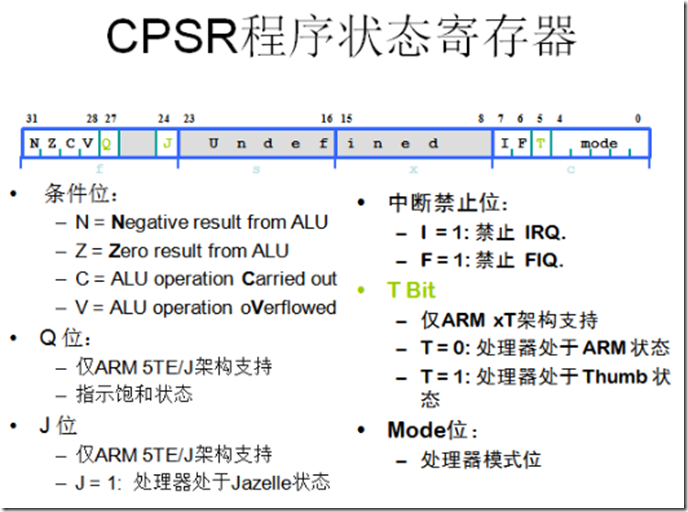

ARM的内核版本与对应的微处理器核心:

ARM7TDMI,ARM710T,ARM9TDMI,ARM920T V5

ARM11 V6

ARM Cortex-M,Cortex-R,Cortex-A V7

arm7是基于单纯的冯诺依曼结构来设计的,code和data共享总线,内部有三级流水线:取指,译码,执行;

arm9是基于哈佛结构来设计的,code和data分别有自己的addr和data总线,内部有五级流水线:取指,译码,取操作数,执行,写回。

arm7TDMI,arm9TDMI这样的内核并不能支持os,之后arm提供了加入mmu和cache的arm710t和arm920t内核的版本。

这样的内核版本中,即使有流水线操作也没有对分支进行预测处理,内核中的总线矩阵使用的是amba ahb总线。

arm从armv7架构开始开发的cortex内核:

Cortex-M0,32位的,3级流水线mcu,内部是冯诺依曼结构,指令和数据共享同一总线,基于armv6m架构。

内部总线矩阵AHB总线,中断采用嵌套式中断控制器(NVIC),调试接口通过DAP接口支持jtag和swi。

Cortex-M3,32位的,3级流水线mcu,内部是哈佛结构,增加了分值预测功能。基于armv7m架构。支持thumb-2指令集,不支持arm指令集。

内部总线矩阵AHB总线,中断采用嵌套式中断控制器(NVIC),调试接口通过DAP接口支持jtag和swi,但是也支持coresight的部分etm功能。

支持MPU,存储器保护单元。内部实现了除法和单周期乘法的ALU单元。

Cortex-M4,在M3的基础上,增加了单周期乘法累加(MAC单元),SIMD指令,满足IEEE 754的FPU单元。同样不支持arm指令集。

Cortex-M7,总线矩阵使用amba4的axi 64bit,引入了data和code的TCM cache。

由于MCU中不会支持os,Cortex-M系列的异常模型,与A系列不同,处理器mode也相应的不同。

ARM处理器中一共有37个寄存器。

分别有31个通用寄存器:R0-R15, R13_svc, R14_svc, R13_abt, R14_abt, R13_und, R14_und, R13_irq, R14_irq, R8_frq----R14_frq。

6个状态寄存器:CPSR, SPSR_svc, SPSR_abt, SPSR_und, SPSR_irq, SPSR_fiq。

R13通常用作堆栈指针。R14通常用作子程序连接。

CPSR当前程序状态寄存器。SPSR备份程序状态寄存器。

arm处理器的架构发展:

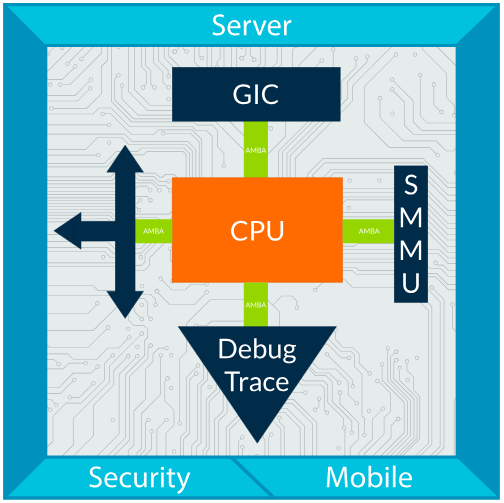

arm系统一般包括:mpcore,debug and trace,smmu,GIC,AMBA bus,security扩展,

arm中最多支持16个coprocessor,CP0-CP15,其中CP8-CP15是由arm reserve的,CP0-CP7是imp defined的。

arm的coprocessor model中,coprocessor一般包括,

1) 组成coprocessor interface的primary,secondary coprocessor寄存器;

2) internal寄存器;

ARMv7以及之前的版本中,包含的coprocessor有:

1) CP15,提供memory,cache,tcm的控制,和系统中非debug功能的寄存器;也被称为系统控制协处理器

2) CP14,提供其他系统寄存器的访问,包括debug,trace;

3) CP10,CP11,用作SIMD,VFP的控制,需要同时使用。

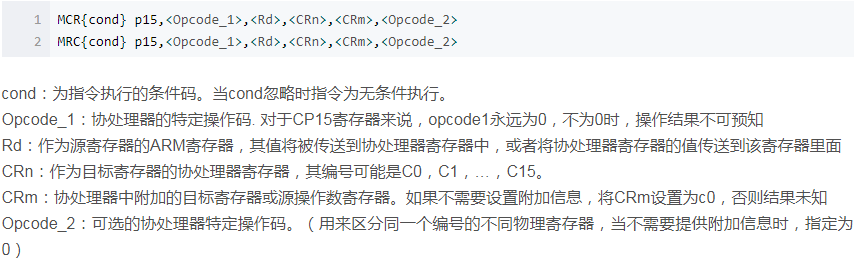

ARM的协处理器指令包括五个:

1) CDP,协处理器数操作指令,

2) LDC,协处理器数据加载指令,

3) STC,协处理器数据存储指令,

4) MCR,ARM寄存器到协处理器寄存器的数据传送指令,

5) MRC,协处理器寄存器到ARM寄存器的数据传送指令,

命令格式:

ARM_Core的处理器模式与寄存器,结构杂谈的更多相关文章

- 二、冯式结构与哈佛结构及ARM处理器状态和处理器模式

2.1 冯式结构与哈佛结构 2.1.1 两者的区别 如果是独立的存储架构和信号通道那就是哈佛结构,否则就是冯式结构 结构与是否统一编址没有关系,也与 CPU 没有关系,与计算机的整体设计有关 CACH ...

- 【嵌入式开发】ARM 芯片简介 (ARM芯片类型 | ARM处理器工作模式 | ARM 寄存器 | ARM 寻址)

: 12MHz 晶振 对应 405 ~ 532 MHz 处理速度; -- : 16K 指令缓存, 16K 数据缓存; -- : 32KB 指令缓存, 32KB 数据缓存; (3) 内存接口对比 : 提 ...

- ARM处理器模式

ARM处理器模式 ARM处理器共有7种运行模式: l 用户模式(User,usr):正常程序执行的模式 l 快速中断模式(FIQ,fiq):用于高速数据传输和通道处理 l 外部中断模式(IRQ, ...

- ARM的工作模式和寄存器

以前学的时候学的是S3C6410的开发板,它是三星公司推出的基于ARM v6架构(指令集),处理器是ARM11. ARM架构是构建每个ARM处理器的基础. 目前最新的是ARM v8架构:http:// ...

- ARM的编程模式及寄存器

根据朱老师的课程及下面博客整理 http://blog.chinaunix.net/uid-20443992-id-5700979.html ARM 采用的是32位架构 ARM 约定: Byte : ...

- BS模式的模型结构详解

编号:1004时间:2016年4月12日16:59:17功能:BS模式的模型结构详解 URL:http://blog.csdn.net/icerock2000/article/details/4000 ...

- 修饰模式(Decorator结构化)C#简单的例子

修饰模式(Decorator结构化)C#简单的例子 播放器的基本功能是移动.执行等.BaseAbility 新增功能:1.伤害技能harmAbility:2.阻碍技能BaulkAbility:3.辅助 ...

- arm9的操作模式,寄存器,寻址方式

工作模式 Arm有7种工作模式: 名称 简称 简介 User Usr 正常用户程序执行的模式(linux下用户程序就是在这一模式执行的.) FIQ Fiq 快速中断模式 IRQ Irq 普通中断模式 ...

- 软件调试——IA-32 保护模式下寄存器一览

最近在看张银奎先生的<调试软件>一书,想将关键的技术记录下来,以便日后查阅,也分享给想看之人吧. 1 通用寄存器 EAX,EBX,ECX,EDX:用于运算的通用寄存器,可以使用AX,BX等 ...

随机推荐

- Nginx写IO占用高故障处理

文章来源:<https://www.centos.bz/2015/04/handle-nginx-write-io-problem/> 故障现象 突然收到一台服务器负载过高告警,紧接着网站 ...

- vue-resource使用 (vue仿百度搜索)

1.this.$http.get()方法2.this.$http.post()方法3.this.$http.jsonp()方法 (vue仿百度搜索) 在输入框中输入a, 然后在百度f12 ==> ...

- probing privatePath如何作用于ASP.NET MVC View

当View上using一些从probing privatePath加载的程序集,运行时会提示无法找到对应程序集. <runtime> <assemblyBinding xmlns=& ...

- Ubuntu下Chrome运行Silverlight程序

Ubuntu 14.04.1下运行Terminal,安装Pipelight输入以下命令: sudo add-apt-repository ppa:pipelight/stable sudo apt-g ...

- ASP.NET 文件上传于下载

本文主要介绍一下,在APS.NET中文件的简单上传于下载,上传是将文件上传到服务器的指定目录下,下载是从存入数据库中的路径,从服务器上下载. 1.上传文件 (1)页面代码 <table alig ...

- html、css如何画实心圆

css3画实心圆 实现方法相当简单,css代码如下: .circle{ width:100px; height:100px; border-radius:50px; /* 图形的半径 */ }

- [转][darkbaby]任天堂传——失落的泰坦王朝(上)

前言: 曾经一再的询问自我;是否真的完全了解任天堂这个游戏老铺的真实本质?或许从来就没有人能够了解,世间已经有太多的真相被埋没在谎言和臆测之中.作为 一个十多年游龄的老玩家,亲眼目睹了任天堂从如日 ...

- K-means中的K值选择

关于如何选择Kmeans等聚类算法中的聚类中心个数,主要有以下方法(译自维基): 1. 最简单的方法:K≍sqrt(N/2) 2. 拐点法:把聚类结果的F-test值(类间Variance和全局Var ...

- vue之cli脚手架安装和webpack-simple模板项目生成

ue-cli 是一个官方发布 vue.js 项目脚手架,使用 vue-cli 可以快速创建 vue 项目. GitHub地址是:https://github.com/vuejs/vue-cli 一.安 ...

- opengl学习笔记(三):经过纹理贴图的棋盘

opengl纹理贴图的步骤: 1:创建纹理对象,并为它指定一个纹理 2:确定纹理如何应用到每个像素上 3:启用纹理贴图功能 4:绘制场景,提供纹理坐标和几何图形坐标 注意:纹理坐标必须在RGBA模式下 ...