S02_CH04_User_IP实验Enter a post title

S02_CH04_User_IP实验

4.1 创建IP

在之前的教程中,我们通过MIO与EMIO来控制LED,所使用的也是官方的IP,实际当中,官方提供的IP不可能涵盖到方方面面,用户需要自己编写硬件描述语言,然后将其封装成IP来使用,本节就将详细的讲解如何在VIVADO中创建用户自定义的IP。

Step1:打开VIVADO软件,新建一个工程。

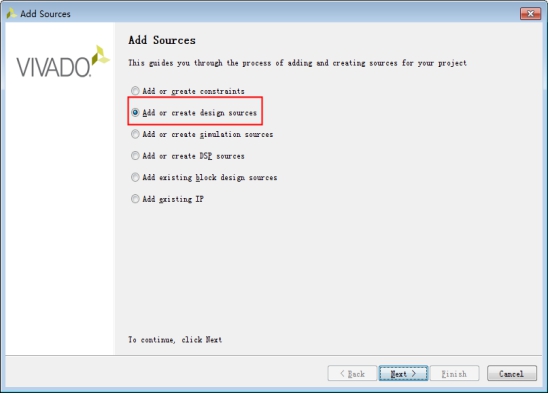

Step2:单击Add Source,选择Add or Creat design Sources,然后单击Next。

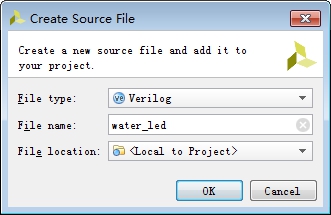

Step3:单击Create File,输入文件名,单击OK。

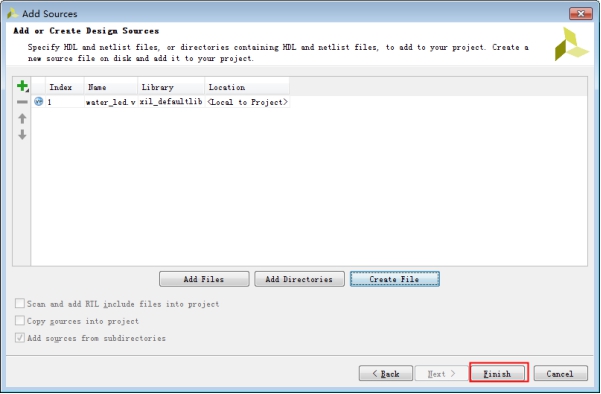

Step4:单击Finish,完成Verilog文件的创建。

Step5:将以下代码复制入文本编辑区内。

|

module LED_ML( input CLK_i,//100MHZ input RSTn_i, output reg [3:0]LED_o ); reg [31:0]C0; always @(posedge CLK_i) if(!RSTn_i) begin LED_o <= 4'b0001; C0 <= 32'h0; end else begin if(C0 == 32'd49_999_999)//1s begin C0 <= 32'h0; if(LED_o == 4'b1000) LED_o <= 4'b0001; else LED_o <= LED_o << 1; end else begin C0 <= C0 + 1'b1; LED_o <= LED_o; end end endmodule |

Step6:单击Tools—>Create and package IP,单击Next。

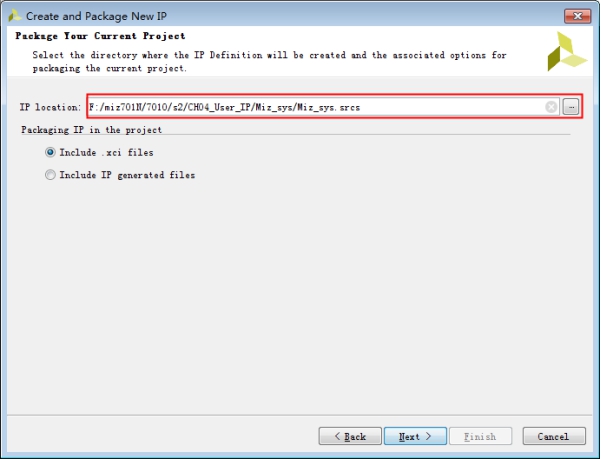

Step7:选择IP的保存路径,单击Next。

Step8:单击Finish完成封装。

4.2 调用自定义IP

Step1:另外新建一个VIVADO工程,根据自己的开发板正确配置芯片型号。

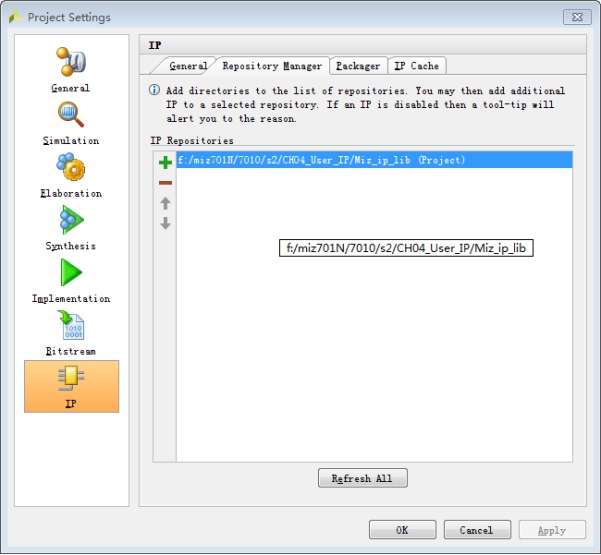

Step2:在Project manager区中单击Project settings。

Step3:选择IP设置区中的repository manager,。

Step:4:单击+号图标,将上一节封装的IP的路劲存放进去,单击OK。

Step5:新建一个BD文件,输入文件名,完成创建。

Step6:向BD文件中添加一个ZYNQ Processing system,根据自身硬件完成IP的配置。

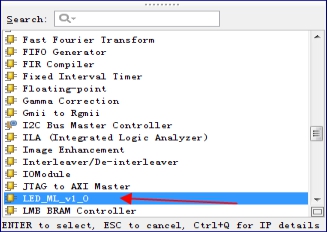

Step7:单击添加IP图标,输入上一节我们自定义IP的模块名,将其添加入BD文件中。

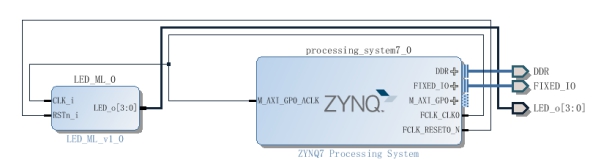

Step8:按如下电路图完成模块间的连线。

Step9:右键单击Block文件,文件选择Generate the Output Products。

Step10:右键单击Block文件,选择Create a HDL wrapper,根据Block文件内容产生一个HDL 的顶层文件,并选择让vivado自动完成。

Step11:选中Project manager,然后右单击Constraints,选择Add Sources。

Step12:输入文件名,完成创建,将上一章EMIO的约束文件copy进去。

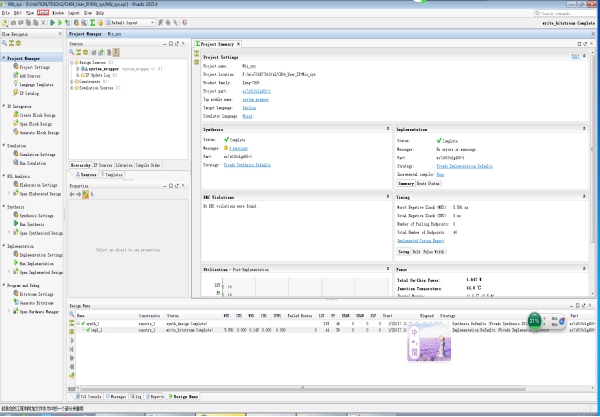

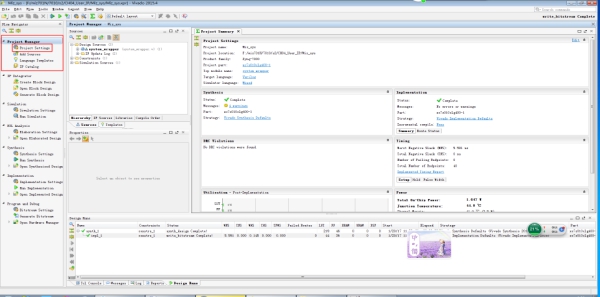

Step11:产生bit文件。

4.3 导入到SDK

由于自定义的IP的时钟输入来自于ZYNQ Processing system,源时钟是使用的PS的时钟,因此需要启动SDK整个系统才能启动,而自定义IP不需要由SDK进行配置,因此我们可以按照前几节讲过的内容,在SDK端建立一个Hello World工程跑起来就能让自定义IP跑起来。

Step1:创建一个Hello World工程。

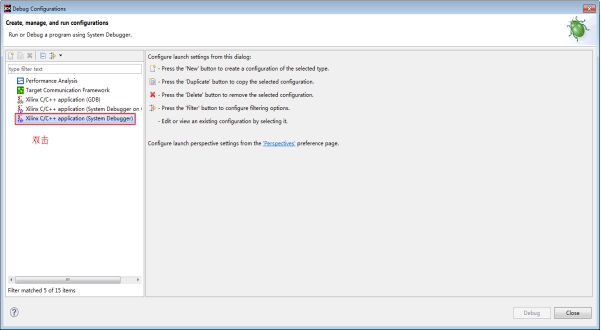

Step2:右击工程,选择Debug as ->Debug configuration。

Step3:选中system Debugger,双击创建一个系统调试。

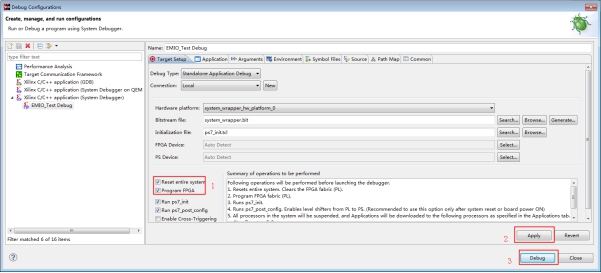

Step7:设置系统调试。

Step8:单击窗口上的运行按钮,运行程序,可看到LED的流水操作。

4.4 本章小结

本章主要介绍了如下在VIVADO下创建一个自定义的IP,内容比较简单,需要注意的是如果工程中使用的源时钟是为PS时钟的话,是需要启动SDK系统才能正常工作的,若是系统使用到了ZYNQ Processing System,则系统使用的是PS时钟,这是一个判断的依据。在ZYNQ的开发中,创建自定义IP是一项基本功,还未熟练掌握的要勤加练习。

S02_CH04_User_IP实验Enter a post title的更多相关文章

- S02_CH05_UBOOT实验Enter a post title

S02_CH05_UBOOT实验 5.1什么是固化 我们前几章的程序都是通过JTAG先下载bit流文件,再下载elf文件,之后点击Run As来运行的程序.JTAG的方法是通过TCL脚本来初始化PS, ...

- S02_CH03_EMIO实验Enter a post title

S02_CH03_EMIO实验 3.1 EMIO 和MIO的对比介绍 上次讲到MIO的使用,初步熟悉了EDK的使用,这次就来说说EMIO的使用.如你所见zynq的GPIO,分为两种,MIO(multi ...

- S02_CH02_MIO实验Enter a post title

S02_CH02_MIO实验 2.1 GPIO简介 Zynq7000系列芯片有54个MIO(multiuse I/O),它们分配在 GPIO 的Bank0 和Bank1隶属于PS部分,这些IO与PS直 ...

- 【第一季】CH05_FPGA设计Verilog基础(二)Enter a post title

[第一季]CH05_FPGA设计Verilog基础(二) 5.1状态机设计 状态机是许多数字系统的核心部件,是一类重要的时序逻辑电路.通常包括三个部分:一是下一个状态的逻辑电路,二是存储状态机当前状态 ...

- 【第一季】CH04_FPGA设计Verilog基础(一)Enter a post title

[第一季]CH04_FPGA设计Verilog基础(一) 4.1 Verilog HDL 代码规范 u 项目构架设计 项目的构架用于团队的沟通,以及项目设计的全局把控 u 接口时序设计规范 模块和模块 ...

- ctrl+enter提交留言

<!DOCTYPE html><html lang="zh-CN"><head> <meta charset="UTF-8&qu ...

- swoole实验版聊天室

“swoole实验版聊天室”是依据一堂swoole培训课内容改编的,结合了bootstrap前端框架.redis数据库.jquery框架等实现基本功能,只是体现了swoole的应用,并不是为了专门写个 ...

- Oracle第一步

Oracle 启动数据库 Startup [NOMOUNT|MOUNT|OPEN|FORCE] [restrict] [pfile=filename] 启动实例,加载数据库,启动数据库 oRACLE关 ...

- Using Nuget in Visual Studio 2005 & 2008

NuGet is a Visual Studio extension that makes it easy to install and update third-party libraries an ...

随机推荐

- ZR#955 折纸

ZR#955 折纸 解法: 可以发现折纸之后被折到上面的部分实际上是没有用的,因为他和下面对应位置一定是一样的,而影响答案的只有每个位置的颜色和最底层的坐标范围.因此,我们只需要考虑最底层即可,即我们 ...

- MySql的Linux版安装

1,官网下载MySql的Linux版: 下载地址:http://dev.mysql.com//downloads/mysql/ 2.上传到Linux服务器,建议放在/opt/目录下 3.检查当前系统是 ...

- expdp / impdp 用法详解 ,和exp / imp 的区别

一 关于expdp和impdp 使用EXPDP和IMPDP时应该注意的事项:EXP和IMP是客户端工具程序,它们既可以在客户端使用,也可以在服务端使用.EXPDP和IMPDP是服务端的工具程 ...

- js 移除数组中的内容

使用方法:arr.splice(arr.indexOf(ele),length):表示先获取这个数组中这个元素的下标,然后从这个下标开始计算,删除长度为length的元素 这种删除方式适用于任何js数 ...

- chrome console控制台引入jquery库

var jqueryJs=document.createElement('script');jqueryJs.setAttribute("type","text/Java ...

- [MySql]当虚拟机的IP地址自动更换后,JDBC使用原来的配置连不上MySql数据库时所报的异常。

Communications link failure The last packet sent successfully to the server was 0 milliseconds ago. ...

- 实用的在线预览数据字典的工具(php编写)

前言 无论是刚接手新项目,或者是维护老项目,有一个方便的数据字典可用是最棒哒! 本文是我为了方便使用数据字典而写的代码. 代码无版权,随便使用. 拷贝代码后,只需修改数据库名,主机,用户名,密码,开箱 ...

- osg help

#ifdef _WIN32#include <Windows.h>#endif // _WIN32 #include <osgViewer/Viewer>#include &l ...

- ckpt convert to pb

import tensorflow as tf #from create_tf_record import * from tensorflow.python.framework import grap ...

- Build Telemetry for Distributed Services之OpenTracing项目

中文文档地址:https://wu-sheng.gitbooks.io/opentracing-io/content/pages/quick-start.html 中文github地址:https:/ ...