12-Verilog-同步FIFO设计

同步FIFO和异步FIFO

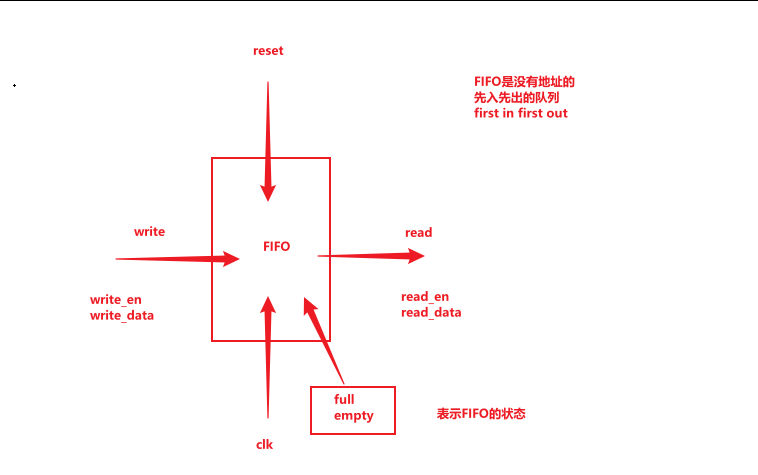

FIFO分为一个同步FIFO,一个异步FIFO,FIFO有读口和写口

读写时钟是一个,就是同步FIFO;读写时钟不是一个,异步FIFO

- IP核设计中,一般使用同步FIFO设计

- SOC设计或者跨时钟域的内容使用异步FIFO

RAM

FIFO中的数据,存储在寄存器中或者是SRAM中

- 数据少--存储在寄存器中

- 数据多--使用SRAM

- 一般而言fab会提供RAM仿真的模型,仿真库和物理库

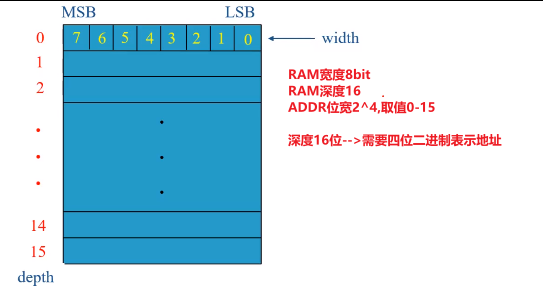

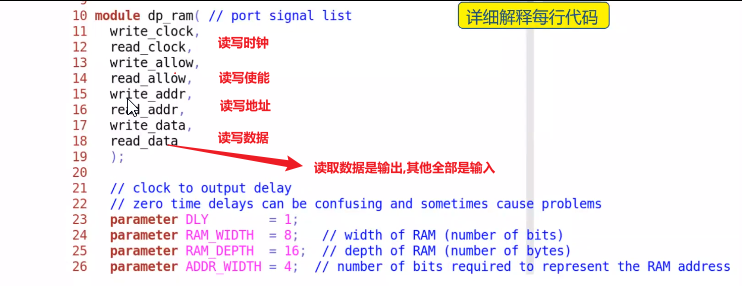

设计实现一个16*8的双端口RAM

RAM在时钟的驱动下,可以通过一个端口写数据,从另外一个端口读取数据,并且读写可以同时进行,如果要写入数据,首先要有写入的数据,并且要知道写到什么地方,要知道写的地址,RAM不可能一直在写,所以要有写使能;读的时候也要知道从什么地方读,有读的地址,有读使能决定什么时候读,读取出来得到数据

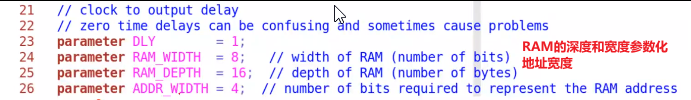

- RAM的位宽,写成参数化的形式,能参数化的部分,全部进行参数化parameter

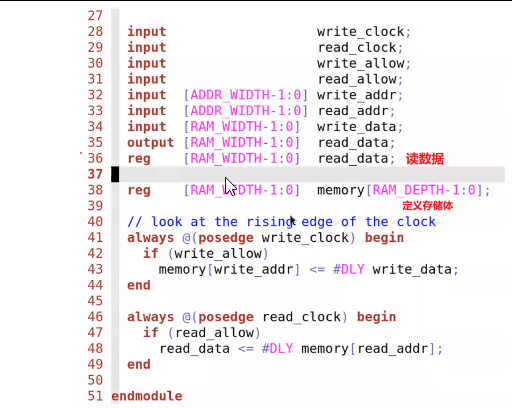

- 定义完接口数据之后,定义内部;数据是存放在一个存储器中的,RTL中是不能直接生成存储器的,需要使用代码进行模拟,实际综合的时候,将module代码替换为SRAM,SRAM是一个已经综合好的硬件,可以直接进行使用

- 首先定义存储体,使用reg或者logic类型

reg/logic [RAM_WIDTH-1:0] memory[RAM_DEPTH-1:0]; //memory存储体

- 写操作,在写使能的驱动下,根据写地址,将数据赋值到写地址中,得到的是寄存器组

- 读操作,从entrance中,根据读地址,将memory中的数据读取出来,read_data需要尽心输出寄存的

- 实际上生成的是一个总容量为128bit的寄存器,数据比较多的时候,使用SRAM存储数据,面积会更小;数据量比较少的时候,使用寄存器,面积也不会大

always @ (posedge clk) begin

if(read_en)

read_data <= memory[read_addr]

end

// SRAM实现

wire [DATA_WIDTH-1:0] read_data_nxt;

assign read_data_nxt = memeory[read_addr];

always @ (posedge clk) begin

if(read_en)

read_data <= read_data_nxt;

end

// 寄存器实现

wire [DATA_WIDTH-1:0] read_data_nxt;

assign read_data_nxt = memeory[read_addr];

- SRAM的时序是在读使能的下一个cycle,得到读数据;用register实现fifo,可以使用组合逻辑,在当前的cycle得到数据

FIFO设计

- 先写存储体,可以使用register或者sram搭建

- FIFO control,FIFO除了时钟和复位,还有写端口和读端口

- FIFO 是先进先出的队列,先写进去的数据,读的时候先读出来;FIFO中的数据存储在存储体中,类似于SRAM,有写数据,写使能,读使能,读数据,但是没有读地址和写地址,读地址和写地址是由FIFO内部的功能模块,FIFO control功能模块进行控制

- 端口:读写使能\读写数据,没有读地址和写地址

- FIFO原则:满不能写,空不能读,取决于full和empty信号,上游模块看到full信号,不向里面写,下游模块看到empty之后不读,FIFO自己也需要进行保护

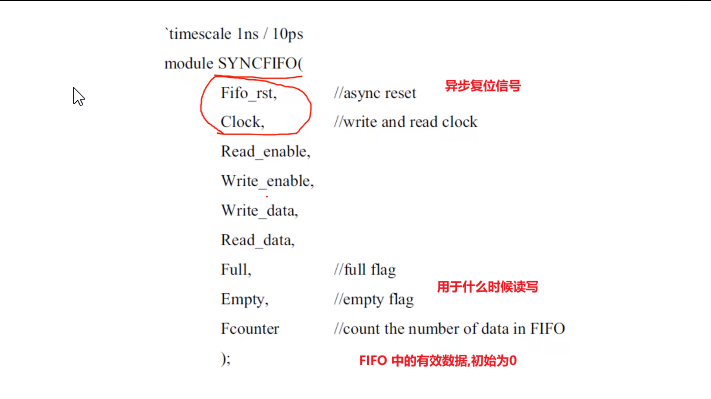

FIFO 端口

- Fcounter,当前FIFO中有效的数据量,写入一个数据,加一,读出一个数据为0,在标准的FIFO中是没有的

module SYNCFIFO(

Fifo_rst, //async reset

Clock, // write and read clock

Read_enable,

write_enable,

Read_data,

write_data,

Full, // full flag

Empty, // empty flag

Fcounter // count the number of data in FIFO

);

endmodule

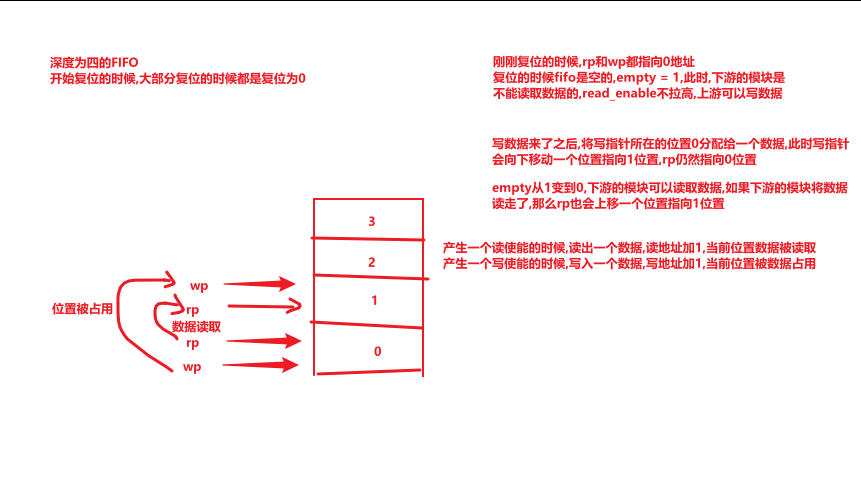

FIFO control

- FIFO control 最主要的就是维护两个地址,读地址和写地址的产生;FIFO control需要有读使能和写使能,读地址和写地址是直接连到SRAM中的,不用经过FIFO control,空满信号也是FIFO control产生的

- FIFO control 需要有读写使能,空满信号,读指针rp和写指针wp

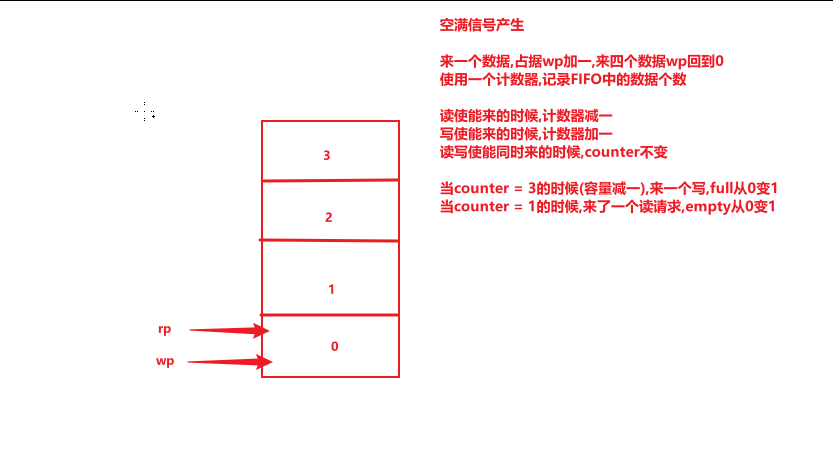

- 空满状态使用计数器,计算存储器的容量

- counter = 3时,来一个写使能,就是再写入一个数据,counter = 4,full从0跳变为1

- counter = 1时,来一个读使能,再读取一个数据,counter = 0,empty从0跳变为1

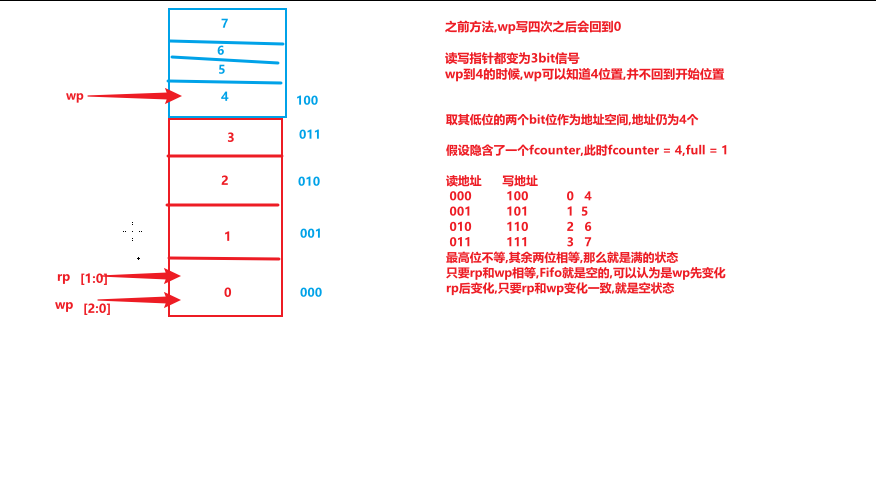

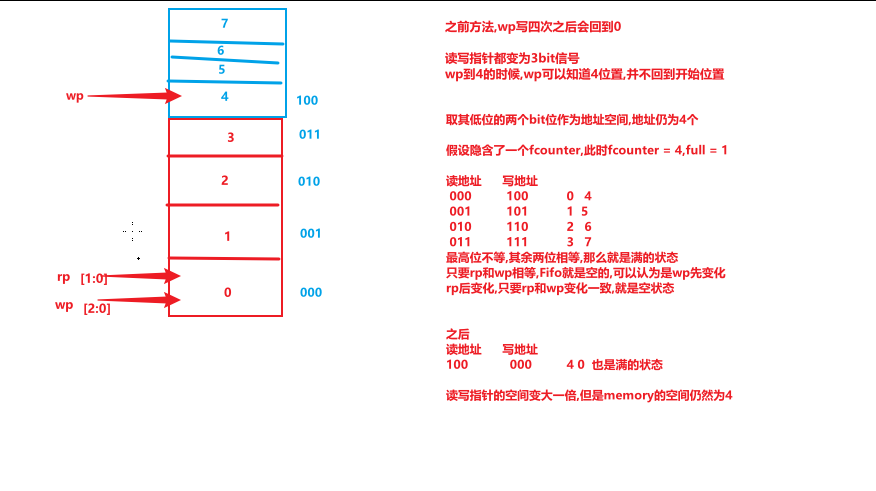

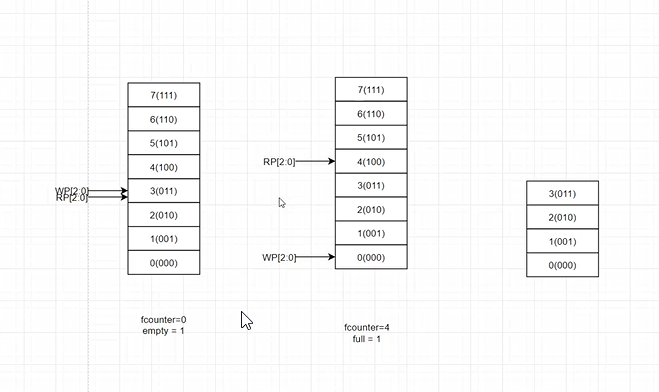

FIFO实现的两种方法

- 通过计数器产生空满信号,执行一次写操作,计数器加1;执行一次读操作,计数器减1;

- 通过扩展地址位,用最高位判断空满状态

// 方法1

paramter DATA_WIDTH = 8;

parameter ADDR_WIDTH = 9; // 2^9 512 这里设计的是512*8的RAM

input Fifo_rst;

input Clock;

input Read_enable;

input Write_enable;

input [DATA_WIDTH-1:0] Write_data;

output [DATA_WIDTH-1:0] Read_data;

output Full;

output Empty;

output [ADDR_WIDTH-1:0] Fcounter;

reg [DATA_WIDTH-1:0] Read_data;

reg Full;

reg Empty;

// reg [ADDR_WIDTH-1:0] Fcounter;

reg [ADDR_WIDTH] Fcounter;

reg [ADDR_WIDTH-1:0] Reader_addr; // read_address,FIFO control传递给memory的

reg [ADDR_WIDTH-1:0] write_addr; // write_address,FIFO control传递给memory的

wire Read_allow = (Read_enable && !Empty); // 读使能来的时候并且非空,才能读

wire Write_allow = (Write_enable && !FUll); // 写使能来的时候并且非满,才能写

RTL Coding

// 例化 RAM 并连接端口

DUALRAM U_RAM (

.Read_clock(Clock),

.Write_clock(Clock), // 同步复位时钟,使用同一个clock

.Read_allow(Read_allow),

.Write_allow(Write_allow),

.Read_addr(Read_addr),

.Write_addr(Write_addr),

.Write_data(Write_data),

.Read_data(Read_data)

);

// 空信号产生

always @(posedge Clock or posedge Fifo_rst) begin

if(Fifo_rst)

Empty <= 'b1; // 时钟复位的时候 empty=1s

else

Empty <= (!Write_allow && (Fcounter[8:1] == 8'h0)&&(Fcounter[0] ==0||Read_allow));

end

- 只要有写使能,Empty就为0,!Write_allow表示写使能无效的时候

- Fcounter[8:1] = 0,表示第1位到第9位都为0

- Fcounter[0] = 0,因为与的关系,所以Fcounter = 0000_0000_0,FIFO无数据,empty = 1;

- Fcounter[0] = 1,因为与的关系,所以Fcounter = 0000_0000_1,FIFO有一个数据,此时如果Read_allow来临,FIFO也无数据,empty = 1

// 最后一句的写法

empty <= Write_allow ? 1'b0 :

Read_allow ? (Fcounter == 9'd1):(Fcounter == 9'd0);

// Write_allow 为 1 empty = 0

// Write_allow 为0 empty = Read_allow ? (Fcounter == 9'd1):(Fcounter == 9'd0);

// Read_allow = 1 empty = Fcounter == 9'd1

// 读使能来之后,判断Fcounter是不是等于1,是empty=1,不是empty=0

// Read_allow = 0 empty = Fcounter == 9'd0

// 读使能为0,判断Fcounter是不是等于0,是empty=1,不是empty=0

// 这种方法使用了两个9bit比较器,面积大,不推荐使用

// Full 信号产生

always @(posedge clock or posedge Fifo_rst) begin

if(Fifo_rst)

Full <= 'b0;

else

Full <= (!Read_allow && (Fcounter[8:] == 8'hFF) &&((Fcounter[0]==1 || Write_allow)));

end

- 分析方法与empty信号产生相同

- 这里Full信号取值范围为0-511(1111_1111_1),9位的二进制数,取不到512,所以定义Full的时候要用10位

reg [ADDR_WIDTH] Fcounter; // 直接是10bit的位宽

Full <= Read_allow ? 1'b0 :

Write_allow ? (Fcounter == 10'd511) : (Fcounter == 10'd512);

// 地址产生

always @(posedge Clock or posedge Fifo_rst) begin

if(Fifo_rst)

Read_addr <= 'h0

else if(Read_allow)

Read_addr <= Read_addr + 'b1;

end

always @(posedge Clock or posedge Fifo_rst) begin

if(Fifo_rst)

Write_addr <= 'h0;

else

write_addr <= Write_addr + 'b1;

end

// Fcounter

always @(posedge Clock or posedge Fifo_rst) begin

if(Fifo_rst)

Fcounter <= 'h0;

else if((!Read_allow && !Write_allow) || (Read_allow && Write_allow))

begin

if(Write_allow)

Fcounter <= Fcounter + 'b1;

else

Fcounter <= Fcounter - 'b1;

end

end

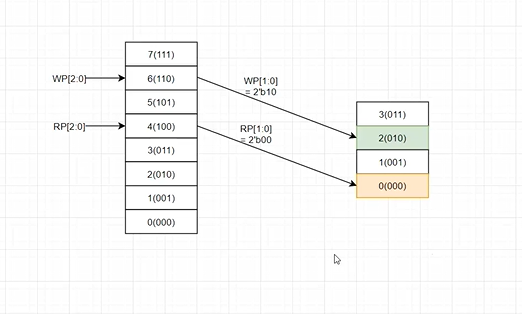

FIFO的第二种实现方法

- 扩展地址位,使用最高位表示空和满的情况

- 使用低位进行寻址

module sync_fifo(clk,rst,wr_en,rd_en,data_in,data_out,empty,full)

input clk,rst,wr_en,rd_en

input [7:0] data_in;

output empty,full;

output [7:0] data_out

reg [7:0] mem[15:0]; //16*8 RAM

reg [7:0] data_out;

wire [3:0] w_addr,r_addr; // 表示寻址

reg [4:0] r_addr_a,w_addr_a; // 表示产生地址

assign r_addr = r_addr_a[3:0];

assign w_addr = w_addr_a[3:0];

always@(posedge clk or negedge rst)

begin

if(!rst)

begin

r_addr_a = 5'b0;

end

else

begin

if (rd_en == 1 && empty == 0)

begin

data_out <=mem[r_addr];

r_addr_a <= r_addr_a+1;

end

end

end

always@(posedge clk or negedge rst)

begin

if(!rst)

begin

w_addr_a = 5'b0;

end

else

begin

if (wr_en == 1 && full == 0)

begin

mem[w_addr] <=data_in;

w_addr_a <= w_addr_a+1;

end

end

end

assign empty = (r_addr_a == w_addr_a) ? 0 : 1;

assign full = (r_addr_a[4] != w_addr_a[4] && r_addr_a[3:0] == w_addr_a[3:0])?1:0;

endmodule

12-Verilog-同步FIFO设计的更多相关文章

- 同步fifo的verilogHDL设计实例

原创 设计一个fifo,输入16bit,输出16bit的data,寻址宽度5bit,有空满标志. top 层如下所示: /* date : 2014/10/14 version : modelsim ...

- Verilog学习笔记简单功能实现(八)...............同步FIFO

Part 1,功能定义: 用16*8 RAM实现一个同步先进先出(FIFO)队列设计.由写使能端控制该数据流的写入FIFO,并由读使能控制FIFO中数据的读出.写入和读出的操作(高电平有效)由时钟的上 ...

- 怎么用Verilog语言描述同步FIFO和异步FIFO

感谢 知乎龚大佬 打杂大佬 网上几个nice的博客(忘了是哪个了....) 前言 虽然FIFO都有IP可以使用,但理解原理还是自己写一个来得透彻. 什么是FIFO? Fist in first out ...

- 同步fifo的Verilog实现

FIFO是一种先进先出的数据缓存器,他与普通存储器相比: 优点:没有外部读写地址线,这样使用起来非常简单: 缺点:只能顺序写入数据,顺序的读出数据, 其数据地址由内部读写指针自动加1完成,不能像普通存 ...

- 基于FPGA的异步FIFO设计

今天要介绍的异步FIFO,可以有不同的读写时钟,即不同的时钟域.由于异步FIFO没有外部地址端口,因此内部采用读写指针并顺序读写,即先写进FIFO的数据先读取(简称先进先出).这里的读写指针是异步的, ...

- 同步FIFO学习

在网上找的一个经典同步FIFO例子. 一.前言 FIFO (First-In-First-Out) 是一种先进先出的数据交互方式,在数字ASIC设计中常常被使用.FIFO按工作时钟域的不同又可以分为: ...

- 同步FIFO design and IP level verification

一.前言 应聘IC前端相关岗位时,FIFO是最常考也是最基本的题目.FIFO经常用于数据缓存.位宽转换.异步时钟域处理.随着芯片规模的快速增长,灵活的system verilog成为设计/验证人员的基 ...

- 同步fifo与异步fifo

参考以下帖子: https://blog.csdn.net/hengzo/article/details/49683707 https://blog.csdn.net/Times_poem/artic ...

- FPGA Asynchronous FIFO设计思路

FPGA Asynchronous FIFO设计思路 将一个多位宽,且在不停变化的数据从一个时钟域传递到另一个时钟域是比较困难的. 同步FIFO的指针比较好确定,当FIFO counter达到上限值时 ...

- FIFO设计思考之一

不管同步FIFO还是异步FIFO,设计难点是full/empty状态flag的正确性. 要保证任何情况 FULL时NO WRITE,EMPTY时NO READ.overflow / underflow ...

随机推荐

- 如何在LinkedIn上开发客户

LinkedIn作为一个职场社交平台,提供了许多开发外贸客户的机会和工具.通过在LinkedIn上建立个人和公司的专业形象.分享有价值的内容.参与行业社群和利用广告推广,您可以扩大您的业务网络,找到更 ...

- 2023-09-13:用go语言,给定一个整数数组 nums 和一个正整数 k, 找出是否有可能把这个数组分成 k 个非空子集,其总和都相等。 输入: nums = [4, 3, 2, 3, 5,

2023-09-13:用go语言,给定一个整数数组 nums 和一个正整数 k, 找出是否有可能把这个数组分成 k 个非空子集,其总和都相等. 输入: nums = [4, 3, 2, 3, 5, 2 ...

- 2023-05-28:为什么Redis单线程模型效率也能那么高?

2023-05-28:为什么Redis单线程模型效率也能那么高? 答案2023-05-28: 1.C语言实现,效率高 C语言程序运行速度快,因为其相较于其他高级语言更加接近底层机器.由于C语言直接操作 ...

- Provider MVVM架构

MVVM架构分为M(Model).V(View).VM(ViewModel)三个部分,他们分别处理自己的分工,在View和Model之间使用ViewModel作为中介者,使View和Model不受业务 ...

- 【DevCloud·敏捷智库】如何利用故事点做估算

背景 在某开发团队辅导的第二天,一个团队负责人咨询道:"领导经常管我要开发计划,我如何能快速的评估出预计开发完成时间呢,我们目前用工时估算,我听说过故事点估算,不知道适合吗?" 问 ...

- 一文带你搞懂从动态代理实现到Spring AOP

摘要:本文主要讲了Spring Aop动态代理实现的两种方式. 1. Spring AOP Spring是一个轻型容器,Spring整个系列的最最核心的概念当属IoC.AOP.可见AOP是Spring ...

- 云小课|手把手教您在PyCharm中连接云端资源进行代码调试

摘要:让我们看看如何在PyCharm中连接云端资源进行代码调试吧! 本文分享自华为云社区<[云小课]EI第54课 手把手教您在PyCharm中连接云端资源进行代码调试>,作者:Hello ...

- 使用appuploader工具流程(Windows版本)

转载:使用appuploader工具流程(Windows版本) 目录 转载:使用appuploader工具流程(Windows版本) 一.登录apple官网,注册账号 二.下载Appuploade ...

- 火山引擎数智平台最新直播活动:ByteHouse技术架构与最佳实践分享

数据的时效性,正深刻影响着企业的发展. 以大型半导体制造厂商为例,不同于常规工厂生产流水线,半导体制造通用的无人实验室生产模式高度依赖机械臂作业,且对整个生产调度链路中的精密度要求非常高,这背后主 ...

- & 0xFF 作用 取低8位

& 0xFF 取低8位 @Test void byteTest() { byte hex1 = (byte) 127; byte hex2 = (byte) 383; byte hex3 = ...