基于BASYS2的VHDL程序与仿真——50%占空比8分频器

转帖请注明转自http://www.cnblogs.com/connorzx/p/3547673.html

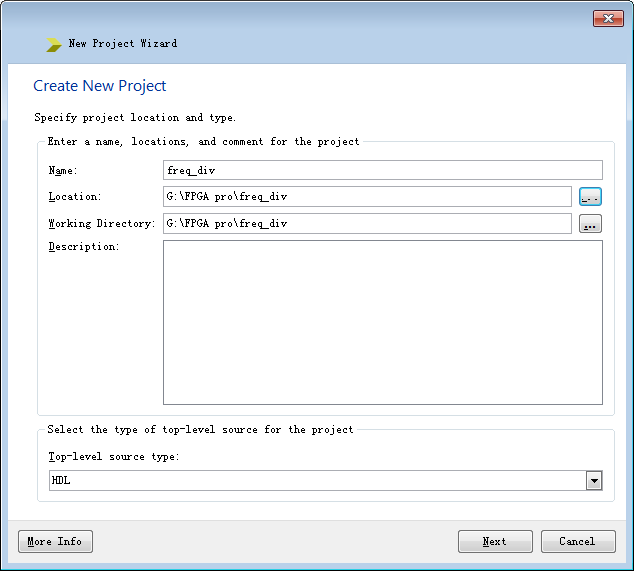

一、新建工程

1.点击File->New Project,

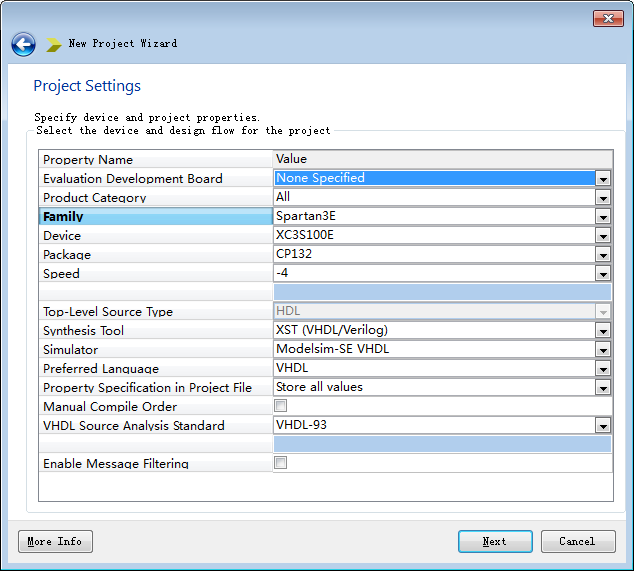

2.点击Next

注:此处的simulator已经和modelsim关联,未关联可以先选默认。

3.点击Next,点击Finish。

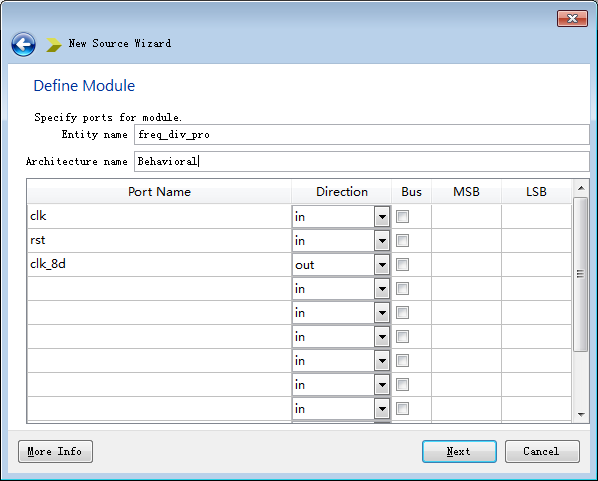

二、新建源文件

右击程序文件,点击New Source。选择VHDL Module。

输入端口设置,如下图所示

三、编写程序代码

library IEEE; --库引用

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL; entity freq_div_pro is --实体,端口定义

Port ( clk : in STD_LOGIC;

rst : in STD_LOGIC;

clk_8d : out STD_LOGIC);

end freq_div_pro; architecture Behavioral of freq_div_pro is --结构体定义

signal cnt:STD_LOGIC_VECTOR( downto );

signal tmp:STD_LOGIC; --定义两个信号

begin

process(rst,clk) --主进程

begin

if(rst = '')then --异步清零

cnt( downto ) <= "";

tmp <= '';

elsif(clk'event and clk ='')then --上升沿有效

cnt( downto ) <= cnt( downto ) + ; --计数

if(cnt( downto )="")then

tmp <= not tmp; --输出翻转,可以用T'触发器实现

cnt( downto ) <= ""; --计数器复位

end if;

end if;

end process;

clk_8d <= tmp; --输出 end Behavioral;

进行语法检查

然后点击Synthesize –XST 和Implement Design。

四、编写测试基准

选择simulation窗口,新建一个VHDL testbench,

编写代码如下:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY freq_div_test IS

END freq_div_test; ARCHITECTURE behavior OF freq_div_test IS -- Component Declaration for the Unit Under Test (UUT) COMPONENT freq_div_pro

PORT(

clk : IN std_logic;

rst : IN std_logic;

clk_8d : OUT std_logic

);

END COMPONENT; --Inputs

signal clk : std_logic := '';

signal rst : std_logic := ''; --Outputs

signal clk_8d : std_logic;

-- Clock period definitions

constant clk_period : time := ns; BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: freq_div_pro PORT MAP (

clk => clk,

rst => rst,

clk_8d => clk_8d

);

-- Clock process definitions

clk_process :process

begin

clk <= '';

wait for clk_period/;

clk <= '';

wait for clk_period/;

end process; -- Stimulus process

stim_proc: process

begin

-- hold reset state for ns.

rst<='' after ns;

wait;

end process;

END;

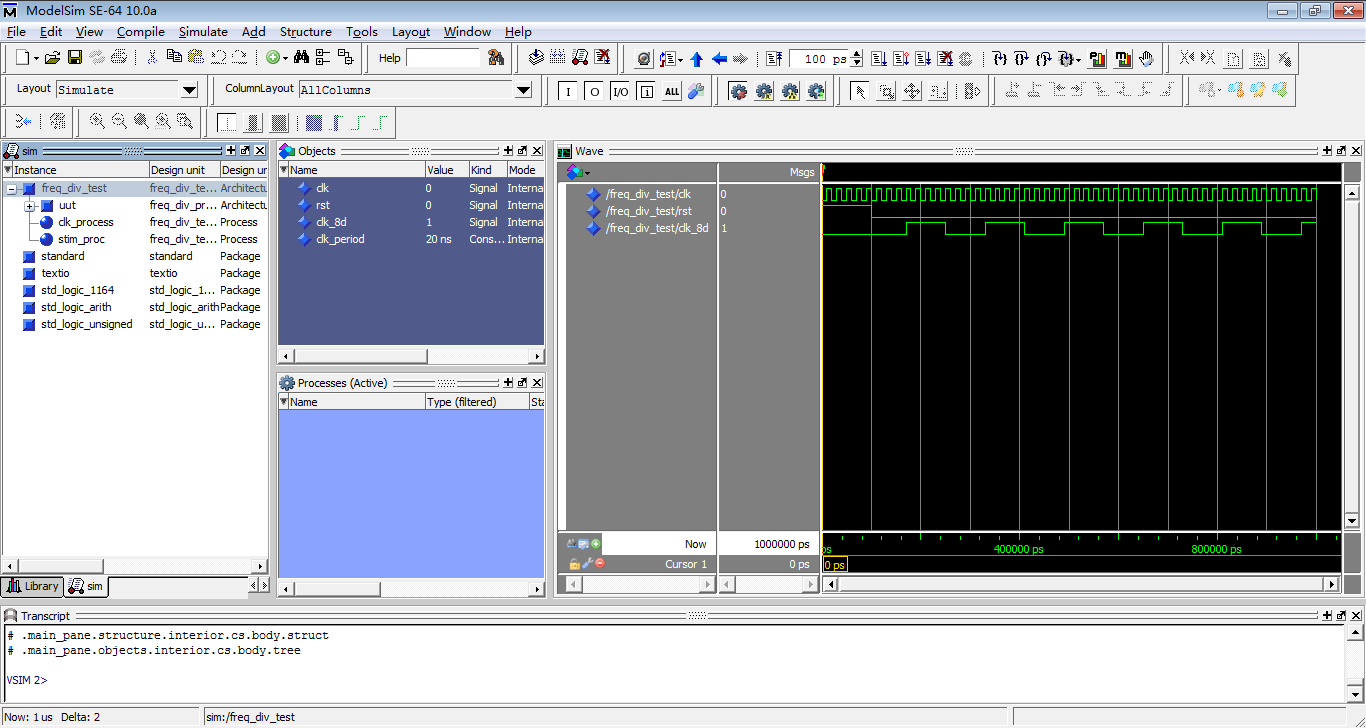

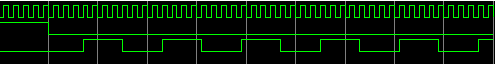

选择仿真程序文件,点击Simulate Behavioral Model,弹出Modelsim程序,可以看到如下结果

波形如下,

注:本实验采用Modelsim进行仿真分析,Modelsim软件以及Xilinx和Modesim关联方法请参照以下链接操作。

链接: http://pan.baidu.com/s/1eQj5rrW 密码: c1ca

基于BASYS2的VHDL程序与仿真——50%占空比8分频器的更多相关文章

- 基于BASYS2的VHDL程序——交通灯

请尊重作者版权,转载请注明原地址: http://www.cnblogs.com/connorzx/p/3676746.html 数电实验交通灯VHDL版,程序写的扩展性很差,待以后有时间进行优化. ...

- 基于BASYS2的VHDL程序——分频和数码管静态显示程序

转载请注明出处:http://www.cnblogs.com/connorzx/p/3633860.html 分频是基于计数器程序.由于FPGA的并行处理能力,根本不需要单片机式的中断指令,用起来很方 ...

- 基于BASYS2的VHDL程序与烧写——按键消抖程序

请尊重作者版权,转载请注明源地址http://www.cnblogs.com/connorzx/p/3548364.html 按键在按下的过程中通常会产生一段时间的抖动,为了消除这种抖动,一般采取两种 ...

- 基于BASYS2的VHDL程序——交通灯(状态机版)

请尊重作者版权,转载注明源地址:http://www.cnblogs.com/connorzx/p/3694618.html 使用了状态机,增加了可读性和用户体验. library IEEE; use ...

- 基于BASYS2的VHDL程序——数字钟(最终版)

转载请注明原地址:http://www.cnblogs.com/connorzx/p/3674178.html 调时电路正常工作.一切正常.发现做FPGA还是得从数电的思路思考,设置一个预置使能端,预 ...

- 基于BASYS2的VHDL程序——数字钟(改进版)

扩展到时分秒.加了入调时电路,但不知道为什么有两个按键不好使.而且不知道以何种方式假如按键消抖电路,因为加入后会多个时钟控制一个信号,物理不可实现.调试电路待解决.还有,四个数目管中间的那两个圆点怎么 ...

- 基于BASYS2的VHDL程序——数字钟

在编电子表时发现FPGA求余,取模只能针对2的次方.毕竟是数字的嘛! 时钟用到了动态刷新数码管.以一个大于50Hz的速度刷新每一个数码管. 因为数码管只有四个,只写了分针和秒针. 代码如下: libr ...

- 改善C#程序,提高程序运行效率的50种方法

改善C#程序,提高程序运行效率的50种方法 转自:http://blog.sina.com.cn/s/blog_6f7a7fb501017p8a.html 一.用属性代替可访问的字段 1..NET ...

- 基于HTML5的燃气3D培训仿真系统

最近上线了的基于HTML5的燃气3D培训仿真系统,以前的老系统是采用基于C++和OpenGL的OpenSceneGraph引擎设计的,OSG引擎性能和渲染效果各方面还是不错的,但因为这次新产品需求要求 ...

随机推荐

- UVALive 5135 Mining Your Own Business 双连通分量

据说这是一道Word Final的题,Orz... 原题链接:https://icpcarchive.ecs.baylor.edu/index.php?option=com_onlinejudge&a ...

- UVALive - 3700 Interesting Yang Hui Triangle

题目大意就是求一下 杨辉三角的第N行中不能被P整除的有多少个. 直接卢卡斯定理一下就行啦. #include<bits/stdc++.h> #define ll long long usi ...

- iOS真机测试,为Provisioning添加设备

------------添加设备到provisioning------------- 1,登陆https://developer.apple.com/devcenter/ios/index.actio ...

- mac 当前位置打开终端

做开发时经常会遇到在当前目录打开终端的情况,一直都是先启动终端,然后再切换到当前目录,今天发现了一个新的方法,虽然不是一步到位,但比以前快多了. 工具/原料 mac系统 苹果电脑 方法/步骤 ...

- 权重轮询调度算法(WeightedRound-RobinScheduling)-Java实现

权重轮询调度算法(WeightedRound-RobinScheduling)-Java实现 import java.math.BigInteger; import java.util.ArrayLi ...

- Linux中的热键[Tab] [Ctrl]-c [Ctrl]-d

Tab键:命令或者文件补全.可以避免很多的输入错误 1. 按一次,文件或命令补全 2. 按两次,会列举出以按键前的字母为首的所有命令或者文件 Ctrl+C:中断目前程序 Ctrl+D:键盘输入结束.可 ...

- 使用Cout输出String和CString对象

CString和string都是一个类,不同的是CString主要用于MFC或者是ATL编程中,而string则多用于Windows控制台编程中 在实际编程过程中,我们经常用到string或者是CSt ...

- strupr和strlwr字符串函数的使用

strupr 功能:将小写字母转换为大写字母 strlwr 功能:将大写字母转换为小写字母 在VS2013里面使用的时候要这样的格式 _strlwr_s _strupr_s #include<s ...

- 将UIBezierPath存为自己定义格式的字符串,再将字符串转为UIBezierPath

<pre name="code" class="objc">自己定义字符串格式为:@"123.02,234.23|321.23,432.0 ...

- 物联网网络编程和web编程

本文是基于嵌入式物联网研发project师的视觉对网络编程和web编程进行阐述. 对于专注J2EE后端服务开发的同学来说,这篇文章可能略微简单.可是网络编程和web编程对于绝大部分嵌入式物联网proj ...