FPGA入门实例一:LFSR

一:任务:

要求使用Verilog语言在Xilinx Virtex-6开发板上实现线性反馈移位寄存器(LFSR)的硬件逻辑设计。

二:前期准备:

基本上完成一个简单的设计需要用到以下几个软件

逻辑:Uedit32(硬件狗吐血推荐)

综合:ISE14.1

仿真:Modelsim SE 10.1b

分析:Chipscope Pro

三:设计流程

逻辑:

首先当然是RTL级设计,俗称硬件逻辑设计。使用的是Uedit32,这个软件相当于一个记事本,但编辑功能十分强大,简直是写Verilog代码的神器,具体下载安装,使用技巧详见(http://blog.163.com/bubble_fish/blog/static/23724712920146180178713/)。 见识了Uedit32的方便快捷后,在写代码之前,小编给大家说几个注意事项。工作过的朋友肯定知道,公司里是很强调代码书写规范的,特别是对于大的设计。如果不按规范做,一个月后调试发现错误,回头再看自己写的代码,估计很多信号都忘了,更不要说检错了;如果一个项目做了一半离职了,接班的人估计得从头开始设计;如果在原版本基础上增加新功能,很可能也要从头来过,很难做到设计的可重用性。这里有一份组长在我第一天实习时就给我的Verilog书写规范,分享给大家,真心希望跟我一样的小白在写代码之前仔细阅读(http://blog.163.com/bubble_fish/blog/static/237247129201461692652979/)。了解书写规范后,我们对任务进行分析。线性反馈移位寄存器(LFSR)的工作原理及应用详见博文(http://blog.sina.com.cn/s/blog_62d9edac01015lsd.html)。以下是Verilog源码:

module LFSR

(

input usr_clk, //时钟

input rst, //复位

output reg [:] dout //data_out

); parameter INIT = 'h1; //初始值

parameter COFF = 'h4; //生成多项式 reg [:] dout_next;

always @ (posedge usr_clk or posedge rst)

if(rst) dout <= INIT;

else dout <= dout_next; integer i;

always@(*)

begin

dout_next[] <= dout[];

for(i=; i<; i=i+)

if(COFF[-i]) dout_next[i] <= dout[i-]^dout[];

else dout_next[i] <= dout[i-];

end endmodule

综合:

对于xilinx的开发板,使用ISE做为综合工具。软件的使用方法不作介绍,网上一搜一大把。这里只给大家留一个附件,包含全部工程文件和.ucf用户约束(http://download.csdn.net/download/yuzeren48/7644573)。

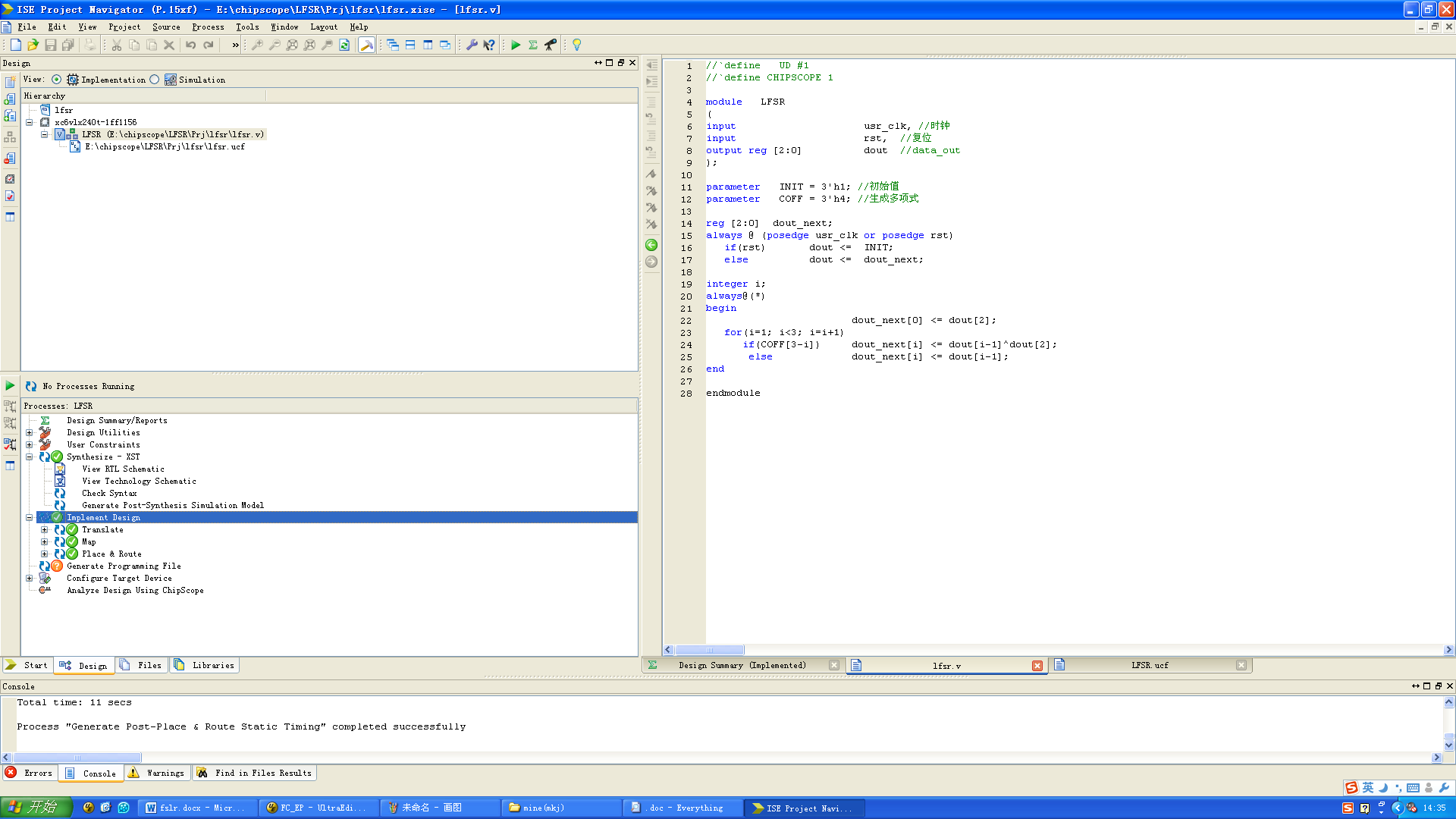

图1:综合界面

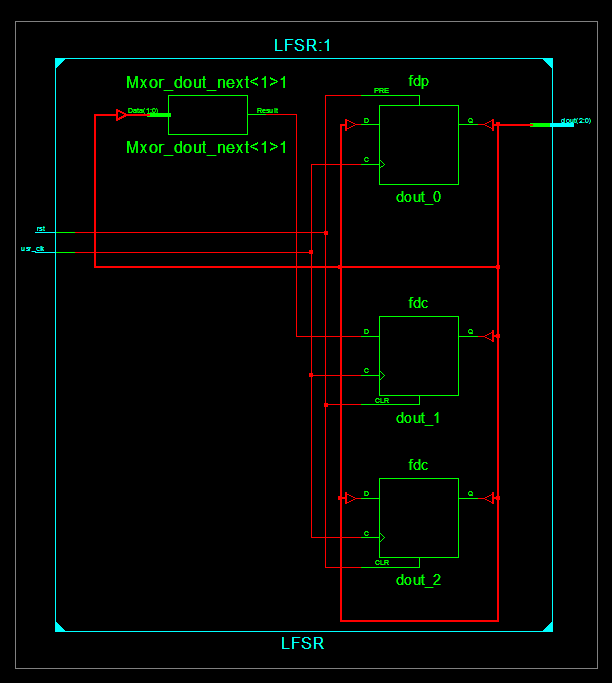

根据LFSR工作原理加上自己定义的参数COFF(3’b100),可知整个LFSR是由一个异或门和三个触发器构成,我们点开Synthesize-XST下的View RTL Schematic,即可看到由代码生成的门级电路,与预期一致。

图2:RTL Schematic

仿真:

ISE是自带仿真软件Isim的,但实际使用效果不是很好。所以我们采用更专业的modelsim来做仿真。Modelsim的具体安装、配置说明详见(请自行百度,如有问题请留言小编)。配置好modelsim后,我们需要写一个testbench来对我们刚才的设计做验证,testbench的作用其实就是给原设计添加各种输入激励信号,然后观察输出信号的波形。具体怎么写testbench请自行百度《编写高效率的testbench》。这里给出本设计的testbench源码

`timescale ns / ns module lfsr_tb; reg rst;

reg usr_clk;

wire [ : ] dout ; LFSR UUT (

.rst (rst),

.usr_clk (usr_clk),

.dout (dout)

); always # usr_clk = ~usr_clk; 17 initial begin

$display("lfsr_tb start...");

rst = ;

usr_clk = ;

#;

rst = ;

#;

$stop;

end endmodule

下面小编给大家简单写一下modelsim的仿真步骤。

1、 新建一个Sim文件夹,将需要用到的源文件文件,testbench文件(.h .v)放进去

2、 打开modelsim,File-New-Project

3、 把目录指定为刚才建好的文件夹,添加.v文件到Project中

4、 对Project中的.v文件右键,选择Compile-Compile All

5、 选择Library标签,找到work,点击+展开

6、 对已经编译好的.v文件右键,选择simulate without optimization

7、 此时会弹出Sim标签栏,对要仿真的文件右键,选择Add wave

8、 设定仿真时间,例如1000ns

9、 点击工具栏按钮Run

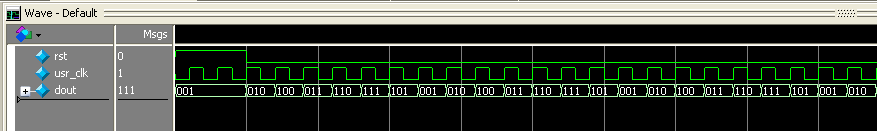

图3展示LFSR仿真结果

图3: LFSR仿真波形

分析:

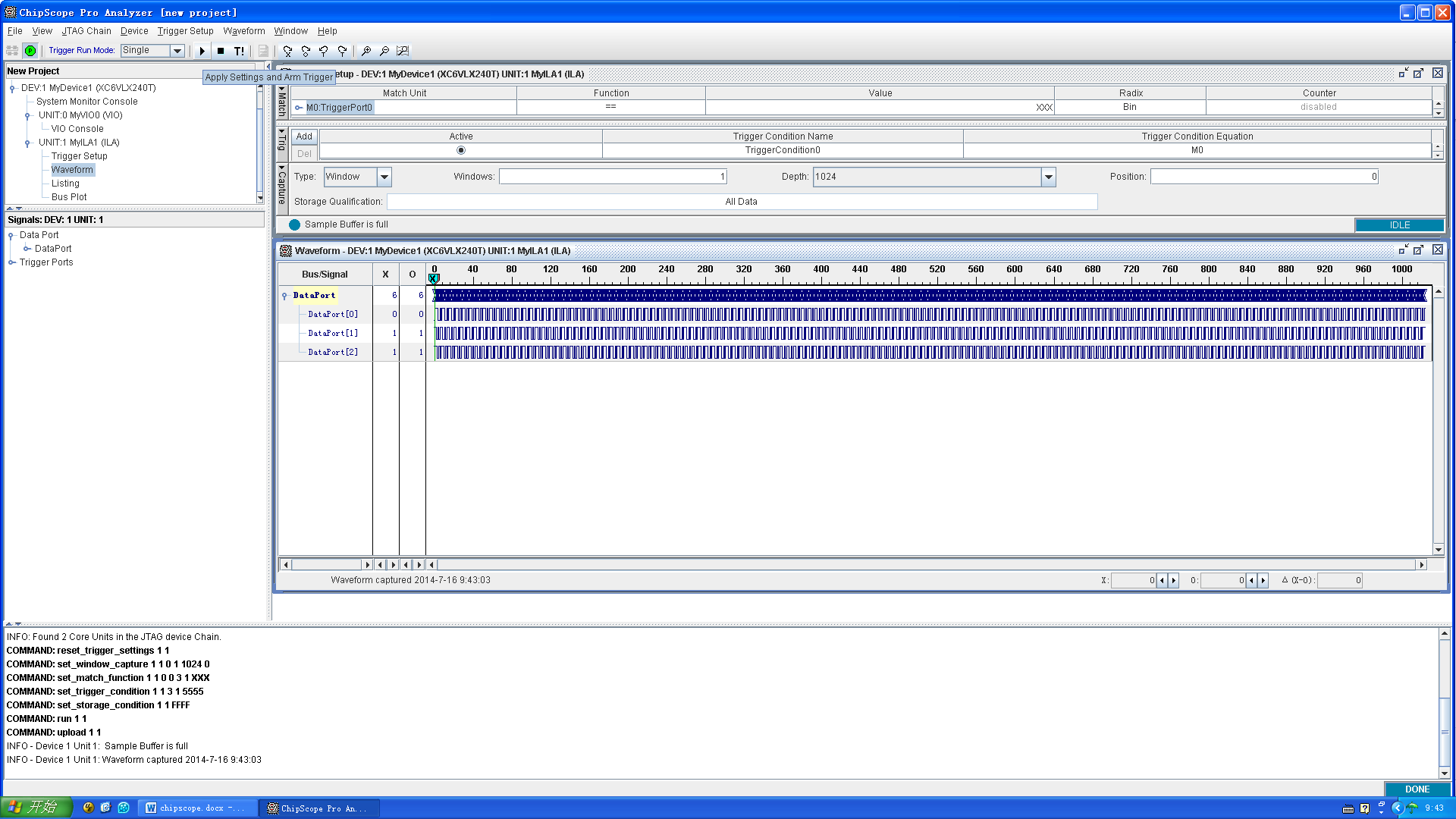

分析用到的软件主要是Chipscope pro,Chipscope的使用方法详见(百度文库搜索“ChipScope Pro实例教程”)。它跟modelsim的主要区别在于这是真正的板级调试。我们需要根据不同的开发板编写用户约束文件(.ucf),经过ISE综合,布局布线后生成bit文件写入FPGA。ChipScope Pro 的主要功能是通过JTAG 口、在线实时地读出FPGA 的内部信号。这里就有一个问题产生:为什么要用ChipScope来观察信号?我们把输入信号直接连上LED,观察LED的亮灭不就知道信号是怎么跳变的吗?小编就用我们刚编写的实例来简单解释一下这个问题:我们开发板使用的时钟信号是33MHz,dout在每个时钟上升沿都会发生一次跳变,一秒钟会发生33000000次跳变,这种高速跳变肉眼无法分辨,所以根本无法通过LED的亮灭来观测dout变化。图4左上角即为LED显示的dout变化。

图4 板级调试

针对本次设计任务,尽可能多的说明chipscope的用途。决定同时使用ICON核、ILA核、VIO核来分析输入输出信号。具体的操作步骤详见博文(http://blog.163.com/bubble_fish/blog/static/237247129201461682452592/)。图5为检测到的数据波形。

图5 chipscope抓包截图

FPGA入门实例一:LFSR的更多相关文章

- React 入门实例教程(转载)

本人转载自: React 入门实例教程

- struts入门实例

入门实例 1 .下载struts-2.3.16.3-all .不摆了.看哈就会下载了. 2 . 解压 后 找到 apps 文件夹. 3. 打开后将 struts2-blank.war ...

- Vue.js2.0从入门到放弃---入门实例

最近,vue.js越来越火.在这样的大浪潮下,我也开始进入vue的学习行列中,在网上也搜了很多教程,按着教程来做,也总会出现这样那样的问题(坑啊,由于网上那些教程都是Vue.js 1.x版本的,现在用 ...

- wxPython中文教程入门实例

这篇文章主要为大家分享下python编程中有关wxPython的中文教程,分享一些wxPython入门实例,有需要的朋友参考下 wxPython中文教程入门实例 wx.Window 是一个基类 ...

- Omnet++ 4.0 入门实例教程

http://blog.sina.com.cn/s/blog_8a2bb17d01018npf.html 在网上找到的一个讲解omnet++的实例, 是4.0下面实现的. 我在4.2上试了试,可以用. ...

- Spring中IoC的入门实例

Spring中IoC的入门实例 Spring的模块化是很强的,各个功能模块都是独立的,我们可以选择的使用.这一章先从Spring的IoC开始.所谓IoC就是一个用XML来定义生成对象的模式,我们看看如 ...

- FPGA入门1

FPGA入门知识介绍 近几年来,由于现场可编程门阵列(FPGA)的使用非常灵活,又可以无限次的编程,已受到越来越多的电子编程者的喜爱,很多朋友都想学习一些FPGA入门知识准备进行这个行业,现在关 ...

- Node.js入门实例程序

在使用Node.js创建实际“Hello, World!”应用程序之前,让我们看看Node.js的应用程序的部分.Node.js应用程序由以下三个重要组成部分: 导入需要模块: 我们使用require ...

- Java AIO 入门实例(转)

Java7 AIO入门实例,首先是服务端实现: 服务端代码 SimpleServer: public class SimpleServer { public SimpleServer(int port ...

随机推荐

- java变量常量

1. java 变量遵循先声明,再赋值,后使用的原则. 一个变量可以只声明,不赋值,没有问题(只是这个变量没有实际意义,但完全没有问题).但如果想要使用它,那么就一定要给它赋值,而大多数时候我们又不知 ...

- shrio的简单认识

博客讲解; shrio的知识储备 shrio的简单认识 笔记整理地址: Shrio.pdf 下载 Shrio理论.doc 下载 shrio知识储备.doc 下载

- armel和armhf区别

出于低功耗.封装限制等种种原因,之前的一些ARM架构处理器因为内部资源宝贵,加入浮点运算单元是十分奢侈的,因为需要额外的软件实现.之前的ARM处理器架构是什么样的?(http://www.cnblog ...

- MySQL InnoDB锁机制之Gap Lock、Next-Key Lock、Record Lock解析

MySQL InnoDB支持三种行锁定方式: l 行锁(Record Lock):锁直接加在索引记录上面,锁住的是key. l 间隙锁(Gap Lock):锁定索引记录间隙,确保索引记录的间隙 ...

- Django的model中创建表

类中的class Meta字段的作用: 第一个作用可以给这个类起名字 在后台的admin中显示这个类名字 class CourseCategory(models.Model): "" ...

- [UI] Elastic Stack & scrollReveal.js

Elastic Stack & scrollReveal.js Elastic Stack http://freebiesbug.com/code-stuff/elastistack-js-d ...

- TreeSet集合的add()方法源码解析(01.Integer自然排序)

>TreeSet集合使用实例 >TreeSet集合的红黑树 存储与取出(图) >TreeSet的add()方法源码 TreeSet集合使用实例 package cn.itca ...

- November 28th 2016 Week 49th Monday

You only live once, but if you do it right, once is enough. 年华不虚度,一生也足矣. One today can win two tomor ...

- You may experience an access violation when you access an STL object through a pointer or reference in a different DLL or EXE

Symptoms When accessing an STL object created in one DLL or EXE through a pointer or reference in a ...

- PHP设计模式系列 - 工厂模式

工厂模式 提供获取某个对象实例的一个接口,同时使调用代码避免确定实例化基类的步骤. 工厂模式 实际上就是建立一个统一的类实例化的函数接口.统一调用,统一控制. 工厂模式是php项目开发中,最常用的设计 ...