lower power的IP设计

在IP的实现过程中,考虑lower power部分进行设计:

1)Partition the design来满足lower power的一些strategies,尤其是power gating和clock gating。

2)为power gating增加额外的逻辑。

3)设计clock和reset的strategy来配合lower power设计。

lower power memory可能需要好多mode:normal operating mode,retention mode,power off。

其中retention mode工作在一个低电压下,retain data。

针对power gating,在IP设计中需要注意:

1)区分power gating和power always on的block。

2)设计power controller控制power up和power down的sequence。(一般在IP外的一个aon模块中)

3)区分signal需要做isolate处理。

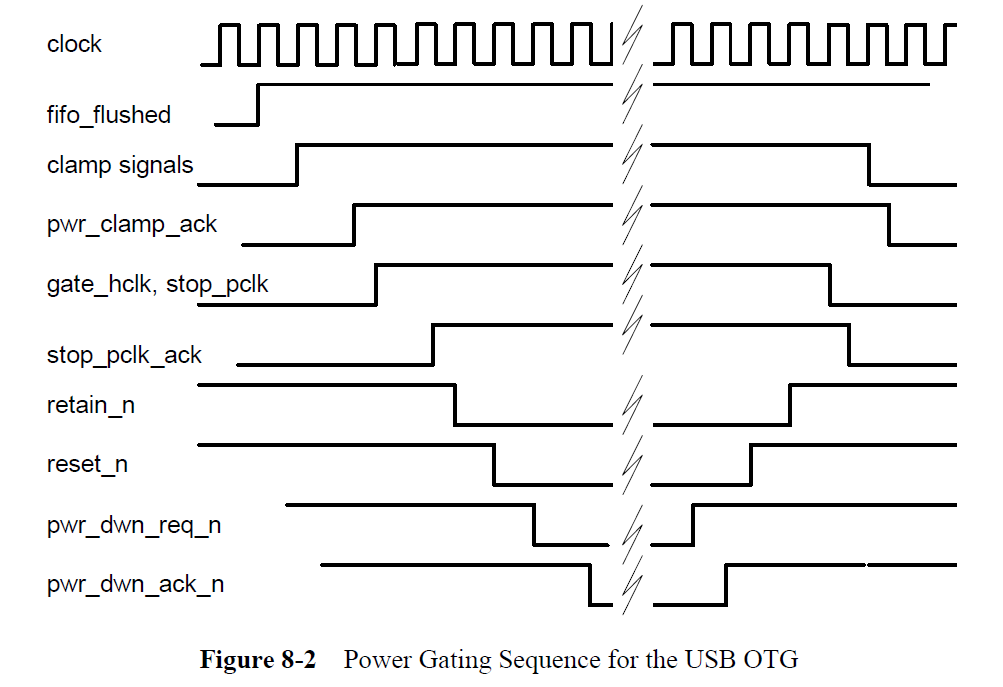

一般的power down和power up的sequence操作:

1)判断transaction和fifo都已为空。

2)停止clock。

3)针对isolate信号,进行clamp操作。

4)进retention操作。

5)复位IP。

6)关掉power。

上电过程中,会在clock之前进行一个rst,在经过clock的sync之后,才会被撤销。 异步复位的rst端口是电平触发,可以保证rst的成功。

但是仿真器中的X->0行为不确定。 掉电区域的clock,必须有一个clock的eb信号默认为有效,这样在上电后,可以保证有clock。

但是clock的频率需要再用该clock或者其他有电的clock进行配置。

rst的sync,只在存在cdc issue的问题上才会做。 同一个clock group上的clock,不需要做sync,不存在相位差。

上电过程中很多其他的clock的enable信号也必须是默认有效的,或者bus上的clock的enable信号默认有效。

1)从pmu过来的rst会进行同步; 2)Bus相关的rst会由bus的clock来同步; 3)Module相关的rst会由自己的clock来同步;

在rtl的simulation过程中,在power down之后,force register的输出为X,来进行仿真。

在gate-simulation过程中,可以建立一个switching fabric的model来进行仿真,还可以得到power up/down时间。

一个power gating的IP的框图,其中的pwr_switch在综合后加入。

lower power的IP设计的更多相关文章

- Power Gating的设计(模块二)

针对lower power的验证,由cpf/upf来建模,包括: 1)power gating的功能模型(在power gate之后将output force为x) 2)isolation功能模型: ...

- Lower Power with CPF(三)

常用的一些Lower Power的策略: 1)Clock tree optimization and clock gating:在正常情况下clock信号会一直toggle at the maximu ...

- Lower Power with CPF(二)

CPF文件可以有两种组织方式:Flat CPF file or Hierarchical CPF file. 由于在大型的SoC设计中,一般都采用Hierarchical的形式,所以本文主要按这个方式 ...

- Power Gating的设计(概述)

Leakage power随着CMOS电路工艺进程,功耗越来越大. Power Domain的开关一般通过硬件中的timer和系统层次的功耗管理软件来进行控制,需要在一下几方面做trade-off: ...

- 一步一步学ZedBoard & Zynq(四):基于AXI Lite 总线的从设备IP设计

本帖最后由 xinxincaijq 于 2013-1-9 10:27 编辑 一步一步学ZedBoard & Zynq(四):基于AXI Lite 总线的从设备IP设计 转自博客:http:// ...

- Lower Power with CPF(四)

CPF从Front-end到Back-end(RTL--GDSII)的整个流程: 1)Creating a CPF file:来在前端就建立lower power的规范. 2)检查CPF文件的正确性, ...

- lower power设计中的DVFS设计

Pswitch = Ceff * Vvdd^2*Fclk, Pshort-circuit = Isc * Vdd * Fclk, Pleakage = f(Vdd, Vth, W/L) 尽管对电压的s ...

- Power Gating的设计(架构)

switching network的层次: 一般选择flatted的形式,hierarchy的结构对voltage drop和performance delay有影响. Power network的结 ...

- Power Gating的设计(模块)

Switching Fabric的设计: 三种架构:P沟道的switch vdd(header switch),N沟道的switch vss(footer switch),两个switch. 但是如果 ...

随机推荐

- git 初次使用

其实知道git很久了,也一度看了不少资料来学习指令.但是一直不明白到底我该咋办,我最疑惑的地方在于,本地代码是如何存储到远程服务器上的,那些指令在什么环境下执行,其实主要是目录问题.就是我在git s ...

- SQL重要命令

SQL对大小写不敏感:SELECT与select是相同的. SQL语句的分号:分号是在数据库系统中分隔每条 SQL 语句的标准方法,这样就可以在对服务器的相同请求中执行一条以上的 SQL 语句. SE ...

- iOS 应用程序的生命周期(转CocoaChina)

对于iOS应用程序,关键是要知道你的应用程序是否正在前台或后台运行.由于系统资源在iOS设备上较为有限,一个应用程序必须在后台与前台有不同的行为.操作系统也会限制你的应用程序在后台的运行,以提高电池寿 ...

- 【转】C语言中标识符的作用域、命名空间、链接属性、生命周期、存储类型

参考网址:http://blog.csdn.net/zhanglianpin/article/details/41575849 绝对的经典.

- RHEL6解决无法使用YUM源问题

RHEL的YUM源需要注册用户才能更新使用,由于CentOS和RHEL基本没有区别,并且CentOS已经被REHL收购.所以将RHEL的YUM源替换为CentOS即可.问题如下:[root@bogon ...

- ESXI

ESXI设置时间 esxi设置时间命令:Usage: esxcli system time set [cmd options] Description: set ...

- Volume rendering

Volume rendering Reconstruction filter UCDAVIS

- procps包里面的sysctl命令

procps包里面的sysctl命令 --http://www.cnblogs.com/createyuan/p/3740917.html?utm_source=tuicool&utm_med ...

- tomcat 禁用不安全的http请求模式 .

HTTP服务器至少应该实现GET和HEAD方法,其他方法都是可选的.当然,所有的方法支持的实现都应当符合下述的方法各自的语义定义.此外,除了上述方法,特定的HTTP服务器还能够扩展自定义的方法. ht ...

- Nginx负载均衡和LVS负载均衡的比较分析

LVS和Nginx都可以用作多机负载的方案,它们各有优缺,在生产环境中需要好好分析实际情况并加以利用. 首先提醒,做技术切不可人云亦云,我云即你云:同时也不可太趋向保守,过于相信旧有方式而等别人来帮你 ...