我的 FPGA 学习历程(03)—— 使用 Quaruts 自带仿真工具

在上一篇中详细的介绍了怎样创建原理图工程,这篇同样使用原理图工程新建一个多路选择器,目的是学习使用图形输入的仿真工具输入仿真激励。

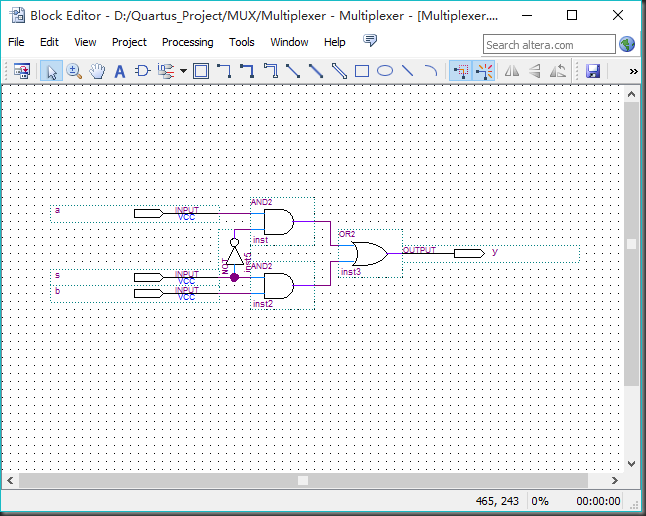

新建工程,并绘制以下的原理图。

编译项目,会多出一个警告: Critical Warning (169085): No exact pin location assignment(s) for 4 pins of 4 total pins,其大致意思是在目标器件上有四个引脚没有被分配,由于这次我们只用到仿真,不需要下载文件到板子上,因此没有必要去分配管脚。

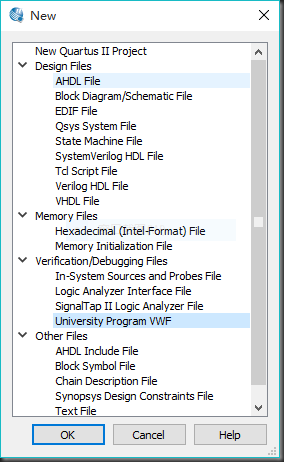

编译成功后新建一个 University Program VWF (仿真波形文件),

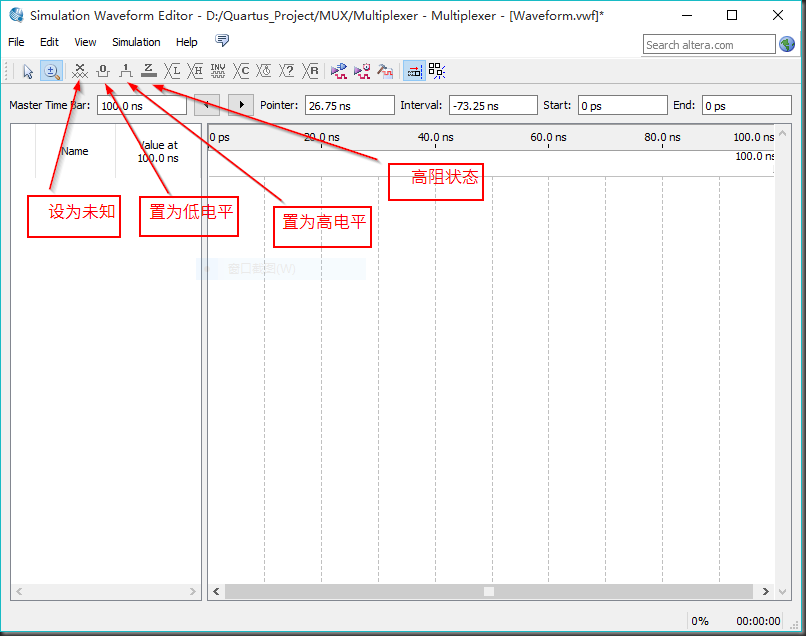

双击主界面 Project Navigator Files 标签下的 waveform.vwf 文件打开仿真波形文件编辑器,如下:

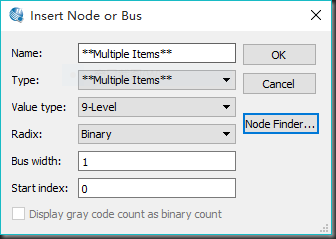

接下来在仿真波形文件编辑器中添加管脚,依次点击 Edit –> Insert –> Insert Node or Bus,再点击下图中的 Node Finder...

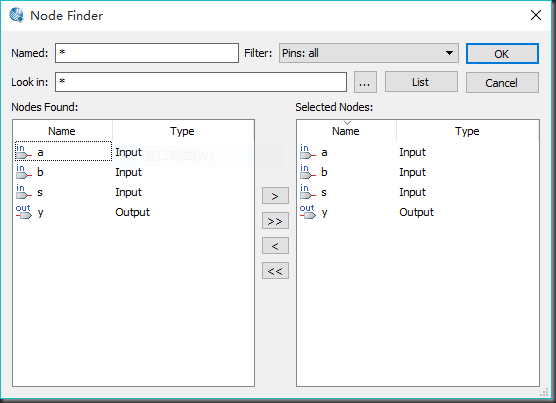

点击 List,图为仿真引脚的选择工具,这里我们需要添加所有的引脚。完成后点 OK。

再点一次 OK

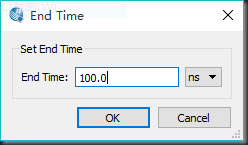

完成引脚添加工作,接下来在 Edit --> Set End Time 中设定仿真时间,由于该编辑器的一个格子是 10 ns,这里我们设为 100 ns。

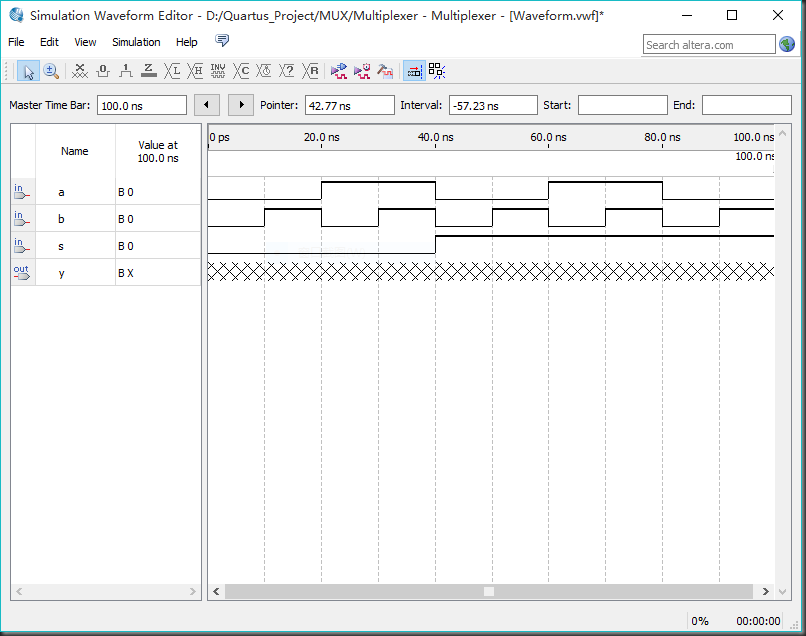

选择需要修改的时间段,修改为需要的高低电平,修改到下面这个样子就可以了(*^__^*)。

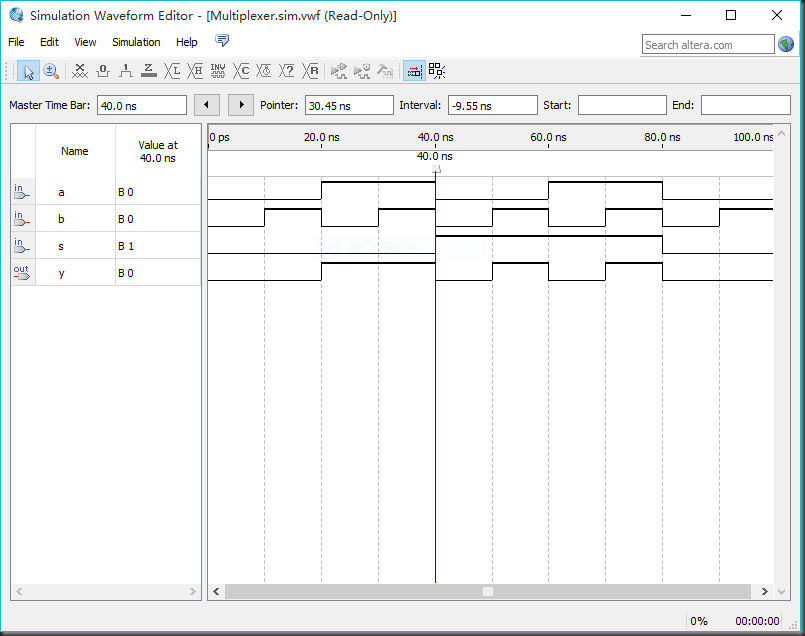

接下来点击 Simulation –> Run Function Simulator 进行逻辑仿真。仿真结果如下:

可以看到,当 s = 0 时, y = a;当 s = 1 时,y = b。

仿真验证了我们的设计是正确的。O(∩_∩)O 同样还可以使用 verilog 语言描述一个多路选择器,verilog 代码如下,各位可以试试。

module mymux

(

input wire a, //这里是逗号

input wire b,

input wire s,

output reg y //这里没有逗号

); //这里是分号 //**************************************************//

always @ (*) //敏感信号列表,初学者打星号就可以了

begin

if(s=='b0) //两个等号表示判断是否相等

y = a;

else

y = b;

end

//*************************************************// endmodule

我的 FPGA 学习历程(03)—— 使用 Quaruts 自带仿真工具的更多相关文章

- 我的 FPGA 学习历程(05)—— 使用 Modelsim 仿真工具

在第 3 篇中讲到了如何使用图形进行仿真激励输入,图形输入法尽管简单易学,但如若要求复杂的仿真输入激励.较长的仿真时间或是要求打印输出信息乃至输出文件日志则显得不够用了. 本篇以上一篇的 3-8 译码 ...

- 我的 FPGA 学习历程(01)—— FPGA 基础知识和 Quartus 的安装

高级的嵌入式市场主要分为以下三类:ARM.DSP 和 FPGA. 其中 ARM 是行业内的佼佼者,目前几乎所有的安卓智能手机都使用 ARM 授权的 CPU架构:而 DSP(数字信号处理器) 早年就被大 ...

- 我的 FPGA 学习历程(09)—— 时序逻辑入门

讲到这篇时,组合逻辑就告一段落了,下面是一些总结: 描述组合逻辑时,always 语句中的敏感信号列表中需要列出全部的可能影响输出的变量 描述组合逻辑时,always 语句中的赋值总是使用阻塞赋值符号 ...

- 我的 FPGA 学习历程(02)—— 实验:点亮 LED 灯

关于 Quartus 的操作可以使用 Quartus 自带的帮助,帮助中带有全套的操作教程. 中文网络教程链接(链接至 altera中文官网,点击观看) Quartus II 软件设计系列:基础 Qu ...

- 我的 FPGA 学习历程(14)—— PWM 脉冲宽度调制

PWM 是一种调节输出功率的技术(俗称调压),其原理在于改变输出方波的占空比,具体输出见下图: 输出信号为电压值,当负载为恒阻时,上图中的输出功率分别为 25%.50%.75%. 实现方法如下: 设置 ...

- 我的 FPGA 学习历程(12)—— 电子钟项目准备

初学 FPGA 的时候,我们总是存在很多疑问,比如:xilinx 和 altera 的 FPGA 那种比较好.verilog 语言被如何综合成具体硬件电路.RTL 级电路是什么意思等等.现在我们就不会 ...

- 我的 FPGA 学习历程(11)—— 实验:按键消抖

按键是一个输入设备,在理论上可以归为开关一类,理想的按键波形如下: 然而由于按键的机械特性,断开和闭合动作是不可能在一瞬间完成的,实际的波形如下: 抖动期间电平处于临界值,由于晶振的频率相当的高,数字 ...

- 我的 FPGA 学习历程(08)—— 实验:点亮单个数码管

数码管是一种常见的用于显示的电子器件,根据数码管大致可以分为共阴极和共阳极两种,下图所示的是一个共阳极的数码管的电路图(摘自金沙滩工作室的 51 开发板电路图),我的 AX301 开发板与这张图的情况 ...

- 我的 FPGA 学习历程(07)—— BCD 编码:移位加 3 算法

2-10 进制码,也称为 BCD 码,它的编码方式则是通过一个 4 位二进制来表示一个 10 进制数,部分十进制对应的 BCD 码如下 十进制数 | BCD 码 13 --> 0001_0011 ...

随机推荐

- Maven pom文件标签解析大全

<span style="padding:0px; margin:0px"><project xmlns="http://maven.apache.or ...

- django-url的分发

1)url的分发: 1,首先在全局的url里面的路径中写好,你要分发的路径名. 2,并且在你要分发的路径下,创好新的url文件. 在分发的路径名里面,把全局url里面的代码,复制过来 3,最后在浏览器 ...

- WinForm文件说明

以上位置,双击即可. 界面可以通过拖动控件,也可以通过背后的界面代码去布局. 如果删除了事件代码,界面可能报错,因为界面代码中有未删除的残余(波浪线提示处代码,直接删除即可). 对于多个窗体,Prog ...

- ZooKeeper 概述

ZooKeeper:分布式应用程序的分布式协调服务 ZooKeeper:是用于分布式应用程序的分布式开源协调服务 可以简单理解:ZooKeeper = 文件系统 + 通知机制 从设计模式角度理解:Zo ...

- Spark Java API 之 CountVectorizer

Spark Java API 之 CountVectorizer 由于在Spark中文本处理与分析的一些机器学习算法的输入并不是文本数据,而是数值型向量.因此,需要进行转换.而将文本数据转换成数值型的 ...

- 乘积型Sobolev不等式

(Multiplicative Sobolev inequality). Let $\mu,\lambda$ and $\gamma$ be three parameters that satisfy ...

- Spring基础4

一.Spring的JDBC模板 Spring对持久层也提供了解决方案,ORM模块和JDBC模板 提高简化JDBC或Hibernate的模板 二.JDBC模板使用入门 1)引入jar包:Spring开发 ...

- 【归纳】正则表达式及Python中的正则库

正则表达式 正则表达式30分钟入门教程 runoob正则式教程 正则表达式练习题集(附答案) 元字符\b代表单词的分界处,在英文中指空格,标点符号或换行 例子:\bhi\b可以用来匹配hi这个单词,且 ...

- html 超链接标签 锚点 a标签伪类

一个简易的连接 <a href="01.html">01</a> <body> <a href="01.html" t ...

- 开发portlet中的一些问题记录,portlet:resourceURL用法,portlet中通过processAction方法传值

在portlet页面中引入js或者css,通过c或者s标签 <!--jquery实际放的地方:/MyTask/WebContent/scripts/jquery-1.8.3.min.js--&g ...