Verilog学习笔记简单功能实现(一)...............D触发器

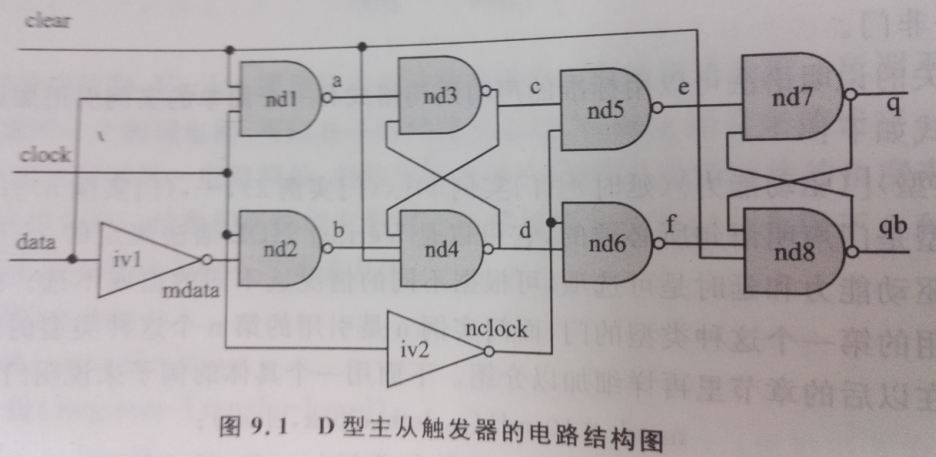

module D_flop(data,clk,clr,q,qb);

input data,clk,clr;

output q,qb;

wire a,b,c,d,e,f,ndata,nclk;

nand nand1(a,clr,data,clk),

nand2(b,ndata,clk),

nand4(d,c,b,clr),

nand5(e,c,nclk),

nand6(f,d,nclk),

nand8(qb,f,clr,q);

nand nand3(c,a,d),

nand7(q,e,qb);

not not1(ndata,data),

not2(nclk,clk);

endmodule

门级电路

上图就是门级Verilog语言描述的对应的网表,由图可以看出这是一个带异步置零的D触发器。

同样我们也可以采用行为描述来定义D触发器。

普通D触发器:

module D_EF(Q,D,CLK)

input D,CLK;

output Q;

reg Q; //在always语句中被赋值的信号要声明为reg类型寄存器定义

always @ (posedge CLK)

begin Q <= D; end

endmodule

异步D触发器:

module D_EF(q,qn,d,clk,set,reset)

input d,clk,set,reset;

output q,qn;

reg q,qn; //寄存器定义

always @ (posedge clk or negedge set or negedge reset)

begin

if(!reset) begin q<=;qn<=;end//异步清0,低有效

else if(!set) begin q<=;qn<=;end //异步置1,低有效

else begin q<=~d;qn<=~d;end

end

endmodule

同步触发器:

module D_EF(q,qn,d,clk,set,reset)

input d,clk,set,reset;

output q,qn;

reg q,qn;

always @ (posedge clk)

begin

if(!reset) begin q<=;qn<=;end//同步清0,低有效

else if(!set) begin q<=;qn<=;end //同步置1,低有效

else begin q<=~d;qn<=~d;end

end

endmodule

注意,异步和同步触发器中else begin q<=~d;qn<=~d;end 更正为else begin q<=d;qn<=~d;end

Verilog学习笔记简单功能实现(一)...............D触发器的更多相关文章

- Verilog学习笔记简单功能实现(二)...............全加器

先以一位全加器为例:Xi.Yi代表两个加数,Cin是地位进位信号,Cout是向高位的进位信号.列表有: Xi Yi Cin Sum Cout 0 0 0 0 0 0 0 1 1 0 ...

- Verilog学习笔记简单功能实现(八)...............同步FIFO

Part 1,功能定义: 用16*8 RAM实现一个同步先进先出(FIFO)队列设计.由写使能端控制该数据流的写入FIFO,并由读使能控制FIFO中数据的读出.写入和读出的操作(高电平有效)由时钟的上 ...

- Verilog学习笔记简单功能实现(六)...............计数分频电路

在分频器电路中最重要的概念有两个:1)奇分频/偶分频:2)占空比. A)其中最简单的就是二分频电路,占空比为50%,其Verilog程序为 module half_clk(clr,clk_in,clk ...

- Verilog学习笔记简单功能实现(五)...............序列检测设计

这里采用夏宇闻教授第十五章的序列检测为例来学习; 从以上的状态转换图可以写出状态机的程序: module seqdet(x,out,clk,rst); input x,clk,rst; output ...

- Verilog学习笔记简单功能实现(三)...............同步有限状态机

在Verilog中可以采用多种方法来描述有限状态机最常见的方法就是用always和case语句.如下图所示的状态转移图就表示了一个简单的有限状态机: 图中:图表示了一个四状态的状态机,输入为A和Res ...

- Verilog学习笔记简单功能实现(四)...............译码器和编码器

这里以简单的3-8译码器和8-3编码器为例: module decoder3_8(a,out); :]a; :]out; 'b1<<a;/*把最低位的1左移in位(根据in口输入的值)并赋 ...

- Verilog学习笔记简单功能实现(八)...............异步FIFO

基本原理: 1.读写指针的工作原理 写指针:总是指向下一个将要被写入的单元,复位时,指向第1个单元(编号为0). 读指针:总是指向当前要被读出的数据,复位时,指向第1个单元(编号为0). ...

- Verilog学习笔记简单功能实现(七)...............接口设计(并行输入串行输出)

利用状态机实现比较复杂的接口设计: 这是一个将并行数据转换为串行输出的变换器,利用双向总线输出.这是由EEPROM读写器的缩减得到的,首先对I2C总线特征介绍: I2C总线(inter integra ...

- IIC驱动学习笔记,简单的TSC2007的IIC驱动编写,测试

IIC驱动学习笔记,简单的TSC2007的IIC驱动编写,测试 目的不是为了编写TSC2007驱动,是为了学习IIC驱动的编写,读一下TSC2007的ADC数据进行练习,, Linux主机驱动和外设驱 ...

随机推荐

- JVM性能分析与优化

JVM性能分析与优化: http://www.docin.com/p-757199232.html

- SQL 操作结果集 -并集、差集、交集、结果集排序

操作结果集 为了配合测试,特地建了两个表,并且添加了一些测试数据,其中重复记录为东吴的人物. 表:Person_1魏国人物 表:Person_2蜀国人物 A.Union形成并集 Union可以对两个或 ...

- POJ 1816 Wild Words

Wild Words Time Limit: 2000MS Memory Limit: 65536K Total Submissions: 4412 Accepted: 1149 Descri ...

- 译:C#面向对象的基本概念 (Basic C# OOP Concept) 第三部分(多态,抽象类,虚方法,密封类,静态类,接口)

9.多态 Ploy的意思就是多于一种形式.在文章开始,方法那一章节就已经接触到了多态.多个方法名称相同,而参数不同,这就是多态的一种. 方法重载和方法覆盖就是用在了多态.多态有2中类型,一种是编译时多 ...

- 30分钟入门Java8之方法引用

30分钟入门Java8之方法引用 前言 之前两篇文章分别介绍了Java8的lambda表达式和默认方法和静态接口方法.今天我们继续学习Java8的新语言特性--方法引用(Method Referenc ...

- JRE和JDK

转自:http://www.cnblogs.com/myitm/archive/2011/05/03/2035942.html 很多程序员已经干了一段时间java了依然不明白jdk与jre的区别. ...

- 关于 iOS 的一些学习资料

iOS.Book.Effective Objective-C 2.0 1. 中文翻译版 (更新中) https://github.com/HagerHu/effective-objective-c-2 ...

- JS对象的几个方法介绍

1.hasOwnProperty 判断是不是对象自身的属性,如果是继承的返回false否则true function Fn(){ } Fn.prototype.num = 10; var obj = ...

- 【分享】Matlab R2015a 发布啦!

本博客所有文章分类的总目录:http://www.cnblogs.com/asxinyu/p/4288836.html Matlab和C#混合编程文章目录:http://www.cnblogs.com ...

- Hadoop入门进阶课程1--Hadoop1.X伪分布式安装

本文版权归作者和博客园共有,欢迎转载,但未经作者同意必须保留此段声明,且在文章页面明显位置给出原文连接,博主为石山园,博客地址为 http://www.cnblogs.com/shishanyuan ...