【接口时序】1、软件与Verilog基本格式规范说明

一、 说明

以前总是没有记录的习惯,导致遇到问题时总得重新回忆与摸索,大大降低了学习效率,从今天开始决定改掉这个坏毛病,认真记录自己的Verilog学习之路,希望自己能一直坚持下去。

二、 软件资源与硬件资源

软件资源说明:

1、UltraEdit:本博客所有的Verilog代码全部都在UltraEdit中编辑, UltraEdit具有语法高亮与自动补全(设置方法在本文最后面)功能,而且界面美观,绝对是写代码的利器。

下载链接:

https://pan.baidu.com/s/15aiPB5Mq0zEY51ftmzFwhA 密码:ebzt

2、ISE14.7或Vivado2016.3:本博客的FPGA选择的是Xilinx的,所以选择Xilinx集成开发套件,本来之前一直在用7系列的FPGA,但是目前手头只有一块Spartan-6系列的二手开发板,所以代码的验证都在Spartan-6上验证,但好在FPGA的结构基本类似,Verilog的代码基本可以通用。

ISE14.7安装包与破解包下载链接:

https://pan.baidu.com/s/1CVGNKZ9tr7dpcDmq3ZhM8Q 密码:zyd2

3、ModelSim-win64-10.4-se:仿真工具使用ModelSim 10.4版本,其他版本也可以,无过多要求。

下载链接:

https://pan.baidu.com/s/1N8nOHDla1G8jx4Q_DGRHcg 密码:371g

4、Windows-7 64-bit系统:建议大家在Windows-7 64-bit系统做开发 ,Windows-7 64-bit系统对以上软件的兼容性都比较好。我的笔记本电脑用的是Windows-8.1系统,安装ISE14.7以后导入ModelSim仿真库,选择库目录的时候出现了卡住的情况,这种就是ISE14.7与WIndows-8.1不太兼容导致的,解决办法如下。

解决Windows-8.1与ISE14.7不兼容的办法:

找到ISE安装目录的中的nt64文件夹,我的ISE的安装目录在D盘,所以nt64的路径如下D:\Xilinx\14.7\ISE_DS\ISE\lib\nt64,然后把nt64文件夹中的libPortability.dll文件名改成libPortability.dll.org,再把libPortabilityNOSH.dll重命名为libPortability.dll。这样可以有效解决一部分兼容性的问题。

5、更多软件资源可以关注文末的微信公众号并输入关键字“软件安装包”获取

硬件资源说明:

1、目前手头只有一块二手的黑金AX545开发板,FPGA的型号是:XC6SLX45-2CSG324,所以代码都会在这个板子上进行验证。对于其他型号的FPGA只要理解原理了应该也不难上手。

三、 Verilog命名规范与格式说明

Verilog语言并没有固定的命名规范与编写格式,每个人根据自己的喜好而定就行了,我自己比较喜欢下面规范与格式。这里先写一部分,后面如果有补充的在加上。

Verilog命名规范:

1、所有输入端口以大写I加下划线开始,然后后面内容的一律用小写,信号比较长的话,后面的小写用下划线隔开。如:

input I_clk;

input I_led_mode;

如果输入端口低电平有效的话就在末尾加下划线和小写n,如:

input I_rst_n;

2、所有输出端口以大写O加下划线开始,然后后面内容的一律用小写,信号比较长的话,后面的小写用下划线隔开。如:

output O_led;

output O_led_mode;

3、所有reg变量以大写R加下划线开始,然后后面内容的一律用小写,信号比较长的话,后面的小写用下划线隔开。如:

reg R_cnt;

reg R_cnt_100ms;

4、所有wire变量以大写W加下划线开始,然后后面内容的一律用小写,信号比较长的话,后面的小写用下划线隔开。如:

wire W_cnt;

wire W_led_mode;

5、所有常量(parameter变量)以大写C加下划线开始,然后后面内容的一律用大写以示与变量的区别,信号比较长的话,后面的大写用下划线隔开。如:

parameter C_IDLE;

parameter C_FLASH_READ;

6、命名一定要有意义,看着变量名就大概能猜出它的作用,并适当采用缩写,下面几个缩写是写代码过程中比较常用的缩写。

‘rd’代替‘read’

‘wr’代替‘write’

‘cnt’代替‘count’

‘rst’代替‘reset’

‘addr’代替‘address’

Verilog编写格式:

1、always块的begin…end换行写,如:

always @(posedge I_clk or negedge I_rst_n)

begin

…

end

2、if…else if…else语句的begin…end换行并空一个Tab键(记得设置一个Tab为4个空格)写,如果if或者else下面只有一条语句那么就省略begin…end如:

if

begin

…

end

else if

begin

…

end

else

…

3、case…endcase语句中的条件后面如果只有一条语句,则直接在冒号后面写语句,default一定要写上,即使里面什么语句也没有。最好用UltraEdit的列模式功能把那些冒号和分号都上下对齐。如

case(...)

C_IDEL : …… ;

C_FLASH : …… ;

default : ;

endcase

case…endcase语句中的条件后面如果有多条语句,则直接在冒号后面换行加Tab键写begin…end。同样用UltraEdit的列模式功能把那些冒号和分号都上下对齐。

case(R_state)

C_IDEL :

begin

…… ;

end

C_ FLASH :

begin

…… ;

end

default :

begin

…… ;

end

endcase

4、例化模块的时候例化名就是在模块名前面加一个大写的U和下划线,并且用UE的列模式功能把括号和逗号都对齐。如:

led_work U_ led_work

(

. I_clk (I_clk ),

. I_rst_n (I_rst_n ),

.O_led_mode (O_led_mode ),

.O_led_out (O_ led_out )

);

附、 UltraEdit设置方法

下载上文的UltraEdit压缩包并解压,里面有两个文件,一个是UE的安装包,一个是语法高亮文件

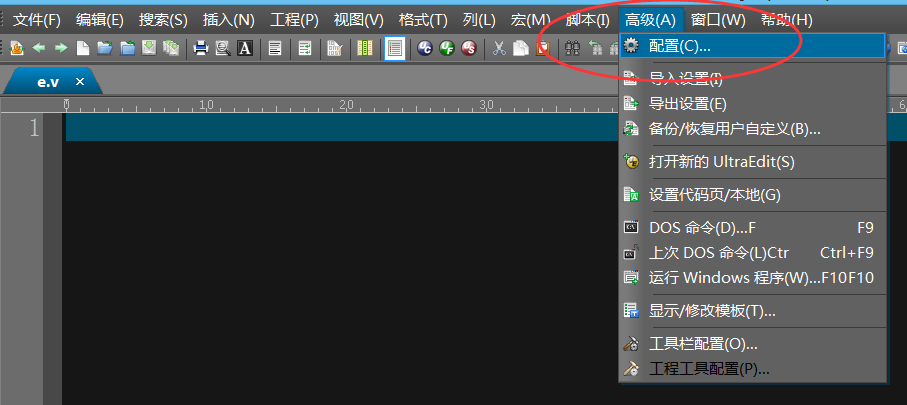

双击exe文件安装好了以后打开UE会提示选择风格,我比较喜欢黑暗风格,选完风格以后在菜单栏找到高级选项卡,然后在高级选项卡下载找到配置菜单

单击配置菜单,弹出如下界面

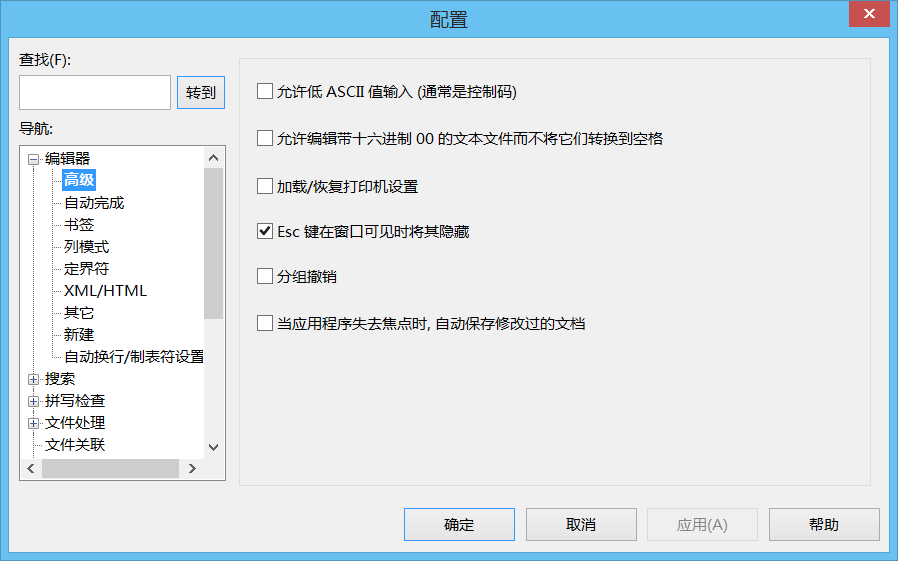

接着在上面的界面中找到自动完成功能并选中,然后按照下图进行设置

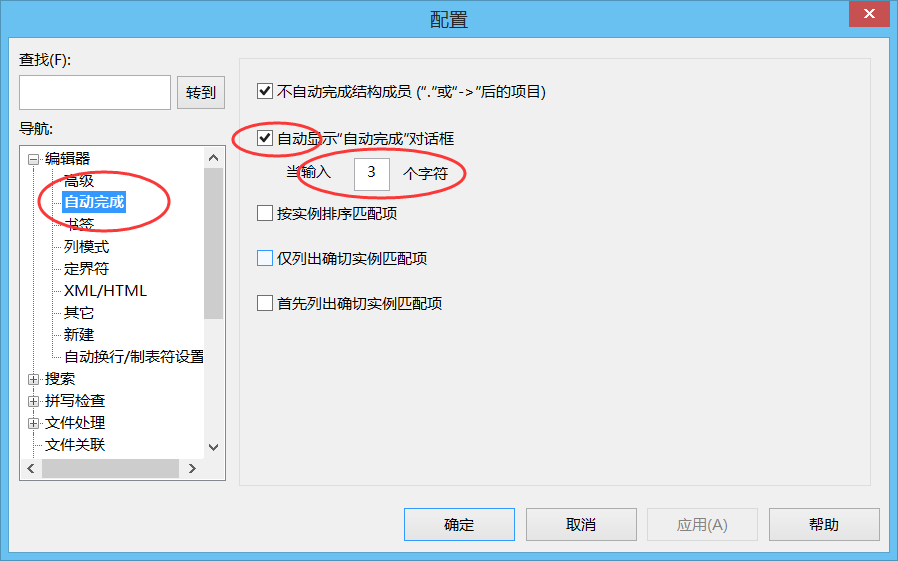

接着在找到自动换行/制表符设置,按照如下方式设置

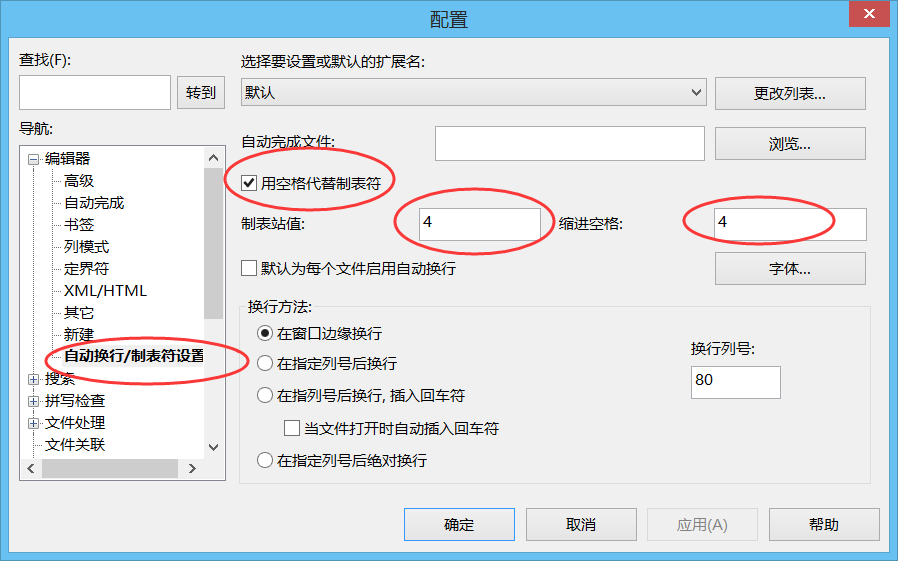

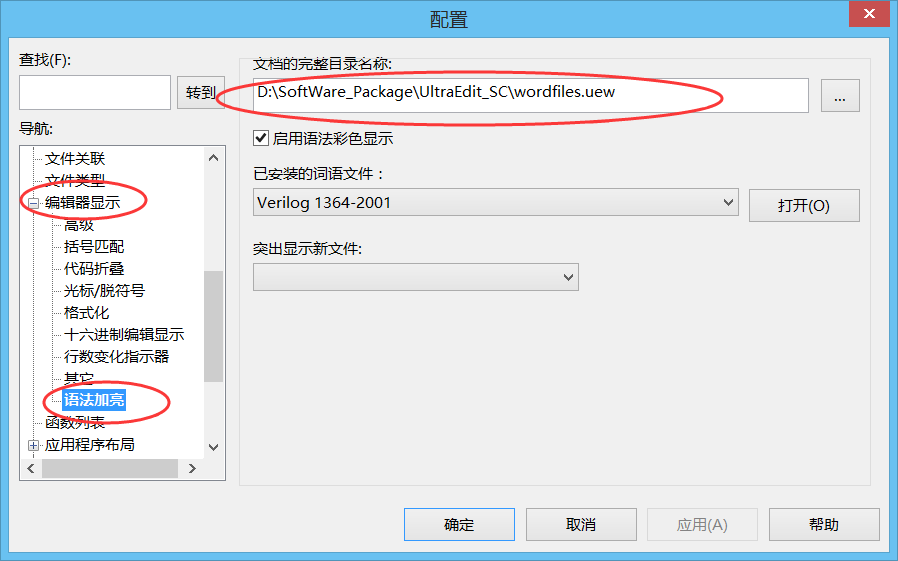

最后找到编辑器显示下面的语法加亮,选择安装包中的wordfile.uew配置文件就OK了,如下图所示

欢迎关注我的公众号:FPGA之禅

【接口时序】1、软件与Verilog基本格式规范说明的更多相关文章

- 【接口时序】2、Verilog实现流水灯及与C语言的对比

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1.FPGA型号:XC6SLX45 ...

- 【接口时序】7、VGA接口原理与Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1. FPGA型号:Xilinx公 ...

- 在现有的图像处理软件中融合dxf格式输出

在现有的图像处理软件中融合dxf格式输出 dxf格式是autocade的支持格式.如果将现有图像识别的结果导出到dxf格式,就能够使用autocad的强大功能进行后续处理. dxf的格式比较复杂,开源 ...

- 明确出需求 然后开会评审 要什么接口 接口参数、返回json内容、格式 协定好 在做

明确出需求 然后开会评审 要什么接口 接口参数.返回json内容.格式 协定好 在做

- 能力不足之 根据时序图转化为Verilog代码

不能够把时序图看的非常透彻,然后把时序图写成Verilog代码,有时候甚至搞不清楚信号之间的时序关系.

- VGA接口时序约束

SF-VGA模块板载VGA显示器DA转换驱动芯片AVD7123,FPGA通过OUPLLN连接器驱动ADV7123芯片产生供给VGA显示器的色彩以及同步信号.SF-CY3核心模块与SF-VGA子模块连接 ...

- OverWatch团队文档格式规范

V1.0 最终修改于2016/10/19 概述 软件工程中,一份优雅的文档不仅能降低团队成员之间的沟通难度,而且能给之后的开发者提供一个非常有效的引导.本团队为了规范整个项目中文档的格式,便于统一管理 ...

- WEB学习笔记4-前端代码基本命名规法和格式规范

1.HTML命名规范及格式规范 标签名和属性应该都小写,虽然HTML代码不区分大小写:属性值应该用双引号闭合. <IMG src=demo.jpg alt='test'/>(N) < ...

- GeoJSON格式规范说明

GeoJSON格式规范说明 1.简介 GeoJSON是一种对各种地理数据结构进行编码的格式.GeoJSON对象可以表示几何.特征或者特征集合.GeoJSON支持下面几何类型:点.线.面.多点.多线.多 ...

随机推荐

- background url base64

各自含义:data: ----获取数据类型名称image/gif; -----指数据类型名称base64 -----指编码模式AAAAA ------指编码以后的结果. background-imag ...

- 关于php查询mongodb限制返回字段的问题

最近想做一个前端控制接口字段返回的一个基础方法,通过mongodb 的find($query,$field)查询来规定查询的字段,但是遇到这么一个问题: 工作代码中有两个封装方法 : /** * 查询 ...

- 总结http状态码和200,304状态码

状态码 响应类别 中文意思 1XX 信息性状态码(Informational) 服务器正在处理请求 2XX 成功状态码(Success) 请求已正常处理完毕 3XX 重定向状态码(Redirec ...

- React Native在window下的环境搭建(一)

React Native官方开发文档 以下是本人抄录的: 初次接触React Native感觉和React很像,却是有点类似,但不完全是,React Native有自己的组件对象,不过它也自定义的组件 ...

- jquery 中后代遍历之children、find区别

jquery 中children.find区别 首先看一段HTML代码,如下: <table id="tb"> <tr> <td>0</t ...

- IntelliJ IDEA——SVN的配置及使用

服务端:VisualSVN-Server-3.9.1-x64 下载地址:https://www.visualsvn.com/server/download/ TortoiseSVN 安装 下载地址:h ...

- lvs+nginx负载均衡

1 学习目标 掌握什么是负载均衡及负载均衡的作用和意义. 了解lvs负载均衡的三种模式. 了解lvs-DR负载均衡部署方法. 掌握nginx实现负载均衡的方法. 掌握lvs+nginx负载 ...

- EOS踩坑记 2

[EOS踩坑记 2] 1.--contracts-console 在开发模式下,需要将 nodeos 添加此选项. 2.Debug Method The main method used to deb ...

- Pandas排列和随机采样

随机重排序 import pandas as pd import numpy as np from pandas import Series df = pd.DataFrame(np.arange(5 ...

- 微信小程序记账本进度二

二.1,下载微信web开发者工具 2,使用新注册的账号登录,并创建工程