verilog利用线性插值实现正弦波生成器(dds)

verilog实现线性插值实现正弦波生成器

最近在项目上遇到一个需要在低资源FPGA上实现FFT逻辑的项目,而且要求实现窗函数。对于窗函数来说,莫非是实现正弦波生成器,正弦波生成器可以利用DDS模块,CORDIC模块,或者查找表的方式实现,以下主要讲解ROM核线性插值相结合的波形生成器,用于生成正弦波。

1.线性插值

线性插值是一种数据估值算法,由于其拟合线是一条直线,所以叫做线性插值。即通过需要估值点的左右两个点的权重以及距离,对估值点的权重进行计算的一种算法。

由于估值拟合线是直线那么,已知(x0,y0)和(x1,y1),以及x到两点的距离,对y进行计算。

&\frac{y_1-y_0}{x_1-x_0} = \frac{y-y_0}{x-x_0} \\ &y = y_0 + \frac{(y_1-y_0)*(x-x_0)}{x_1-x_0}

\end{split}

\]

对正弦函数进行估值:

其中(x,y)表示估算值,(x2,y2)表示真实值,误差为y2-y,即当x1-x0越小,估算值越准确。样本点越多越精确。

2.样本生成

以下matlab代码用于生成正弦函数样本值,用于进行数据估算。

clc,clear,close all

%% 生成 rom 数据

Width=16;

Depth=256;

phi=linspace(0,2*pi,Depth+1);

phi=phi(1:end-1)';

cos_sig=cos(phi);

cos_sig=floor(cos_sig*(2^(Width-1)-1));

plot(cos_sig)

%% 生成.coe文件

filename='.\cos_rom.coe';

fid = fopen(filename,'w');

radix = 10;

fprintf(fid,"memory_initialization_radix=%d;\n",radix); %使用的进制

fprintf(fid,"memory_initialization_vector=");

for i=1:size(cos_sig,1)

fprintf(fid,"\n%d",cos_sig(i));

end

fprintf(fid,";");

fclose(fid);

3.verilog实现线性插值

以下将使用参数:样本深度256,相位最大值65536进行讲解。

对某一个点进行线性估值的时候,我们需要知道当前点在样本中对应相应点的邻近点。样本邻近两点相位差65536/256 = 256,假设插值相位位置为phase,则相邻点为floor(phase/256)和floor(phase/256)+1,floor表示向下取整,rom表示查找表数据。

那么

y = y_0 + \frac{(y_1-y_0)*(x-x_0)}{x_1-x_0}

= rom(floor(phase/256)) + \frac{(rom(floor(phase/256) + 1)-rom(floor(phase/256)))*(phase-floor(phase/256)*256)}{256}

\end{equation}

\]

以下为VERILOG代码实现:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2025/03/29 15:47:50

// Design Name:

// Module Name: cos_gen_pipeline

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module cos_gen_pipeline(

input clk ,

input rst ,

input valid ,

input [15:0] phase , //相位,0~65535对应0~2pi)

output rdy ,

output reg [15:0] cos_out

);

reg [4:0] valid_d;

always @(posedge clk) begin

if(rst)begin

valid_d <= 0;

end else begin

valid_d <= {valid_d[3:0],valid};

end

end

assign rdy = valid_d[4];

wire [7:0] addr1;

wire [7:0] addr2;

wire signed [15:0] cos_dat1;

wire signed [15:0] cos_dat2;

wire [15:0] phase1;

//-----------线性插值-----------------------------

assign addr1 = (phase>>8) ;

assign addr2 = (phase>>8)+1 ;

assign phase1 = addr1<<8 ;

cos_rom cos_rom_inst1(

.clka (clk ),

.addra (addr1 ),

.douta (cos_dat1 )

);

cos_rom cos_rom_inst2(

.clka (clk ),

.addra (addr2 ),

.douta (cos_dat2 )

);

reg [15:0] phase_d0 ;

reg [15:0] phase_d1 ;

reg [15:0] phase1_d0 ;

reg [15:0] phase1_d1 ;

always @(posedge clk) begin

if(rst)begin

phase_d0 <= 0 ;

phase_d1 <= 0 ;

phase1_d0 <= 0 ;

phase1_d1 <= 0 ;

end else begin

phase_d0 <= phase ;

phase_d1 <= phase_d0 ;

phase1_d0 <= phase1 ;

phase1_d1 <= phase1_d0 ;

end

end

reg [31:0] multi;

reg [15:0] delta_cos_data ;

reg [15:0] delta_phase ;

always @(posedge clk) begin

if(rst)begin

multi <= 0;

end else begin

if(cos_dat2 > cos_dat1)begin

delta_cos_data <= (cos_dat2 - cos_dat1) ;

delta_phase <= phase_d1 - phase1_d1 ;

multi <= delta_cos_data*delta_phase ;

end else begin

delta_cos_data <= (cos_dat1 - cos_dat2) ;

delta_phase <= phase_d1 - phase1_d1 ;

multi <= delta_cos_data*delta_phase ;

end

end

end

reg signed [15:0] cos_dat1_d;

reg signed [15:0] cos_dat2_d;

always @(posedge clk) begin

if(rst)begin

cos_dat1_d <= 0;

cos_dat2_d <= 0;

end else begin

cos_dat1_d <= cos_dat1;

cos_dat2_d <= cos_dat2;

end

end

reg signed [15:0] cos_dat1_d1;

reg signed [15:0] cos_dat2_d1;

always @(posedge clk) begin

if(rst)begin

cos_dat1_d1 <= 0;

cos_dat2_d1 <= 0;

end else begin

cos_dat1_d1 <= cos_dat1_d;

cos_dat2_d1 <= cos_dat2_d;

end

end

always @(posedge clk) begin

if(rst)begin

cos_out <= 0;

end else begin

if(cos_dat2_d1 > cos_dat1_d1)begin

cos_out <= cos_dat1_d1 + (multi >> 8);

end else begin

cos_out <= cos_dat1_d1 - (multi >> 8);

end

end

end

endmodule

仿真代码:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2025/04/05 00:00:38

// Design Name:

// Module Name: tb_cos_gen_pipeline

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module tb_cos_gen_pipeline();

reg clk;

reg rst;

initial begin

clk <=0;

rst <=1;

#300

rst <=0;

end

always #10 clk <= ~clk;

reg valid ;

reg [15:0] phase ;

localparam FREQ_FTW = 6554; // 频率控制字 生成5Mhz的正弦波,采样率50M,round((5/50)*(2^16))

always @(posedge clk)begin

if(rst)begin

valid <= 0;

phase <= 0;

end

else begin

valid <= 1;

phase <= phase + FREQ_FTW;

end

end

wire rdy ;

wire [15:0] cos_out ;

cos_gen_pipeline cos_gen_pipeline(

.clk (clk ),

.rst (rst ),

.valid (valid ), //使能信号

.phase (phase ), //相位,0~65535对应[0~2pi)

.rdy (rdy ), //输出准备好信号

.cos_out (cos_out)

);

integer file = 0;

initial begin

file = $fopen("cos_gen_pipeline.txt", "w");

if (file == 0) begin

$display("Error opening file");

$finish;

end

end

reg [15:0] data_cnt = 0;

always @(posedge clk)begin

if(rdy)begin

data_cnt <= data_cnt + 1;

$fwrite(file, "%d\n", $signed(cos_out));

if(data_cnt == 4096*4-1)begin

$fclose(file);

$finish;

end

end

end

endmodule

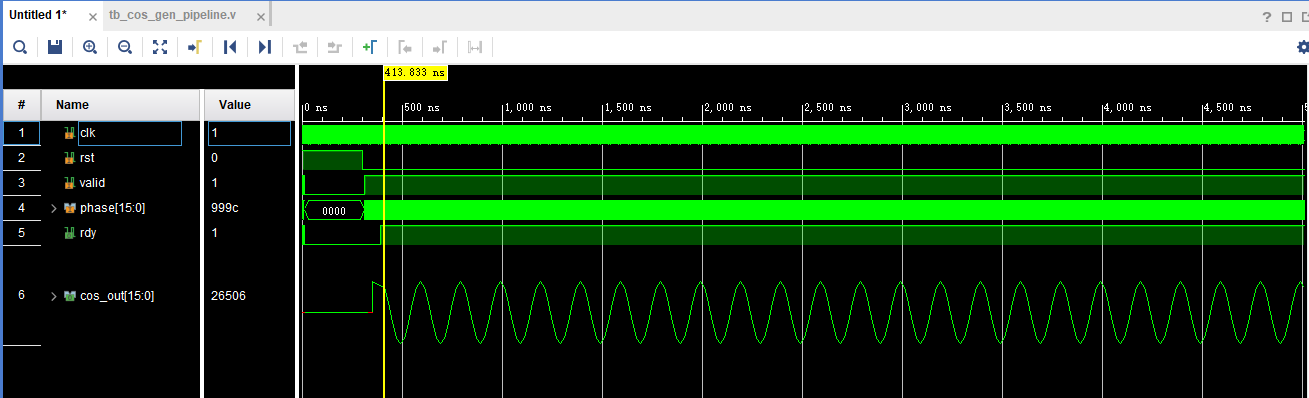

仿真结果:

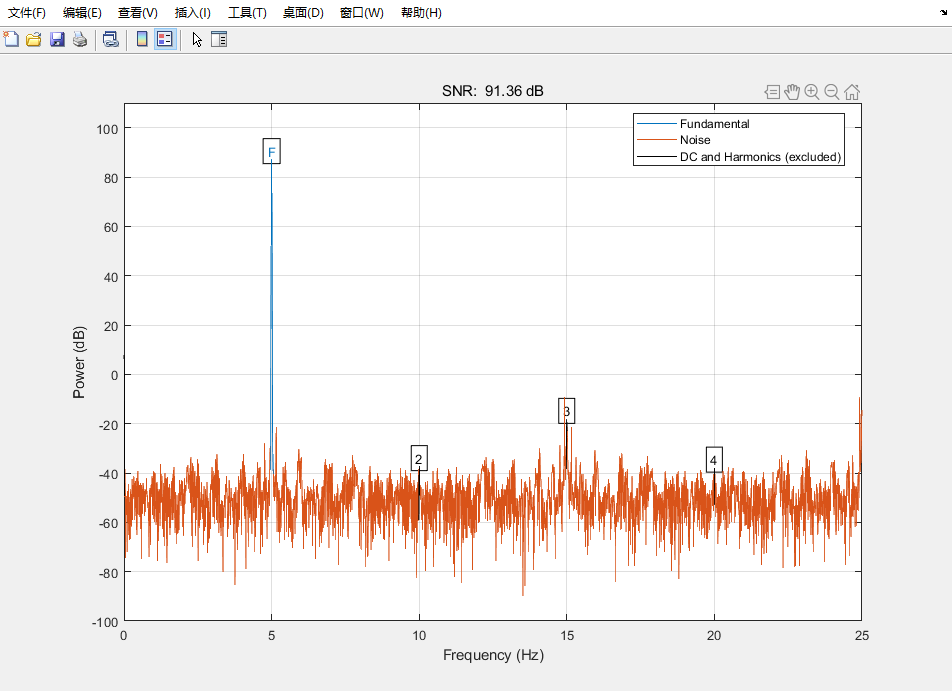

这样一个正弦波生成器就完成了,SNR=91db,足以满足大多数的使用情况了,如果需要更高的精度,可以更改样本的点数,为了提升频率精度,需要对相位控制字位宽进行扩展。

verilog利用线性插值实现正弦波生成器(dds)的更多相关文章

- mysql利用LAST_INSERT_ID实现id生成器

首先了解 LAST_INSERT_ID LAST_INSERT_ID 有自己的存储空间,能存一个数字 不带参数时返回最近insert的那行记录的自增字段值.带参数时会将自己存储的数字刷成参数给定的值 ...

- [FPGA]Verilog利用PWM调制巧妙完成RGB三色彩虹呼吸灯(给简约的题目以美妙的解答)

概述 实现彩虹呼吸灯 题目就是这么简短,但这是目前我碰到的最有意思的一道题目,因为他有无数种解决方法,并且每一种都是那么高级或者巧妙,比如 可以利用3路不同初相的PWM调制信号驱动三颗RGB灯重叠呼吸 ...

- Verilog利用$fdisplay命令往文件中写入数据

最近在做的事情是,用FPGA生成一些满足特定分布的序列.因此为了验证我生成的序列是否拥有预期的性质,我需要将生成的数据提取出来并且放到MATLAB中做数据分析. 但是网上的程序很乱,表示看不懂==其实 ...

- 基于FPGA的DDS设计(一)

最近在学习基于FPGA的DDS设计,借此机会把学习过程记录下来,当作自己的学习笔记也希望能够帮助到学习DDS的小伙伴. DDS(Direct Digital Synthesizer)直接数字合成器,这 ...

- Python小白学习之路(二十三)—【生成器补充】

生成器的一些补充 接着下鸡蛋和吃包子! 补充一:生成器只能遍历一次 (总是把生成器比喻成母鸡下鸡蛋,需要一个下一个,首先是下出来的鸡蛋不能塞回母鸡肚子里,其次是一个母鸡一生只能下一定数量的鸡蛋,下完了 ...

- python里的生成器

author:headsen chen date:2018-03-22 10:59:46 notice:This article created by headsen chen himself and ...

- FFMpeg ver 20160219-git-98a0053 滤镜中英文对照 2016.02.21 by 1CM

FFMpeg ver 20160219-git-98a0053 滤镜中英文对照 2016.02.21 by 1CM T.. = Timeline support 支持时间轴 .S. = Slice t ...

- FFMpeg ver 20160213-git-588e2e3 滤镜中英文对照

1 FFMpeg ver 20160213-git-588e2e3 滤镜中英文对照 2016.02.18 by 1CM 2 T.. = Timeline support 3 支持时间轴 4 .S. = ...

- FFMpeg 滤镜中英文对照

FFMpeg ver 20160213-git-588e2e3 滤镜中英文对照 2016.02.17 by 1CM T.. = Timeline support 支持时间轴 .S. = Slice t ...

- shell脚本生成限定范围的随机数

#!/bin/bash +)) 这串代码实现了随机生成从1~50之间是数 这串代码特别简单,就是利用RANDOM这个随机数生成器进行取余就能够实现,至于为什么取余时需要+1是因为在取余时如果被整除那么 ...

随机推荐

- WPF 设置DataGrid 选中的背景色和前景色

<DataGrid > <DataGrid.CellStyle> <Style TargetType="DataGridCell"> <S ...

- hadoop-hbase单机和集群搭建

1.下载 http://www.apache.org/dyn/closer.cgi/hadoop/common/hadoop-2.7.1/hadoop-2.7.1.tar.gz 最新版 解压: t ...

- TbSchedule任务调度管理框架的整合部署

一.前言 任务调度管理作为基础架构通常会出现于我们的业务系统中,目的是让各种任务能够按计划有序执行.比如定时给用户发送邮件.将数据表中的数据同步到另一个数据表都是一个任务,这些相对耗时的操作通过任务调 ...

- 推荐一款非常好用的在线 SSH 管理工具

前言 SSH工具在远程连接.文件传输.远程管理和增强安全性等方面发挥着重要作用,是我们开发人员和系统管理员不可或缺的工具.今天大姚给大家推荐一款非常好用的在线 SSH 管理工具:Xterminal. ...

- 变量-python

变量-python 1. 变量的定义 变量是存储数据的地方,在程序运行时,变量的值可以改变.变量的定义格式如下: 变量名 = 数据 例如: a = 10 b = "hello" c ...

- 某次信创环境Oceanbase数据库偶发乱码问题

资料迁移,整理分享. 问题发生在2023年 一.环境介绍及问题简述 数据库 oceanbase 操作系统 Linux (麒麟) WEB中间件 Tongweb 数据库表编码 GBK 中间件默认使用的HT ...

- RabbitMq消息过期时间TTL介绍

概述: 在rabbitmq中我们可以给消息设定过期时间LLT(Time to Live),在消息发送后过期时间段内未被消费,则系统会将其删除,被删除的消息将会进入死信队列.关于设置消息的过期时间有两种 ...

- FreeSql学习笔记——3.查询

前言 FreeSql中查询的支持非常丰富,包括链式语法,多表查询,表达式函数:写法多种多样,可以使用简单的条件查询.sql查询.联表.子表等方式用于查询数据, 查询的格式也有很丰富,包括单条记录, ...

- redis的连接池和管道

NoSQL泛指非关系型的数据库 非关系型数据库和关系型数据库的差别: 性能NOSQL是基于键值对的,可以想象成表中的主键和值的对应关系,而且不需要经过SQL层的解析,所以性能非常高 可扩展性同样也 ...

- 在 WPF 应用程序中缓存应用程序数据

参考学习链接:https://docs.microsoft.com/zh-cn/dotnet/framework/wpf/advanced/walkthrough-caching-applicatio ...