Cacheable VS Non-Cacheable

1 基本概念

在嵌入式软件开发中,经常会碰到说某块内存是cache的,还是non-cache的,它们究竟是什么意思?分别用在什么场景?non-cache和cache的内存区域怎么配置?这篇博文将会围绕这几个问题展开讨论。

Cache,就是一种缓存机制,它位于CPU和DDR之间,为CPU和DDR之间的读写提供一段内存缓冲区。cache一般是SRAM,它采用了和制作CPU相同的半导体工艺,它的价格比DDR要高,但读写速度要比DDR快不少。例如CPU要执行DDR里的指令,可以一次性的读一块区域的指令到cache里,下次就可以直接从cache里获取指令,而不用反复的去访问速度较慢的DDR。又例如,CPU要写一块数据到DDR里,它可以将数据快速地写到cache里,然后手动执行一条刷新cache的指令就可以将这片数据都更新到DDR里,或者干脆就不刷新,待cache到合适的时候,自己再将内容flush到DDR里。总之一句话,cache的存在意义就是拉近CPU和DDR直接的性能差异,提高整个系统性能。

2 哪些情况不能用cache

在大部分时候,cache是个很好的帮手,我们需要它。但也有例外,考虑下面几个场景

- case 1 CPU读取外设的内存数据,如果外设的数据本身会变,如网卡接收到外部数据,那么CPU如果连续2次读外设的操作相差时间很短,而且访问的是同样的地址,上次的内存数据还存在于cache当中,那么CPU第二次读取的可能还是第一次缓存在cache里数据。

- case 2 CPU往外设写数据,如向串口控制器的内存空间写数据,如果CPU第1次写的数据还存在于cache当中,第2次又往同样的地址写数据,CPU可能就只更新了一下cache,由cache输出到串口的只有第2次的内容,第1次写的数据就丢失了。

- case 3 在嵌入式开发环境中,经常需要在PC端使用调试工具来通过直接查看内存的方式以确定某些事件的发生,如果定义一个全局变量来记录中断计数或者task循环次数等,这个变量如果定义为cache的,你会发现有时候系统明明是正常运行的,但是这个全局变量很长时间都不动一下。其实它的累加效果在cache里,因为没有人引用该变量,而长时间不会flush到DDR里

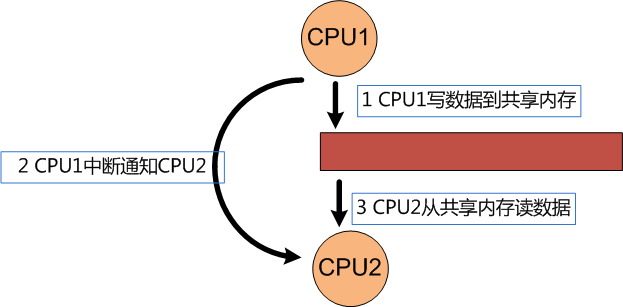

- case 4 考虑双cpu的运行环境(不是双核)。cpu1和cpu2共享一块ddr,它们都能访问,这块共享内存用于处理器之间的通信。cpu1在写完数据到后立刻给cpu2一个中断信号,通知cpu2去读这块内存,如果用cache的方法,cpu1可能把更新的内容只写到cache里,还没有被换出到ddr里,cpu2就已经跑去读,那么读到的并不是期望的数据。该过程如图所示:

另外,做过较为小型的对性能要求不太高的嵌入式裸板程序(例如bootloader,板级外设功能验证之类)的朋友都知道,cache经常会帮倒忙,所以他们往往会直接把CPU的cache功能关掉,损失一点性能以确保CPU写入和读出的数据与操作的外设完全一致。

这里我们可以稍微总结一下:对于单CPU,不操作外设,只对DDR的读写,可以放心的使用cache。对于其它情况,有两种办法:

- 1 手动更新cache,这需要对外设的机制较为了解,且要找到合适的时机刷新(将cache里的数据flush到内存里)或无效(Invalidate,将cache里的内容清掉,下次再读取的时候需要去DDR里读最新的内容)

- 2 将内存设置为non-cache的,更准确的说是non-cacheable的

3 怎么设置内存为non-cacheable?

不同的处理器平台对于non-cacheable的处理办法也是不一样的,在高级CPU里,一般在运行中,动态地采用页表的方式来标记某些内存是否是non-cacheable的,例如Linux内核里的 有个常用的函数叫ioremap,在访问外设的时候经常会用到,它的作用是映射外设的物理地址到虚拟地址空间给内核驱动程序使用,在映射时,会将寄存器地址页表配置为non-cacheable的,数据直接从外设的地址空间读写,保持了数据的一致性。

在较为低级的CPU(如ARM Cortex-A5,MIPS R3000.接近于MCU)里,一般是采用编译链接时预设的方法来区分cache区域和non-cache区域,在链接脚本或者scatter file里定义不同的section,将需要设为non-cacheable的内存块放置到特定的section里。CPU在启动时会读取这些配置文件,在启动代码里对不同的section配置MMU或MPU,对non-cache的section映射到CPU认识的特拟地址。此后,CPU再访问内存的时候,经过MMU或者MPU,就会知道这块内存是cacheable还是non-cacheable的了

在MIPS里,程序地址空间被分为了kseg0,kseg1等区域,其中kseg0是0x800000000x9FFFFFFF,它是非映射的、cached;kesg1是0xA00000000xBFFFFFFF,它是非映射的,uncached,他们指向的物理地址空间是相同的,也就是说,0x82001234和0xA2001234指向的物理地址是相同的,但是MIPS对它们的访问方式不同,当取指后CPU得知要访问的是kseg0的空间,会想去cache寻找目标内存,若找不到,才会去物理地址寻找,而如果要访问的地址空间是kseg1内,则CPU会绕过cache,直接去物理地址里进行读和写。

4 non-cacheable区域的大小有限制吗?

答案是否定的,只要你乐意,甚至可以把几乎整个DDR都设置为non-cacheable的,但是这样做付出的代价也是巨大的,你等于放弃了CPU厂家精心设计的cache机制,在每次读写数据都要去访问比CPU速度慢得多的DDR,整个系统速度会被严重拖慢。楼主做过一个测试,在同等条件下,写cache的内存速度大约比non-cache的内存快一倍的!

5 应用案例

假设某个嵌入式应用需要将一个4K的内存拷贝到另一个地址去,源和目的映射的物理地址都在DDR里。很自然的,我们会想到勤劳的搬运工——DMA,让DMA去做这个枯燥而费时的拷贝工作,让CPU忙别的去。经常使用DMA的同学都知道,它有标准的3个步骤:

- 对源地址进行cache flush,防止源地址里的内容已经在cache里更新,而DDR里还是过时的内容,DMA可不知道何为Cache

- 对目标地址进行cache invalidate,因为这个目标地址里的内容马上就要被覆盖了,cache里如果有它的内容,就是过时的了

- 设置源、目的地址和数据长度,启动DMA

是不是挺麻烦的? 如果源地址和目的地址都是以全局数据的形势预设置好的话,完全可以将它们定义在non-cacheable的段内,这样第1)步和第2)步就都不再需要了。请注意,源和目的地址都需要定义到non-cache的区域,少一个的话,你都很可能得不到正确的结果,因为cache的强随机性,DMA搬完后,你再访问内存里的内容很可能是个很奇怪的数字。

6 cache flush & cache invalidate

含义:Flush does write back the contents of cache to main memory, and invalidate does mark cache lines as invalid so that future reads go to main memory.

invalidate处理悖论:如果需要invalidate的cache/cache line里面包含无用的数据,需要丢弃;又包含其他进程需要的有用的数据,需要写回内存。

Cacheable VS Non-Cacheable的更多相关文章

- Spring缓存注解@Cacheable

@Cacheable @Cacheable 的作用 主要针对方法配置,能够根据方法的请求参数对其结果进行缓存 @Cacheable 作用和配置方法 参数 解释 example value 缓存的名称, ...

- Spring-Cache 注解 @Cacheable,@CachePut , @CacheEvict

1.自动生成key @Bean public KeyGenerator keyGenerator() { return new KeyGenerator() { @Override public Ob ...

- 详解Spring缓存注解@Cacheable,@CachePut , @CacheEvict使用

https://blog.csdn.net/u012240455/article/details/80844361 注释介绍 @Cacheable @Cacheable 的作用 主要针对方法配置,能够 ...

- Spring Boot缓存注解@Cacheable、@CacheEvict、@CachePut使用

从3.1开始,Spring引入了对Cache的支持.其使用方法和原理都类似于Spring对事务管理的支持.Spring Cache是作用在方法上的,其核心思想是这样的:当我们在调用一个缓存方法时会把该 ...

- SpringBoot2.0 @Cacheable 添加超时策略

SpringBoot2.0 @Cacheable 添加超时策略 逻辑比较简单,废话不多说,直接进入正题: 需求:SpringBoot 利用注解使缓存支持过期时间 (同@Cacheable @Cache ...

- Cacheable key collision with DefaultKeyGenerator

The default is to use the hashcode of each parameter and create another (32-bit) hash code. Obviousl ...

- Spring中@Cacheable的用法

在Spring中通过获取MemCachedClient来实现与memcached服务器进行数据读取的方式.不过,在实际开发中,我们往往是通过Spring的@Cacheable来实现数据的缓存的,所以, ...

- Spring 4 Ehcache Configuration Example with @Cacheable Annotation

http://www.concretepage.com/spring-4/spring-4-ehcache-configuration-example-with-cacheable-annotatio ...

- mybatis存取blob对象+@Cacheable实现数据缓存

参考文档: http://www.ibm.com/developerworks/cn/opensource/os-cn-spring-cache/ 需求场景: 当前业务通过第三方接口查询一个业务数据, ...

- Spring的Bean内部方法调用无法使用AOP切面(CacheAble注解失效)

Spring的Bean内部方法调用无法使用AOP切面(CacheAble注解失效) 前言 今天在使用Spring cache的Cacheable注解的过程中遇见了一个Cacheable注解失效的问题, ...

随机推荐

- docker-compose总结

docker-compose.yml 样例: 各个标签的含义在注释里 version: '3' # 选择的docker-compose 版本 services: # 要编排的一组服务 fim-mysq ...

- 一个注解解决ShardingJdbc不支持复杂SQL

背景介绍 公司最近做分库分表业务,接入了 Sharding JDBC,接入完成后,回归测试时发现好几个 SQL 执行报错,关键这几个表都还不是分片表.报错如下: 这下糟了嘛.熟悉 Sharding J ...

- LFS(Linux From Scratch)构建过程全记录(三):下载所需的软件包

写在前面 本文将记录构建LFS的过程中,下载软件包的全过程 准备下载的路径 注意请确保$LFS已经设置完毕 我们需要创建一个文件夹,地址为$LFS/sources,用于保存对应的源码 输入的指令如下: ...

- kvm使用桥接的方法

什么是桥接 桥接就是把物理机的网卡模拟成交换机,虚拟机的网卡直接连在虚拟的网桥即交换机上.这样kvm虚拟机分配的IP地址,就应该和物理机在同一网段,可以对外进行服务. 在KVM下运行的VM默认的网卡采 ...

- Vue实现拖拽穿梭框功能四种方式

一.使用原生js实现拖拽 点击打开视频讲解更加详细 <html lang="en"> <head> <meta charset="UTF-8 ...

- SpringBoot 项目部署(初级)

之前的项目一直在本地电脑上写,最近需要将项目部署到服务器上进行联调测速度.于是,在网上搜集资料后简单的进行一下总结. 由于本次打包部署是为了测试,于是很多内容做的还不算详尽,只是将项目简单的打包为ja ...

- 用深度强化学习玩FlappyBird

摘要:学习玩游戏一直是当今AI研究的热门话题之一.使用博弈论/搜索算法来解决这些问题需要特别地进行周密的特性定义,使得其扩展性不强.使用深度学习算法训练的卷积神经网络模型(CNN)自提出以来在图像处理 ...

- sg函数入门理解

首先理解sg函数必须先理解mex函数 mex是求除它集合内的最小大于等于0的整数,例:mex{1,2}=0:mex{2}=0:mex{0,1,2}=3:mex{0,5}=1. 而sg函数是啥呢? 对于 ...

- TDengine的数据建模?库、表、超级表是什么?怎么用?

欢迎来到物联网的数据世界 在典型的物联网场景中,一般有多种不同类型的采集设备,采集多种不同的物理量,同一种采集设备类型,往往有多个设备分布在不同的地点,系统需对各种采集的数据汇总,进行计算和分析对于 ...

- Vue中使用Switch开关用来控制商品的上架与下架情况、同时根据数据库商品的状态反应到前台、前台修改商品状态保存到数据库

一般后台对商品的信息管理.包含商品的上架与下架.为了提高用户的体验.将商品上下架的操作做成开关的形式.同时后台数据库中保存的商品状态能够根据开关状态改变. 1.效果展示 这种效果:== 当开关是开启状 ...