基于Verilog的串口接收程序

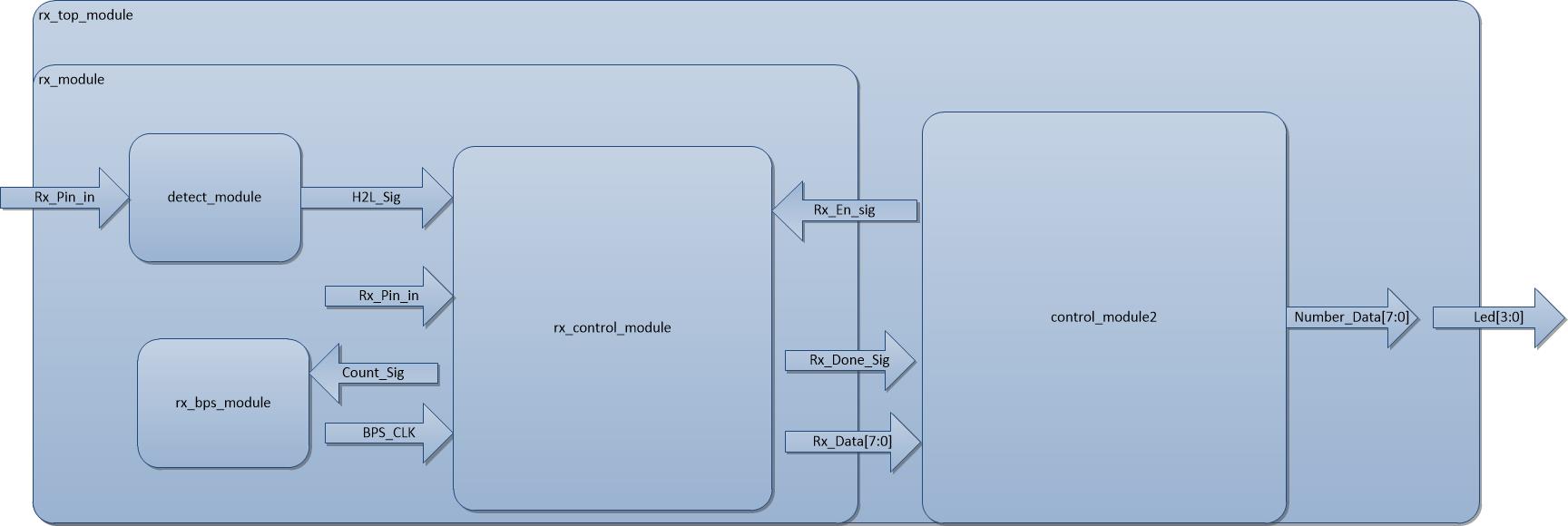

一、模块框图及基本思路

detect_module:检测输入引脚的下降沿,以此判断一帧数据的开始

rx_bps_module:波特率时钟产生模块

rx_control_module:串口接收的核心控制模块

rx_module:前三个模块的组合

control_module2:接受控制模块,不断接收串口数据

rx_top_module:将接收到数据的第四位以LED的形式显示

二、软件部分

detect_module:

module detect_module(

CLK,RSTn,

RX_Pin_in,

H2L_Sig

);

input CLK,RSTn;

input RX_Pin_in;

output H2L_Sig; /**********************************/

reg RX_r1;

reg RX_r2; always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

RX_r1<='b1;

RX_r2<='b1;

end

else

begin

RX_r1<=RX_Pin_in;

RX_r2<=RX_r1;

end

end

/*********************************/ assign H2L_Sig=RX_r2&(!RX_r1); endmodule

rx_bps_module:

module rx_bps_module #(parameter Baud=)(

CLK,RSTn,

Count_Sig,

BPS_CLK

);

input CLK;

input RSTn;

input Count_Sig;

output BPS_CLK; /***************************/

localparam Baud_Div=50_000_000/Baud-;

localparam Baud_Div2=Baud_Div/; reg[:] Count_BPS;

/*************************/

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

Count_BPS<='d0;

else if(Count_BPS==Baud_Div)

Count_BPS<='d0;

else if(Count_Sig)

Count_BPS<=Count_BPS+;

else Count_BPS<='d0;

end

/************************/

assign BPS_CLK=(Count_BPS==Baud_Div2)?'b1:1'b0;

endmodule

rx_control_module:

module rx_control_module(

CLK,RSTn,

H2L_Sig,BPS_CLK,RX_Pin_in,

Count_Sig,RX_En_Sig,RX_Done_Sig,RX_Data

); input CLK,RSTn;

input H2L_Sig,BPS_CLK,RX_En_Sig,RX_Pin_in;

output Count_Sig,RX_Done_Sig;

output [:] RX_Data; reg[:] i;

reg isCount;

reg isDone;

reg [:] rData;

/********************************************/

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

i<='d0;

isCount<='b0;

isDone<='b0;

rData<='d0;

end

else if(RX_En_Sig)

begin

case(i)

'd0:if(H2L_Sig) begin i<=i+1'b1;isCount<='b1; end //接收到下降沿开始启动波特率计数

'd1:if(BPS_CLK) begin i<=i+1'b1; end //起始位

'd2,4'd3,'d4,4'd5,'d6,4'd7,'d8,4'd9:

if(BPS_CLK) begin rData[i-]<=RX_Pin_in;i<=i+'b1;end //数据位

'd10:if(BPS_CLK) begin i<=i+1'b1; end //校验位

'd11:if(BPS_CLK) begin i<=i+1'b1; end //停止位

'd12:if(BPS_CLK) begin i<=i+1'b1;isDone<='b1;isCount<=1'b0; end //一个时钟脉冲的 isDone 信号

'd13:begin i<=1'b0;isDone<='b0; end

endcase

end end /********************************************/

assign Count_Sig=isCount;

assign RX_Done_Sig=isDone;

assign RX_Data=rData; endmodule

rx_module:

module rx_module(

CLK,RSTn,

RX_Pin_in,RX_Done_Sig,RX_Data,RX_En_Sig

); input CLK,RSTn;

input RX_Pin_in,RX_En_Sig;

output RX_Done_Sig;

output [:] RX_Data; wire Count_Sig;

wire BPS_CLK;

wire H2L_Sig; rx_bps_module U0(

.CLK(CLK),.RSTn(RSTn),

.Count_Sig(Count_Sig),

.BPS_CLK(BPS_CLK)

); detect_module U1(

.CLK(CLK),.RSTn(RSTn),

.RX_Pin_in(RX_Pin_in),

.H2L_Sig(H2L_Sig)

); rx_control_module U2(

.CLK(CLK),.RSTn(RSTn),

.H2L_Sig(H2L_Sig),.BPS_CLK(BPS_CLK),.RX_Pin_in(RX_Pin_in),

.Count_Sig(Count_Sig),.RX_En_Sig(RX_En_Sig),.RX_Done_Sig(RX_Done_Sig),.RX_Data(RX_Data)

); endmodule

control_module2:

module control_module2(

CLK,RSTn,

RX_Done_Sig,

RX_En_Sig,

RX_Data,

Number_Data

); input CLK;

input RSTn;

input RX_Done_Sig;

input [:]RX_Data;

output RX_En_Sig;

output [:] Number_Data; /***************************************/

reg[:] rData;

reg rEn;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

rData<='d0;

rEn<='b0;

end

else if(RX_Done_Sig)

begin

rEn<='b0;

rData<=RX_Data;

end

else rEn<='b1;

end

/***************************************/

assign Number_Data=rData;

assign RX_En_Sig=rEn; endmodule

rx_top_module:

module rx_top_module(

CLK,RSTn,

RX_Pin_in,Led

);

input CLK,RSTn;

input RX_Pin_in;

output [:]Led; wire RX_Done_Sig;

wire RX_En_Sig;

wire [:] Number_Data;

wire [:] RX_Data; rx_module U0(

.CLK(CLK),.RSTn(RSTn),

.RX_Pin_in(RX_Pin_in),.RX_Done_Sig(RX_Done_Sig),.RX_Data(RX_Data),.RX_En_Sig(RX_En_Sig)

); control_module2 U1(

.CLK(CLK),.RSTn(RSTn),

.RX_Done_Sig(RX_Done_Sig),

.RX_En_Sig(RX_En_Sig),

.RX_Data(RX_Data),

.Number_Data(Number_Data)

); assign Led=Number_Data[:];

endmodule

三、硬件部分

黑金SPARTAN-6开发板

NET "CLK" LOC = T8;

NET "RSTn" LOC = L3;

NET "RX_Pin_in" LOC = C11;

NET "Led[0]" LOC = P4;

NET "Led[1]" LOC = N5;

NET "Led[2]" LOC = P5;

NET "Led[3]" LOC = M6;

基于Verilog的串口接收程序的更多相关文章

- 基于Verilog的串口发送程序

一.模块框图及基本思路 tx_bps_module:波特率时钟产生模块 tx_control_module:串口发送的核心控制模块 tx_module:前两个模块的组合 control_module: ...

- 基于Verilog的带FIFO输出缓冲的串口接收接口封装

一.模块框图及基本思路 rx_module:串口接收的核心模块,详细介绍请见“基于Verilog的串口接收实验” rx2fifo_module:rx_module与rx_fifo之间的控制模块,其功能 ...

- 基于Verilog的带FIFO写入缓冲的串口发送接口封装

一.模块框图及基本思路 tx_module:串口发送的核心模块,详细介绍请参照前面的“基于Verilog的串口发送实验” fifo2tx_module:当fifo不为空时,读取fifo中的数据并使能发 ...

- Qt编写串口通信程序全程图文解说

(说明:我们的编程环境是windows xp下,在Qt Creator中进行,假设在Linux下或直接用源代码编写,程序稍有不同,请自己修改.) 在Qt中并没有特定的串口控制类,如今大部分人使用的是第 ...

- 转:Qt编写串口通信程序全程图文讲解

转载:http://blog.csdn.net/yafeilinux/article/details/4717706 作者:yafeilinux (说明:我们的编程环境是windows xp下,在Q ...

- Qt编写串口通信程序全程图文讲解 .

在Qt中并没有特定的串口控制类,现在大部分人使用的是第三方写的qextserialport类,我们这里也是使用的该类.我们可以去 http://sourceforge.net/projects/qex ...

- 【转】Qt编写串口通信程序全程图文讲解

本文章原创于www.yafeilinux.com 转载请注明出处. (说明:我们的编程环境是windows xp下,在Qt Creator中进行,如果在Linux下或直接用源码编写,程序稍有不同,请自 ...

- C#中缓存的使用 ajax请求基于restFul的WebApi(post、get、delete、put) 让 .NET 更方便的导入导出 Excel .net core api +swagger(一个简单的入门demo 使用codefirst+mysql) C# 位运算详解 c# 交错数组 c# 数组协变 C# 添加Excel表单控件(Form Controls) C#串口通信程序

C#中缓存的使用 缓存的概念及优缺点在这里就不多做介绍,主要介绍一下使用的方法. 1.在ASP.NET中页面缓存的使用方法简单,只需要在aspx页的顶部加上一句声明即可: <%@ Outp ...

- 018_STM32程序移植之_串口接收中文

(一)在平时数据传输中很少用到接收中文的情况,但是最近需要用到就花了半天时间来弄弄 (二)接收原理,从现在接收情况分析:一个中文占两个数据的空间,也就是两个十六进制可以转化成为一个中文 (三)示例情况 ...

随机推荐

- AI 基础

what AI ? 人工智能(Artificial Intelligence),英文缩写为AI. 人工智能是计算机科学的一个分支,它企图了解智能的实质,并生产出一种新的能以人类智能相似的方式做出反应的 ...

- sparkStreaming 与fafka直接方式 进行消费者偏移量的保存如redis 里面 避免代码改变与节点重启后的数据丢失与序列化问题

import java.util import kafka.common.TopicAndPartition import kafka.message.MessageAndMetadata impor ...

- Linux 基础内容

1.linux版本有:redhat(收费),centos,ubuntu,suse(开发使用) 2./目录下的:etc配置文件目录,media挂载点,opt第三方安装目录,boot启动文件,home家, ...

- activiti5/6 系列之--Activiti与BPMN2.0规范相关节点对应关系

根据BPMN2.0规范的分类划分为以下部分: 1.启动与结束事件(event) 2.顺序流(Sequence Flow) 3.任务(Task) 4.网关(Gateway) 5.子流程(Subproce ...

- 年度游戏圈2018白皮书解析手游折扣app哪个好及靠谱程度分析

2018年,随着全国暂停游戏版本的审核和发布<综合防控儿童青少年近视实施方案>(控制新的在线游戏数量),游戏行业受到的影响不小. 在游戏产业中,游戏行业2018年的收入同比增长5.2%,远 ...

- SAP SD-销售模式-寄售(客户寄售)

SAP SD-销售模式-寄售(客户寄售) http://blog.sina.com.cn/s/blog_a440b7ee01014kgq.html http://www.doc88.com/p-23 ...

- LINQ之路12:LINQ Operators之数据转换(Projecting)

本篇继续LINQ Operators的学习,这里我们讨论的是数据转换的两种方式:Select和SelectMany,看似简单常用的两种运算符,却也大有讲究.我们会在本篇详细介绍他们的使用方式和适用的场 ...

- galera+mycat高可用集群部署

环境描述 10.30.162.29 client 环境描述 10.30.162.29 client 10.30.162.72 mysql1 10.30.162.73 mysql2 10.30.162 ...

- Qt 程序获取程序所在路径、用户目录路径、临时文件夹等特殊路径的方法

Qt 程序获取程序所在路径.用户目录路径.临时文件夹等特殊路径的方法 经常我们的程序中需要访问一些特殊的路径,比如程序所在的路径.用户目录路径.临时文件夹等.在 Qt 中实现这几个功能所用的方法虽然都 ...

- 关于ExpressionChangedAfterItHasBeenCheckedError

最近在stackoverflow上似乎每天都有一些关于angular报错‘ExpressionChangedAfterItHasBeenCheckedError’的问题.发生这些问题通常是由于angu ...