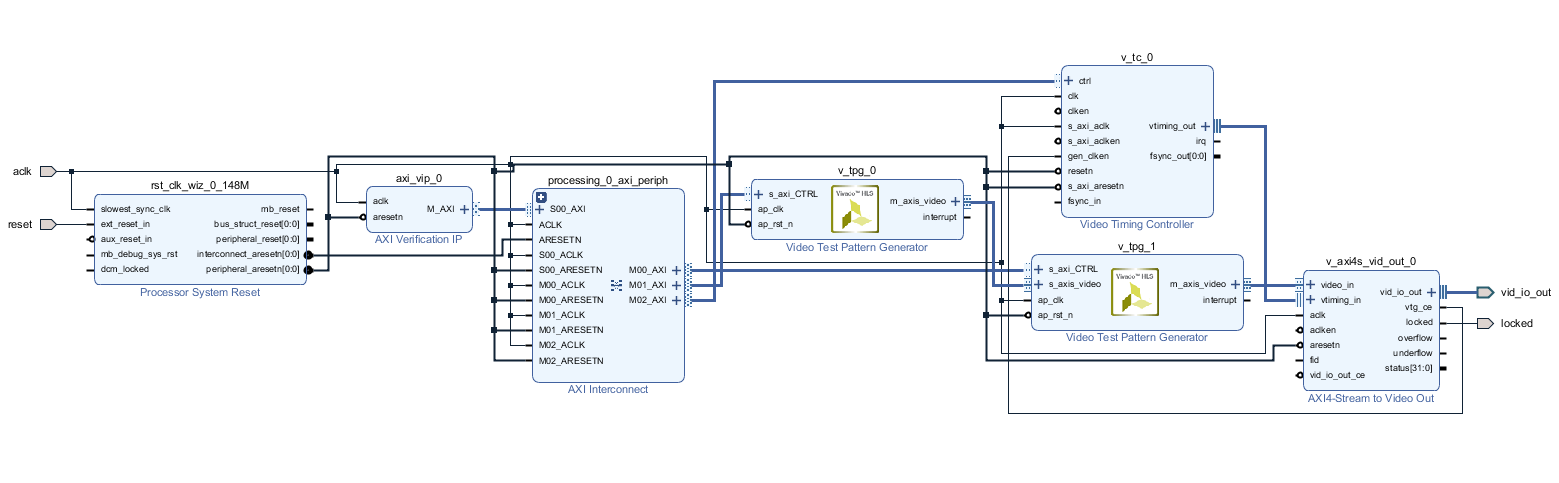

关于tpg例程的仿真

关于tpg例程的仿真

processor system reset---rst_clk_wiz_0_148M

可以看出interconnect_aresetn和peripheral_aresetn的复位作用时间不同,内部复位的时间会短好几个时钟周期。peripheral_aresetn和peripheral_rest是两个完全相反的信号。

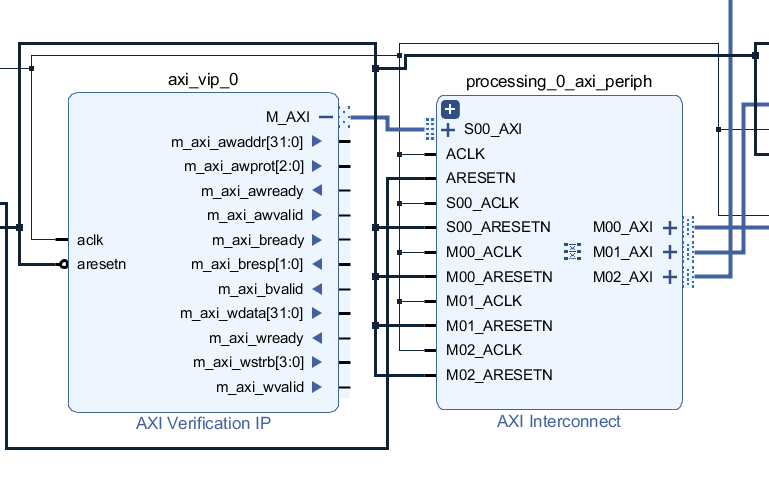

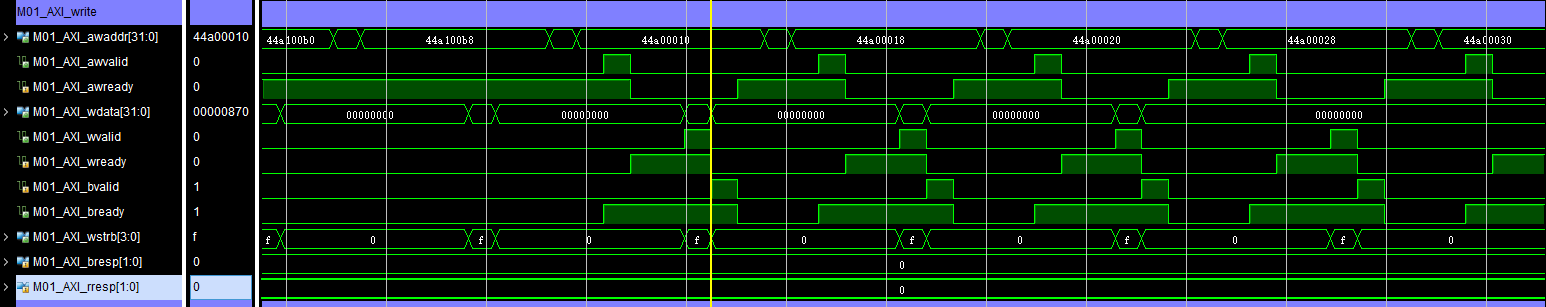

axi verification ip ---axi_vip_0

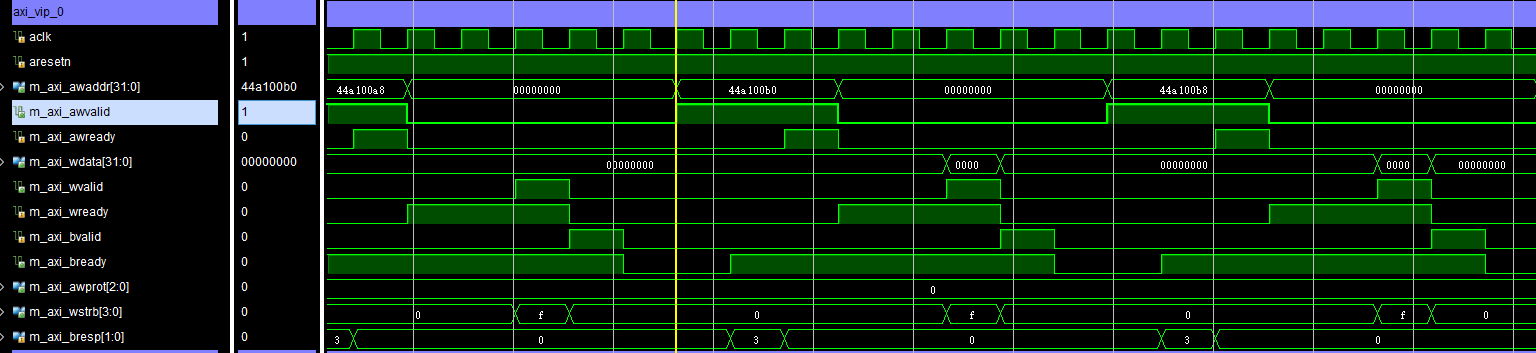

axi上的写数据,写地址,写反馈波形

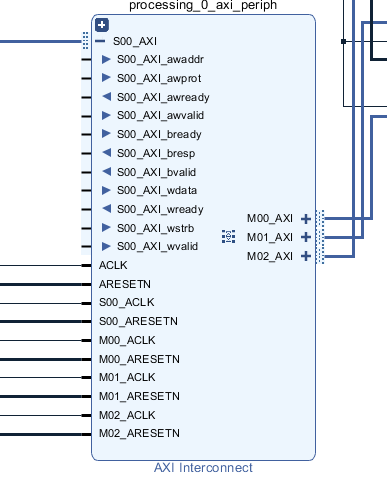

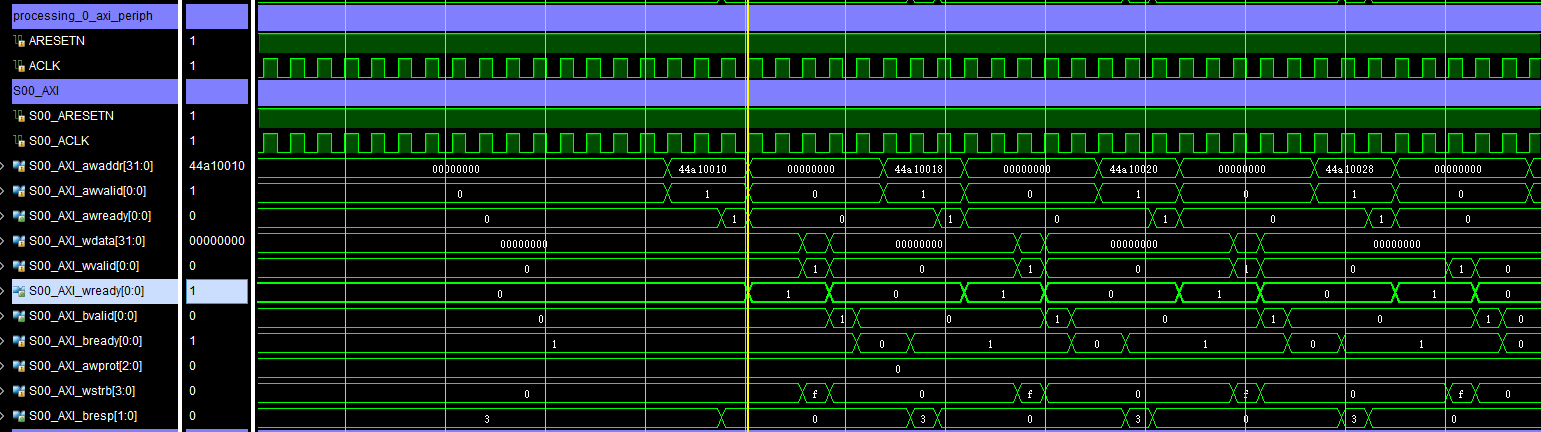

axi interconnect---processing_0_axi_preiph

S00_AXI

S00_AXI

从波形上可以判断出,S00_AXI在接收完写地址信号后,马上就产生了wready信号,为接收写数据做好准备,数据接收完成后,wready信号再拉低。

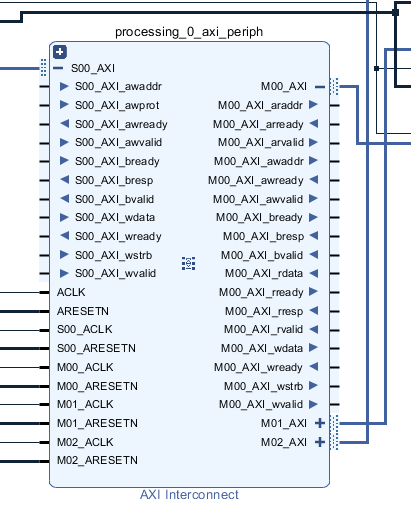

M00_AXI_read

从波形上来看,读信道基本没用

M00_AXI_write

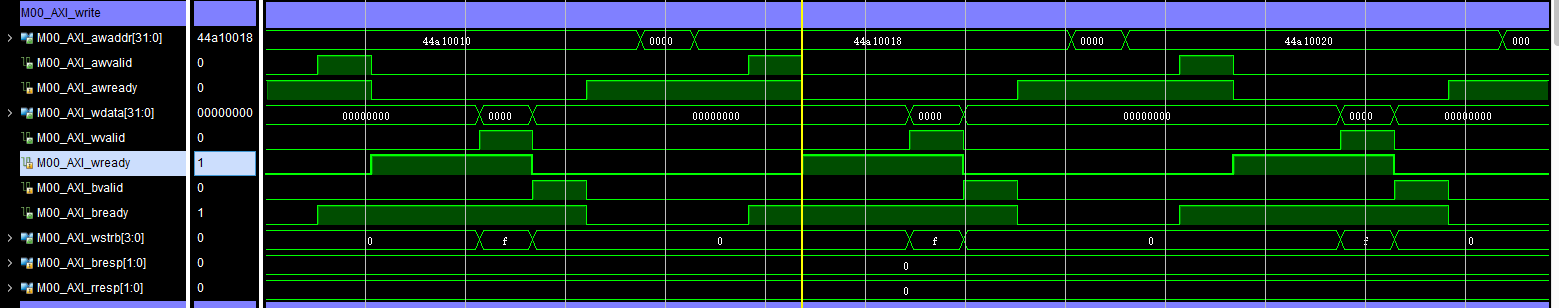

M01_AXI_read

M01_AXI_write

M01_AXI连接的是tpg_0的控制端口。

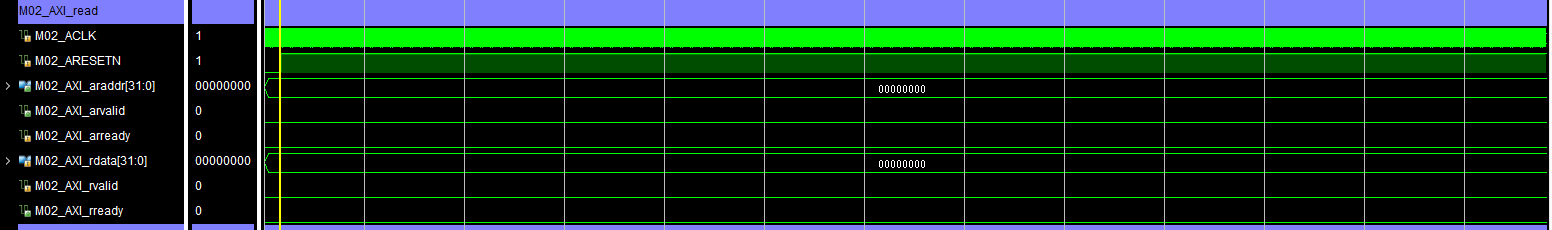

M02_AXI_read

M02_AXI连接的是VTC的控制信号

M02_AXI_write

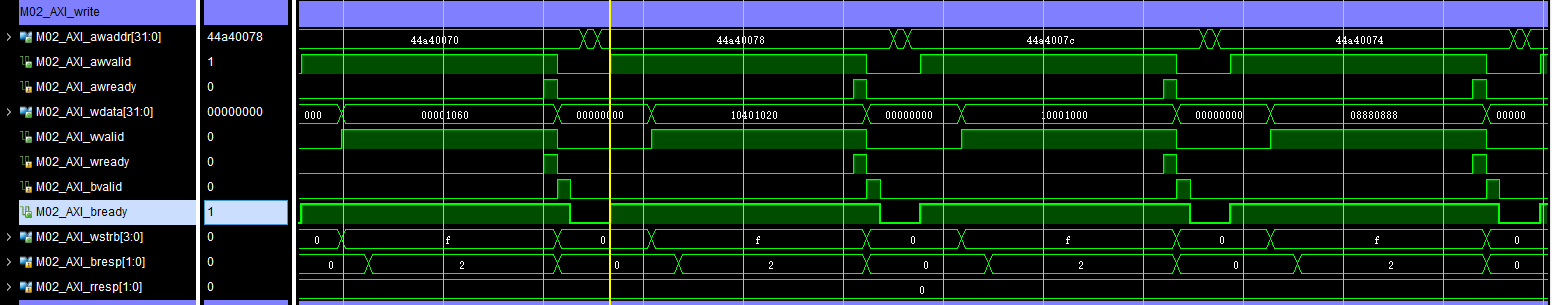

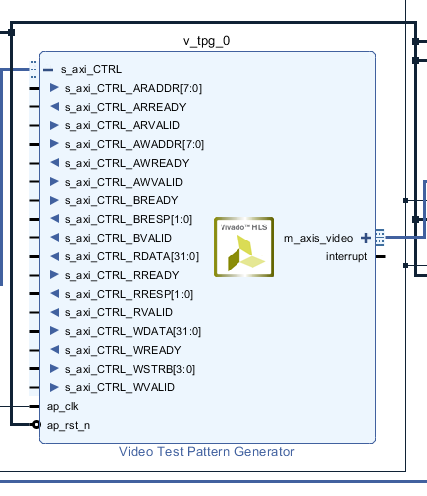

video test pattern generator---tpg_0

s_axi接口信号

接收控制指令

m_axi接口信号

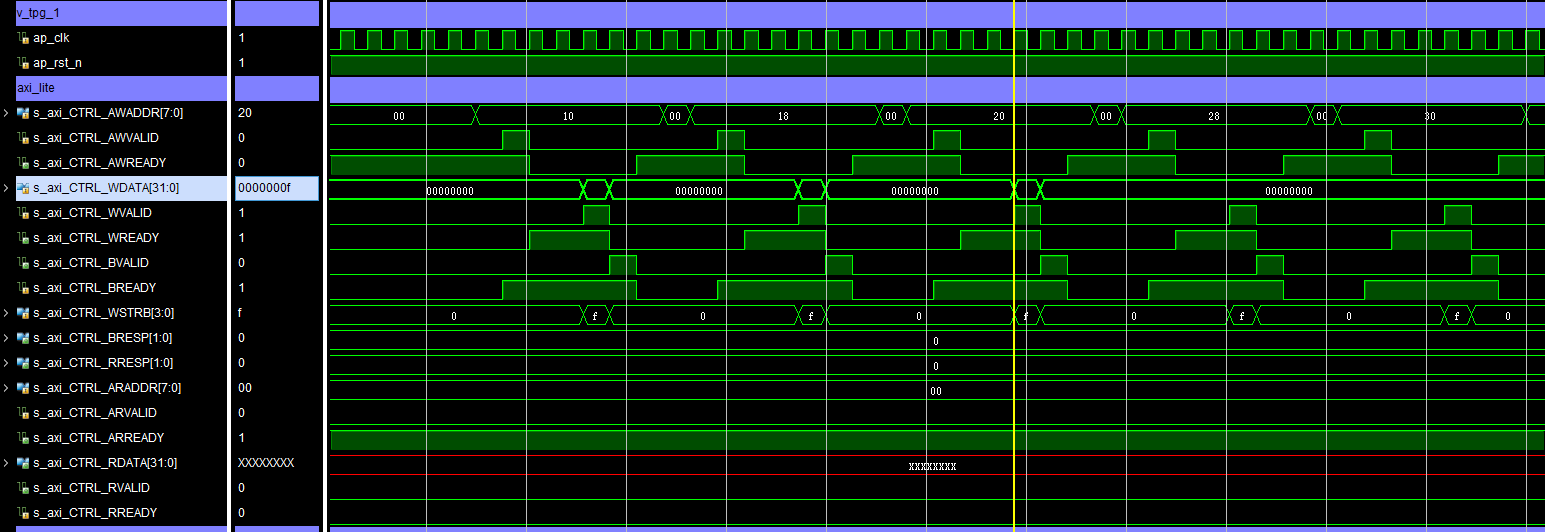

video test pattern generator---tpg_1

axi_lite 接收指令

s_axi_stream和m_axi_stream

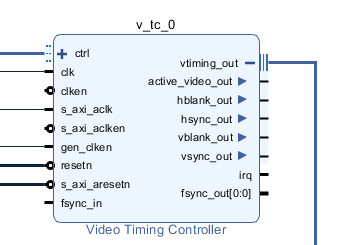

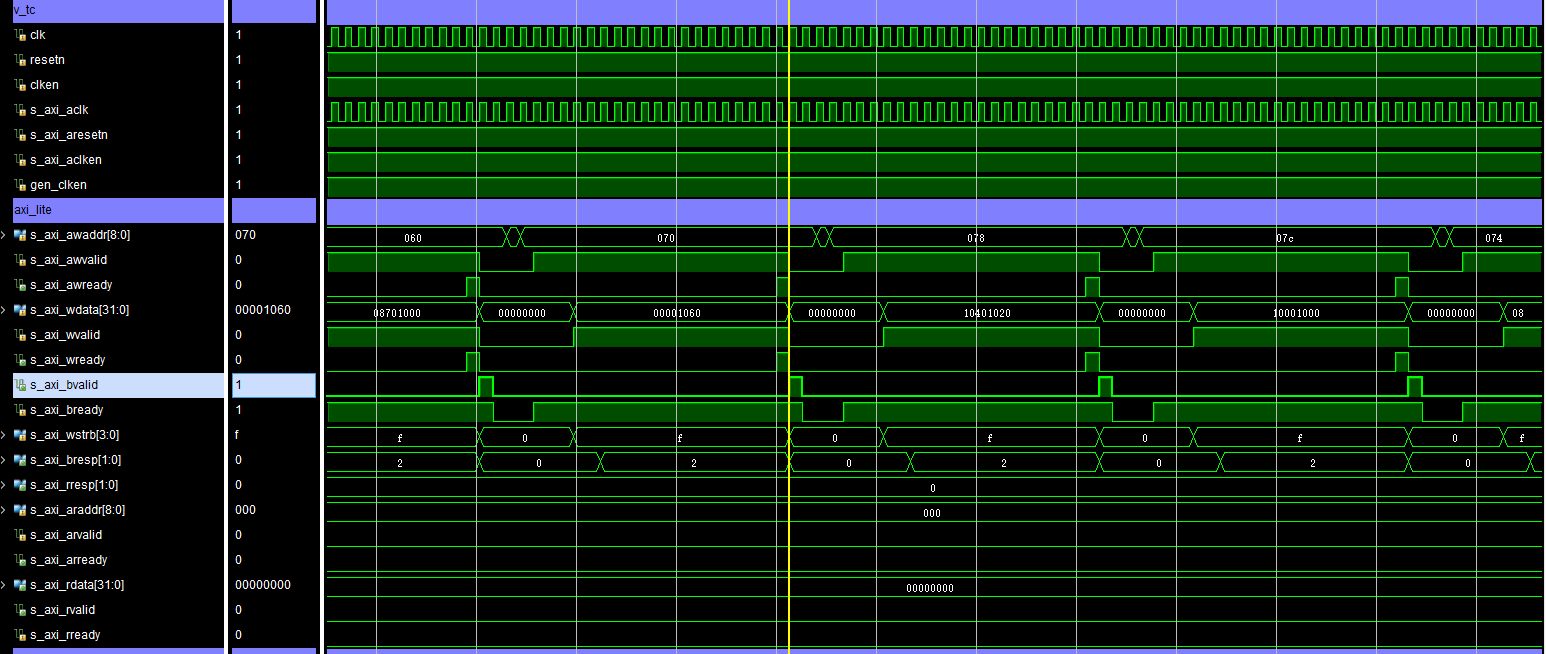

video timing controller---v_tc_0

axi_lite 控制接口

时序信号

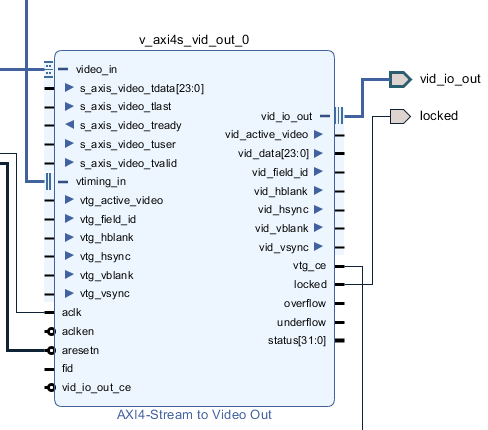

axi4 stream to video out---v_axi4s_vid_out_0

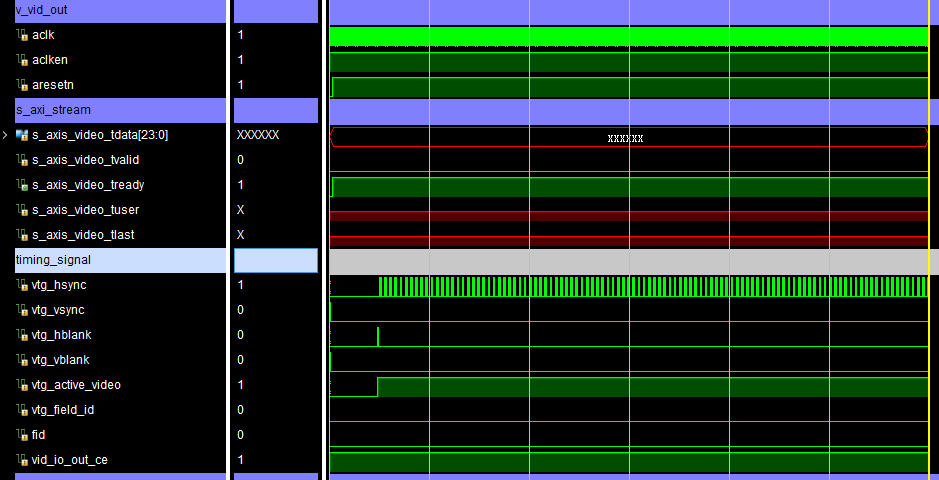

s_axi_stream, timing_signal_in

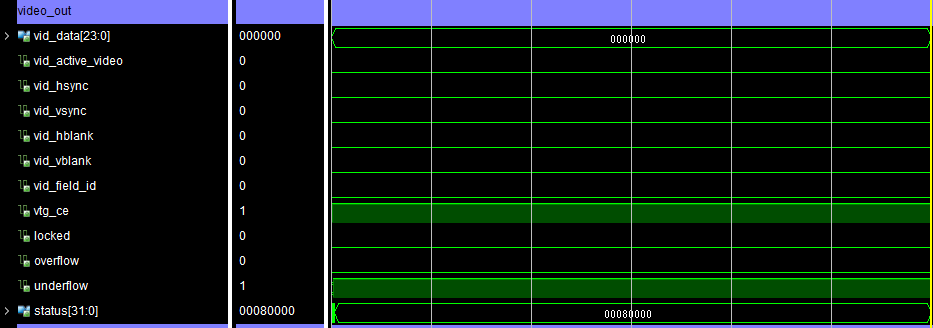

video_out

关于tpg例程的仿真的更多相关文章

- vivado2016.2下系统自带DDR3 ip例程仿真运行

背景:从ISE14.7迁移到vivado2016.2. xilinx的软件改的真是不一般的大.两个软件操作差距真是让人想骂人.由于项目需要,准备调试DDR3.对于新手来说,例化一个DDR3 ip.如果 ...

- 【iCore1S 双核心板_FPGA】例程十一:Modelsim仿真实验

实验现象: 通过仿真波形,分析输入与输出的关系,可以清晰的看到所添加信号波形的变化与程序所写的一致. 核心代码: module modelsim( input CLK_12M, output FPGA ...

- 【iCore3 双核心板_FPGA】例程十二:Modelsim仿真实验

实验指导书及代码包下载: http://pan.baidu.com/s/1bnQEldl iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- stm32 MDK5软件仿真之查看io口输出

软件MDK5 stm32的pack 打开MDK,添加工程 一.首先找到Project的Options选项,里面的Debug选为Use Simulator,也就是选择软件仿真. 然后再Logic ...

- VerilogHDL常用的仿真知识

在描述完电路之后,我们需要进行对代码进行验证,主要是进行功能验证.现在验证大多是基于UVM平台写的systemverilog,然而我并不会sv,不过我会使用verilog进行简单的验证,其实也就是所谓 ...

- ROS学习记录(二)————使用smartcar进行仿真(用.xacro文件来运行rviz)

我发现一个学习ROS系统的好网站: 创客智造http://www.ncnynl.com/ 这里面关于ROS的各个方面都有很详细的介绍. 这周,不,上周我对整个ROS是绝望的,我用一个一个下午的时间在敲 ...

- 搭建Modelsim SE仿真环境-使用do文件仿真

本章我们介绍仿真环境搭建是基于Modelsim SE的.Modelsim有很多版本,比如说Modelsim-Altera,但是笔者还是建议大家使用Modelsim-SE,Modelsim-Altera ...

- ROS进阶学习手记 7.2 -- RViz仿真实例2:Create SmartCar

上一节玩了 exbot 在RViz里的仿真控制,这里我们用urdf文件写个自己的小车模型,ref: http://blog.csdn.net/hcx25909/article/details/8904 ...

- 深入浅出MFC——MFC六大关键技术仿真(二)

1. 仿真MFC目的:以MFC为例,学习application framework的内部运行.MFC六大关键技术: (1)MFC程序的初始化过程 (2)RTTI(Runtime Type Inform ...

随机推荐

- net基础语法

一.net基础语法流程图

- python 爬虫&爬取豆瓣电影top250

爬取豆瓣电影top250from urllib.request import * #导入所有的request,urllib相当于一个文件夹,用到它里面的方法requestfrom lxml impor ...

- MapRedcue的demo(协同过滤)

MapRedcue的演示(协同过滤) 做一个关于电影推荐.你于你好友之间的浏览电影以及电影评分的推荐的协同过滤. 百度百科: 协同过滤简单来说是利用某兴趣相投.拥有共同经验之群体的喜好来推荐用户感兴趣 ...

- Android 音视频深入 十五 FFmpeg 推流mp4文件(附源码下载)

源码地址https://github.com/979451341/Rtmp 1.配置RTMP服务器 这个我不多说贴两个博客分别是在mac和windows环境上的,大家跟着弄 MAC搭建RTMP服务器h ...

- >HTML编辑笔记2

1.列表 ①无序列表 <ul> <li>XXX</li> <li>XXX</li> </ul> ②有序列表 <ol> ...

- 第三组 通信一班 030 OSPFv2、OSPFv3综合实验

一. 实验目的 掌握 OSPFv2. OSPFv3 的配置方法 掌握在帧中继环境下OSPFv2. OSPFv3 的配置方法 掌握 OSPFv2. OSPFv3 NSSA 的配置方法 ...

- python_6

set 集合 {} 无序 s = {1,2,3,4,5} s = {}print(type(s)) # 空{}就是字典 s = {1,2,3,4,5}s = {1,2,3,'22','ss',Fals ...

- effective java——31用实例域代替序数

1,永远不要根据枚举的序数导出与它关联的值,而是要将他保存在一个实例域中.(ordinal()) public enum Ensemble { SOLO, DUET, TRIO, QUARTET, Q ...

- Nginx 单个进程允许的最大连接数

(1) 控制 Nginx 单个进程允许的最大连接数的参数为 worker_connections ,这个参数要根据服务器性能和内存使用量来调整 (2) 进程的最大连接数受 Linux 系统进程的最大打 ...

- java正则表达式appendReplacement和appendTail方法

appendReplacement是java中替换相应字符串的一个方法 appendReplacement(StringBuffer sb,String replacement) 将当前匹配子串替换为 ...