Verilog-case、casez和casex的区别

参考博客:https://www.cnblogs.com/guolongnv/articles/6906929.html

1、基本概念

1)?表示z,而不是“dont care”

2)区分:

case语句的表达式的值有4中情况:0、1、z、x。4种是不同的,故表达式要严格的相等才可以操作分支语句。

casez语句中的表达式情况有三种:0、1、x。不用关心z,z可以和任何数值相等,即z =0.z= 1,z=x;

casex语句的表达式情况有二种:0、1.不用关心x和z。即x=z=0,x=z=1.

2、测试代码

`timescale 1ns / 1ps

module case_compare(

input[:] sel,

output reg [:] y, input[:] z_sel,

output reg [:] z_y, input[:] x_sel,

output reg [:] x_y ); always @(*) begin

case(sel)

'b00: y = 2'b00;

'b01: y = 2'b01;

'b1?: y = 2'b10;

default: y = 'b11;

endcase

end always @(*) begin

casez(z_sel)

'b00: z_y = 2'b00;

'b01: z_y = 2'b01;

'b1?: z_y = 2'b10;

default: z_y = 'b11;

endcase

end always @(*) begin

casex(x_sel)

'b00: x_y = 2'b00;

'b01: x_y = 2'b01;

'b1?: x_y = 2'b10;

default: x_y = 'b11;

endcase

end endmodule

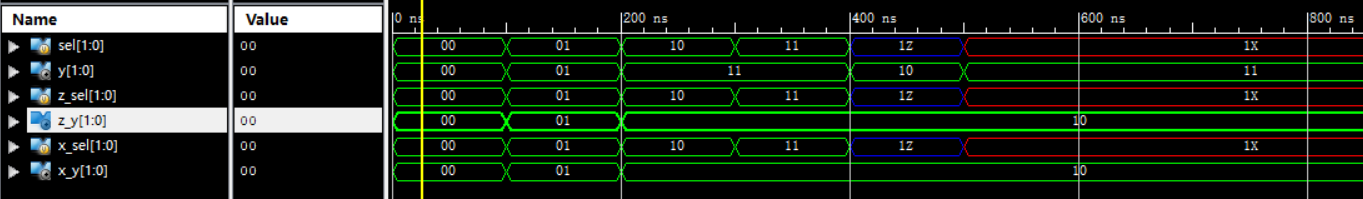

1)前仿真波形

2)综合后仿真波形

对比波形可以看出来,case(不是casez/casex的时候)的index列表里面的x和z,都被综合工具认为是不可达到的状态就被去掉了。

casez和casex里面的x/z都被认为是don't care,所以综合出的电路会是一致的。

3、使用建议

1)我们在写代码的时候如果用了case,那么就不要在index列表里面出现x/z/?,综合工具认不出这些,都会当做don't care

2)casez和casex综合的结果是一致的。

3)casez稍好用一些,因为它可以用来代表don't care的值

4)最重要的一点就是,casez和casex其实没有孰优孰劣

Verilog-case、casez和casex的区别的更多相关文章

- 【FPGA】 007 --Verilog中 case,casez,casex的区别

贴一个链接:http://www.cnblogs.com/poiu-elab/archive/2012/11/02/2751323.html Verilog中 case,casez,casex的区别 ...

- case/casez/casex 的区分与使用

参考:http://www.cnblogs.com/poiu-elab/archive/2012/11/02/2751323.html 与 verilog数字系统设计基础 一般来说,使用最多的是CA ...

- 【原创】case、casez和casex谁是谁

在Verilog中case语句经常用于多分支表决的结构,case后的表达式会与各分支表达式"全等"那么对应的分支会被执行.其基本结构如下: case(expression) exp ...

- case class 和class的区别以及构造器参数辨析

工作中偶然发现Scala构造方法中的参数,无论是否有val/var修饰都可以顺利编译运行,如下: class AA(name: String) class BB(val name: String) 那 ...

- if else if,switch case二者的联系与区别

前段时间在学习中听到了一个关于条件判断语句的问题,分析if else if语句和switch case语句这两者之间的联系和区别,从而使用其中最有效率的一种方法. 一.if...else if if. ...

- verilog case 语句合并问题

有时候在case语句中会有不同选择执行相同操作的情况,为了简化代码,可以将其合并. 以下解答来自百度知道(由于排版问题,有相应修改): reg [1:0]addr_cnt=2'b11; reg rea ...

- 转载 关于case语句的优先级

对于这样的组合逻辑电路 always@(X) case(X) X1: X2: …… endcase 如果分支项包含变量X的所有取值情况,并且互相不重复,那么这样的情况,其实没有必要使用综合指令. (一 ...

- FPGA基础(verilog语言)——语法篇(续1)

上一篇文章提到了FPGA中一个模块基本结构,这篇文章开始介绍语法. 首先,我们学习一门语言都要从这门语言的单词学起,所以verilog中的关键词都有哪些呢?看下面: A:always.assign B ...

- Verilog Tips and Interview Questions

Verilog Interiew Quetions Collection : What is the difference between $display and $monitor and $wr ...

随机推荐

- 使用sass语法生成自己的css的样式库

前言 先说一下 sass 和 scss的区别 sass 是一种缩进语法(即没有花括号和分号,只使用换行 缩进的方式去区别子元素,PS:这是我个人的理解) scss 是css-like语法 (它的语法 ...

- pytorch之 RNN regression

关于RNN模型参数的解释,可以参看RNN参数解释 1 import torch from torch import nn import numpy as np import matplotlib.py ...

- 使用docker创建MySQL容器,并在springboot中使用

最近在看网上找了个springboot的项目试试,在项目中需要的MySQL版本是5.7,但是本机的MySQL只有5.5.因此想着在我的服务器上跑一个MySQL:5.7的容器解决这一问题,但是在实际操作 ...

- cache和内存屏障

1 cache简介 1.1 cache缓存映射规则 tag查看cache是否匹配,set index |tag |set index |block offset ||20-bit |7-bit |5b ...

- get、post请求参数乱码解决方法(qq:1324981084)

java高级架构师全套vip教学视频,需要的加我qq1324981084 在实际的项目中我们会遇见中文乱码的问题,这个问题是很恶心的事,所以我在这里提供了一些解决中文乱码的方法,希望能给大家一些帮助. ...

- Myeclipse maven项目转web项目

右键点击项目,选择project facets,或者在properties选择,点“Convert to faceted from...” 勾选java和Dynamic Web Module 选项 接 ...

- 挂号平台首页开发(UI组件部分)

JQ插件模式开发UI组件 JQ插件开发方法: 1.$.extend() 扩展JQ(比较简单,功能略显不足) $.extend({ sayHello:function(){ console.log(&q ...

- 【WPF学习】第十八章 多点触控输入

多点触控(multi-touch)是通过触摸屏幕与应用程序进行交互的一种方式.多点触控输入和更传统的基于笔(pen-based)的输入的区别是多点触控识别手势(gesture)——用户可移动多根手指以 ...

- 简单的试了试async和await处理异步的方式

今天无意中就来试了试,感觉这个新的方法还是非常行的通的,接下来我们上代码 这段代码想都不用想输出顺序肯定是//null null 233,当然出现这个问题还是因为它是同步,接下来我们就进行异步方式来处 ...

- 剑指offer-面试题59_2-队列的最大值-队列

/* 题目: 定义一个含max函数的队列类,并实现pop_front().push_back().max()函数. */ #include<iostream> #include<cs ...