【原创】case、casez和casex谁是谁

在Verilog中case语句经常用于多分支表决的结构,case后的表达式会与各分支表达式“全等”那么对应的分支会被执行.其基本结构如下:

case(expression)

expr1 : statement_or_null;

…

exprn : statement_or_null;

default : statement_or_null;

endcase

虽然一般case经常被使用,但是在构建仿真验证平台时,经常会遇到case后的敏感表达式出现高阻态z和不定态x的情况,而对于部分位出现高阻态z和不定态x的情况有时需要忽略掉,如下例.

【示例】

`timescale 1 ns / 1 ps

module top_tb;

reg [1:0] d1,d2,d3,d4,d5,d6;

reg [1:0] sel;

reg [1:0] dout;

initial begin

d1 = 2'b00;d2 = 2'b10;d3 = 2'b0x;

d4 = 2'bz0;d5 = 2'bxx;d6 = 2'bzz;

sel = 2'b00;

#1 sel = 2'b10;

#1 sel = 2'b00;

#1 sel = 2'b0x;

#1 sel = 2'bz0;

#1 sel = 2'bxx;

#1 sel = 2'bzz;

#1 sel = 2'b11;

#1 $stop;

end

always @(sel)

begin

case(sel)

2'b00 : begin

dout = d1;

$display("Branch 2'b00!");

end

2'b10 : begin

dout = d2;

$display("Branch 2'b10!");

end

2'b0x : begin

dout = d3;

$display("Branch 2'b0x!");

end

2'bz0 : begin

dout = d4;

$display("Branch 2'bz0!");

end

2'b1x : begin

dout = d5;

$display("Branch 2'b1x!");

end

2'b1z : begin

dout = d6;

$display("Branch 2'b1z!");

end

default : begin

dout = 2'b00;

$display("Branch default!");

end

endcase

end

endmodule // top_tb

【仿真结果】

Sel | Result

2’b00 # Branch 2'b00!

2’b10 # Branch 2'b10!

2’b00 # Branch 2'b00!

2’b0x # Branch 2'b0x!

2’bz0 # Branch 2'bz0!

2’bxx # Branch default!

2’bzz # Branch default!

2’b11 # Branch default!

示例中确实可以将case后的敏感表达式与分支表达式进行全匹配,匹配包括表达式结果的每一位.但是如果期望2’b00和2’b0x或者2’b0z选择执行相同的分支,或者2’b10和2’b1x或者2’b1z选择执行相同的分支,使用原有的case语句是无法实现的,为此,为了满足这种特殊的要求,case语句演变出了两种变体casez和casex.

casez和casex的用法与传统的case一样,只是在敏感表达式和分支表达式匹配时稍有不同,casez语句中,如果分支表达式的结果中某些位的值位高阻z,那么在对这些位进行比较时会忽略不进行比较,仅考虑其他对应位的比较.同理,casex也是会对某些位为z比进行比较,但是其进一步扩展为对包含x的位也不进行比较.

【示例】

`timescale 1 ns / 1 ps

module top_tb;

reg [1:0] d1,d2,d3,d4,d5,d6;

reg [1:0] sel;

reg [1:0] dout;

initial begin

d1 = 2'b00;d2 = 2'b10;d3 = 2'b0x;

d4 = 2'bz0;d5 = 2'bxx;d6 = 2'bzz;

sel = 2'b00;

#1 sel = 2'b10;

#1 sel = 2'b00;

#1 sel = 2'b0x;

#1 sel = 2'bz0;

#1 sel = 2'bxx;

#1 sel = 2'bzz;

#1 sel = 2'b11;

#1 $stop;

end

always @(sel)

begin

casez(sel)

2'b00 : begin

dout = d1;

$display("Branch 2'b00!");

end

2'b10 : begin

dout = d2;

$display("Branch 2'b10!");

end

2'b0x : begin

dout = d3;

$display("Branch 2'b0x!");

end

2'bz0 : begin

dout = d4;

$display("Branch 2'bz0!");

end

2'b1x : begin

dout = d5;

$display("Branch 2'b1x!");

end

2'b1z : begin

dout = d6;

$display("Branch 2'b1z!");

end

default : begin

dout = 2'b00;

$display("Branch default!");

end

endcase

end

endmodule // top_tb

【仿真结果】

Sel | Result

2’b00 # Branch 2'b00!

2’b10 # Branch 2'b10!

2’b00 # Branch 2'b00!

2’b0x # Branch 2'b0x!

2’bz0 # Branch 2'b00!

2’bxx # Branch default!

2’bzz # Branch 2'b00!

2’b11 # Branch 2'b1z!

此处将case替换为casez后,从仿真结果可以看出,2’bz0、2’bzz与2’b00结果一致,即不对敏感表达式与分支表达式中对应位存在z的位进行比较.这里需要注意当sel位2’bzz时,因为不对任何位进行全等检查,所以敏感表达式会与第一个分支匹配.可见casez语句中会忽略表达式中的高阻态位.

【示例】

`timescale 1 ns / 1 ps

module top_tb;

reg [1:0] d1,d2,d3,d4,d5,d6;

reg [1:0] sel;

reg [1:0] dout;

initial begin

d1 = 2'b00;d2 = 2'b10;d3 = 2'b0x;

d4 = 2'bz0;d5 = 2'bxx;d6 = 2'bzz;

sel = 2'b00;

#1 sel = 2'b10;

#1 sel = 2'b00;

#1 sel = 2'b0x;

#1 sel = 2'bz0;

#1 sel = 2'bxx;

#1 sel = 2'bzz;

#1 sel = 2'b11;

#1 $stop;

end

always @(sel)

begin

casex(sel)

2'b00 : begin

dout = d1;

$display("Branch 2'b00!");

end

2'b10 : begin

dout = d2;

$display("Branch 2'b10!");

end

2'b0x : begin

dout = d3;

$display("Branch 2'b0x!");

end

2'bz0 : begin

dout = d4;

$display("Branch 2'bz0!");

end

2'b1x : begin

dout = d5;

$display("Branch 2'b1x!");

end

2'b1z : begin

dout = d6;

$display("Branch 2'b1z!");

end

default : begin

dout = 2'b00;

$display("Branch default!");

end

endcase

end

endmodule // top_tb

【仿真结果】

Sel | Result

2’b00 # Branch 2'b00!

2’b10 # Branch 2'b10!

2’b00 # Branch 2'b00!

2’b0x # Branch 2'b00!

2’bz0 # Branch 2'b00!

2’bxx # Branch 2'b00!

2’bzz # Branch 2'b00!

2’b11 # Branch 2'b1x!

此处将case替换为casex后,从仿真结果可以看出,2’b0x、2’bxx与2’b00结果一致,2’bz0和2’bzz也与结果一致,即不对敏感表达式与分支表达式中对应位存在x和z的位进行比较.可见casex语句中会忽略表达式中的高阻态位和不定态.

【示例】

`timescale 1 ns / 1 ps

module top_tb;

reg [7:0] in;

reg [7:0] out;

initial begin

in = 8'b0000_0000;

#1 in = 8'b0000_0001;

#1 in = 8'b0000_0010;

#1 in = 8'b0000_0100;

#1 in = 8'b0000_1000;

#1 in = 8'b0001_0000;

#1 in = 8'b0010_0000;

#1 in = 8'b0100_0000;

#1 in = 8'b1000_0000;

#1 in = 8'b0010_0100;

#1 in = 8'b1111_0010;

#1 in = 8'b0000_1111;

#1 $stop;

end

always @*

begin

casez(in)

8'bzzzz_zzz1 : out = 0;

8'bzzzz_zz1z : out = 1;

8'bzzzz_z1zz : out = 2;

8'bzzzz_1zzz : out = 3;

8'bzzz1_zzzz : out = 4;

8'bzz1z_zzzz : out = 5;

8'bz1zz_zzzz : out = 6;

8'b1zzz_zzzz : out = 7;

default : out = 0;

endcase

end

endmodule

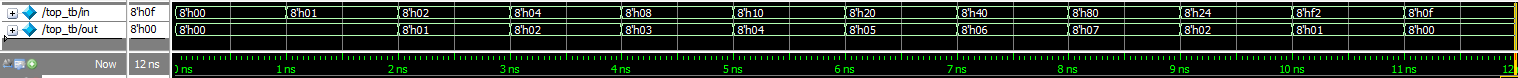

【仿真结果】

从仿真结果可以看出,在进行匹配时,当有多位匹配成功,从右侧开始第一次匹配成功的分支会被执行.示例中in为’h24和’h02的结果是一致的,’h0f和’h01的结果是一致的.

从上述几例可以看出case、casez和casex在对0/1/z/x进行比较时的对应关系如下表:

|

case |

0 |

1 |

X |

Z |

|

casez |

0 |

1 |

X |

Z |

|

casex |

0 |

1 |

X |

Z |

|

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

||

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

||

|

X |

0 |

0 |

1 |

0 |

X |

0 |

0 |

1 |

1 |

X |

1 |

1 |

1 |

1 |

||

|

Z |

0 |

0 |

0 |

1 |

Z |

1 |

1 |

1 |

1 |

Z |

1 |

1 |

1 |

1 |

其中casez语句用来处理不考虑高阻值z的比较过程,casex语句则将高阻态z和不定态都视为忽略,即在表达式进行比较时,不将该位进行比较,这样根据具体需要灵活使用casex和casez了.

综上所述,case进行精确比较,会对每一位不管该位是0/1/z/x的任何值;casez进行忽略z的比较,如果敏感表达式和分支表达式中有一位为z,那么在比较时该位的比较忽略;casex进行忽略x和z的比较,如果敏感表达式和分支表达式中有一位为x或者z,那么在比较时该位的比较忽略,当有多位都可匹配时,仅从右侧开始第一次匹配成功的分支会被执行.

【原创】case、casez和casex谁是谁的更多相关文章

- case/casez/casex 的区分与使用

参考:http://www.cnblogs.com/poiu-elab/archive/2012/11/02/2751323.html 与 verilog数字系统设计基础 一般来说,使用最多的是CA ...

- 【FPGA】 007 --Verilog中 case,casez,casex的区别

贴一个链接:http://www.cnblogs.com/poiu-elab/archive/2012/11/02/2751323.html Verilog中 case,casez,casex的区别 ...

- Verilog-case、casez和casex的区别

参考博客:https://www.cnblogs.com/guolongnv/articles/6906929.html 1.基本概念 1)?表示z,而不是“dont care” 2)区分: case ...

- 写自己的第二级处理器(3)——Verilog HDL行为语句

我们会继续上传新书<自己动手写处理器>(未公布),今天是第七章,我每星期试试4 2.6 Verilog HDL行为语句 2.6.1 过程语句 Verilog定义的模块一般包含有过程语句,过 ...

- FPGA代码设计规范整理

1.设计中的FIFO.状态机接口需要有异常恢复状态和状态上报机制,格雷码电路防止被综合电路优化掉. a)自行设计的格雷码FIFO(一般用于连续数据流跨时钟域)用Synplify综合时,为了防止被优化需 ...

- Verilog Tips and Interview Questions

Verilog Interiew Quetions Collection : What is the difference between $display and $monitor and $wr ...

- Verilog_Day3

内容为书中第5章 条件语句 条件语句必须在过程块语句中使用.所谓过程块语句是指由 initial 和 always 语句引导的执行语句集合.除这两种块语句引导的begin_end块中可以编写条件语句外 ...

- verilog FAQ(zz)

1. What is the race condition in verilog? Ans :The situation when two expressions are allowed to exe ...

- FPGA基础(verilog语言)——语法篇(续1)

上一篇文章提到了FPGA中一个模块基本结构,这篇文章开始介绍语法. 首先,我们学习一门语言都要从这门语言的单词学起,所以verilog中的关键词都有哪些呢?看下面: A:always.assign B ...

随机推荐

- centos 7 增加一块硬盘的步骤

1) 增加一块硬盘 1G [到设置中添加一块硬盘即可] 2) 重启一下服务器 lsblk -f 查看硬盘 3) 给 sdb 硬盘分区 fdisk /dev/sdb n,p,enter,enter,w ...

- 「模拟8.19 A嚎叫..(set) B主仆..(DFS) C征程..(DP+堆优化)」

为啥这一套题目背景感到很熟悉. T1 嚎叫响彻在贪婪的厂房 考试一个小时没调出来,自闭了.......... 正解很好想,最后实在打不出来了只好暴力骗分了... 联想到以前做的题:序列(涉及质因数分 ...

- 使用A Star 算法实现自动寻路详解

@ 目录 1.什么是A Start算法 2.A Star算法的原理和流程 2.1 前提 2.1.1 从起点开始扩散的节点 2.1.2 最短距离计算公式:F = G + H 2.1.3 欧几里得距离计算 ...

- 16、lnmp_mysql二进制安装

16.1.lnmp介绍: lnmp架构,linux的php的程序架构: linux nginx MySQL PHP; # lamp:linux apache mysql php; 16.2.mysql ...

- POJ 2002 二分 计算几何

根据正方形对角的两顶点求另外两个顶点公式: x2 = (x1+x3-y3+y1)/2; y2 = (x3-x1+y1+y3)/2; x4= (x1+x3+y3-y1)/2; y4 = (-x3+x1+ ...

- Docker:Docker常用命令

docker信息 ##查看docker容器版本 docker version ##查看docker容器信息 docker info ##查看docker容器帮助 docker --help 镜像列表 ...

- java 的 IO简单理解

首先要先理解什么是 stream ? stream代表的是任何有能力产出数据的数据源,或是任何有能力接收数据的接收源. 一.不同导向的 stream 1)以字节为单位从 stream 中读取或往 st ...

- Java实验项目三——职工类对象数组按照职工生日排序

Program: 修改项目三(1)中的第3题,实现比较方法,将对象数组的数据按照生日的大小给职工排序. Description:令日期类MyDate和员工类Worker类实现接口Comparable, ...

- 羊城杯wp babyre

肝了好久,没爆破出来,就很难受,就差这题没写了,其他三题感觉挺简单的,这题其实也不是很难,我感觉是在考算法. 在输入之前有个smc的函数,先动调,attach上去,ida打开那个关键函数. 代码逻辑还 ...

- 重学Docker

转了云方向,代码都少写了 1. 为什么出现Docker 以前开发项目有开发的环境.测试的环境.还有生产的环境,每经过一阶段就要迁移项目.不同的环境有不同的配置,可能导致不可预估的错误,运维要经常性的改 ...