高云SOC芯片GW1NSR-LV4CQN48的ARM总线

高云SOC芯片GW1NSR-LV4CQN48的ARM总线

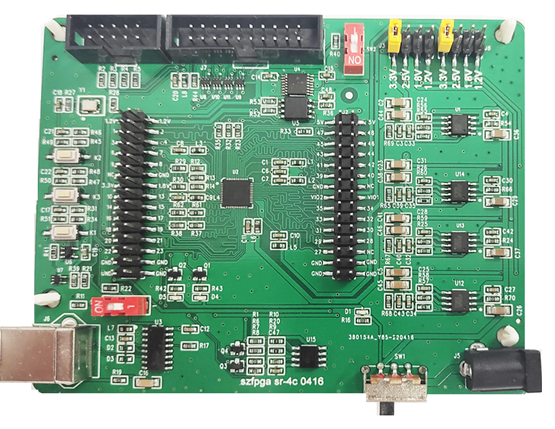

国产GOWIN高云出的一款芯片是GW1NSR-LV4CQN48PC7/I6,QN48封装,资源是4608,有10个18K BRAM,以及2个PLL,内置HyperRAM 64Mb, 可以用于电机,图像测试。内置ARM-M3硬核,可以替换简单的MCU应用。

其中ARM和FPGA的总线连接是两种AHB和APB总线。以下介绍的基本总线的连接代码。

其中AHB总线是包含BURST突发模式读取数据内容。实际从波形调试可以得到每次突发模式8个数据内容。

module Gowin_AHB_Multiple

(

output wire [31:0] AHB_HRDATA,

output wire AHB_HREADY,

output wire [ 1:0] AHB_HRESP,

input wire [ 1:0] AHB_HTRANS,

input wire [ 2:0] AHB_HBURST,

input wire [ 3:0] AHB_HPROT,

input wire [ 2:0] AHB_HSIZE,

input wire AHB_HWRITE,

input wire AHB_HMASTLOCK,

input wire [ 3:0] AHB_HMASTER,

input wire [31:0] AHB_HADDR,

input wire [31:0] AHB_HWDATA,

input wire AHB_HSEL,

input wire AHB_HCLK,

input wire AHB_HRESETn

);

//The AHB BUS is always ready

assign AHB_HREADY = 1'b1; //ready signal, slave to MCU master

//Response OKAY

assign AHB_HRESP = 2'b0;//response signal, slave to MCU master

//Define Reg for AHB BUS

reg [31:0] ahb_address;

reg ahb_control;

reg ahb_sel;

reg ahb_htrans;

always @(posedge AHB_HCLK or negedge AHB_HRESETn)

begin

if(~AHB_HRESETn)

begin

ahb_address <= 32'b0;

ahb_control <= 1'b0;

ahb_sel <= 1'b0;

ahb_htrans <= 1'b0;

end

else //Select The AHB Device

begin //Get the Address of reg

ahb_address <= AHB_HADDR;

ahb_control <= AHB_HWRITE;

ahb_sel <= AHB_HSEL;

ahb_htrans <= AHB_HTRANS[1];

end

end

wire write_enable = ahb_htrans & ahb_control & ahb_sel;

wire read_enable = ahb_htrans & (!ahb_control) & ahb_sel;

//The register of Multiple AHB bus

reg [7:0 ] Multiplier;

reg [7:0 ] Multiplicand;

reg [15:0] The_result;

reg [1:0 ] Cmd_reg; //The Bit0 -> Start

//The Bit1 -> The State of Multiple

wire cmd_finished_status ;

wire [15:0] wire_multiple_result;

//write data to AHB bus

always @(posedge AHB_HCLK or negedge AHB_HRESETn)

begin

if(~AHB_HRESETn)

begin

Multiplier <= 8'b0;

Multiplicand <= 8'b0;

end

else if(write_enable)

begin

case (ahb_address[15:0])

16'h0000: Multiplier <= AHB_HWDATA[7:0];

16'h0004: Multiplicand <= AHB_HWDATA[7:0];

endcase

end

end

//Status

always @(posedge AHB_HCLK or negedge AHB_HRESETn)

begin

if(~AHB_HRESETn)

begin

Cmd_reg <= 2'b0;

end

else if(write_enable &(ahb_address[15:0] == 16'h0008))

begin

Cmd_reg <= AHB_HWDATA[1:0];

end

else if(cmd_finished_status)

begin

Cmd_reg <= 2'b10;

end

end

//read data to AHB bus

always @(posedge AHB_HCLK or negedge AHB_HRESETn)

begin

if(~AHB_HRESETn)

begin

The_result <= 16'b0;

end

else if(cmd_finished_status)

begin

The_result <= wire_multiple_result;

end

end

//register address

reg [31:0] ahb_rdata;

always @(*)

begin

if(read_enable) //read cmd

begin

case (ahb_address[15:0])

32'h0000: ahb_rdata = Multiplier;

32'h0004: ahb_rdata = Multiplicand;

32'h0008: ahb_rdata = Cmd_reg;

32'h000C: ahb_rdata = The_result;

default:ahb_rdata = 32'hFFFFFFFF;

endcase

end

else

begin

ahb_rdata = 32'hFFFFFFFF;

end

end

assign AHB_HRDATA = ahb_rdata;

而对于APB的总线,一次性只能读取一个数据内容。

module Gowin_APB2_Multiple

(

//---------------------The Port declartion--------

input pclk, // master clock input

input presetn, //synchronous active low reset

input psel, //slave sel

input penable, //enable

input pwrite, //transmit direction

input [11:2] paddr, //lower address bits

input [31:0] pwdata, //write data

output [31:0] prdata //read data

);

wire write_enable = psel & pwrite & (!penable);

wire read_enable = psel & (!pwrite) & penable;

//The register of apb bus

reg [7:0 ] Multiplier;

reg [7:0 ] Multiplicand;

reg [15:0] The_result;

reg [1:0 ] Cmd_reg; //The Bit0 -> Start

//The Bit1 -> The State of Multiple

//write Block

always @(posedge pclk or negedge presetn)

begin

if(~presetn)

begin

Multiplier <= 8'b0;

Multiplicand <= 8'b0;

end

else

begin

if(write_enable)

begin

case (paddr[11:2])

10'h00: Multiplier <= pwdata;

10'h01: Multiplicand <= pwdata;

endcase

end

end

end

reg [31:0] prdata_out;

//Read Block

always @(*)

begin

if (read_enable)

begin

case (paddr[11:2])

10'h00: prdata_out = Multiplier;

10'h01: prdata_out = Multiplicand;

10'h02: prdata_out = Cmd_reg;

10'h03: prdata_out = The_result;

default: prdata_out = 32'hFFFFFFFF;//Indicate the unvalid state

endcase

end

else

begin

prdata_out = 32'hFFFFFFFF;

end

end

assign prdata = prdata_out;

高云SOC芯片GW1NSR-LV4CQN48的ARM总线的更多相关文章

- ARM总线方面知识

AMBA简介 随着深亚微米工艺技术日益成熟,集成电路芯片的规模越来越大.数字IC从基于时序驱动的设计方法,发展到基于IP复用的设计方法,并在SOC设计中得到了广泛应用.在基于IP复用的SoC设计中,片 ...

- SOC芯片的FPGA原型验证

FPGA验证在SOC设计非常重要,一般而言,做一些RAM和FIFO的替换以及相应代码转换.具体分下面几步: 1 替换RAM,FIFO和时钟 RAM和FIFO控制器需要RAM的接口都放在了设计顶层,方便 ...

- IN612 IN612L蓝牙5.0 SoC芯片替换NRF52832/NRF52840

IN612L是美国公司INPLAY的SOC产品系列之一,具有多模协同2.4G无线协议栈,支持2.4G私有协议栈以及蓝牙5.0全协议栈的SOC芯片.如2mbps高数据速率模式,125kbps/500kb ...

- ASR6601:国产化lora SOC芯片兼容SX1262/SX1268

ASR6601为目前首颗国产化支持LoRaWAN低功耗广域网无线通信SoC芯片.ASR6601在单芯片上集成了通用微控制器和射频单元(SX1262),包括射频收发器,调制解调器和48 MHz 主频.A ...

- Hi3518 网络监控SOC芯片规格参数

Hi3518 网络监控SOC芯片 视频编解码 处理器内核 ● ARM926@ 440MHz,16KB I-Cache ,16KB D-Cache 视频编码 ● H.264 Main Pro ...

- CPU缓存是位于CPU与内存之间的临时数据交换器,它的容量比内存小的多但是交换速度却比内存要快得多。CPU缓存一般直接跟CPU芯片集成或位于主板总线互连的独立芯片上

一.什么是CPU缓存 1. CPU缓存的来历 众所周知,CPU是计算机的大脑,它负责执行程序的指令,而内存负责存数据, 包括程序自身的数据.在很多年前,CPU的频率与内存总线的频率在同一层面上.内存的 ...

- CI2454国产8位RISC核SoC芯片

Ci2454是一款集成无线收发器和8位RISC(精简指令集)MCU的SOC芯片.主要应用在遥控玩具.智能灯控.数据透传.工业控制等领域.无线收发器主要特性 工作在 2.4GHz ISM 频段. 调制方 ...

- 手机Soc芯片简介

手机SoC(System On a Chip,在一个芯片里面集成CPU.GPU.SP.ISP.RAM内存.Wi-Fi控制器.基带芯片以及音频芯片等)芯片(基于arm架构指令集) 高通骁龙(Snapdr ...

- ARM总线架构

S3C2440集成了丰富了外设控制器(LCD控制器.USB Device控制器.USB Host控制器.NAND FLASH控制器.I2C控制器.SPI控制器等).要控制这些外设就要设置相应控制器的寄 ...

- Nordic nRF52820超低功耗蓝牙5.2 SoC芯片-低端无线连接方案首选

nRF52820是功耗超低的低功耗蓝牙 (Bluetooth Low Energy /Bluetooth LE).蓝牙mesh.Thread.Zigbee和2.4 GHz专有低端无线连接解决方案.nR ...

随机推荐

- git 常见命令和资源

git练习 常用git清单 强制切换分支所指位置 git branch -f main c3强制分支main指向c3 git branch -f main HEAD~3强制分支main指向head的父 ...

- 6 定时器 &中断管理&资源管理

生成函数 周期,多久触发一次定时器(从定时器启动开始计算) 触发什么呢? 回调函数被调用,被谁调用呢 1,tick中断去调用timer函数 Linux中使用这个 (定时器回调函数若执行时间过长, ...

- The History of the English language 英语语音的起源 - 英语的历史 - 古英语 印欧语 希腊语 拉丁语

印欧语 希腊语 拉丁语 日耳曼语 都是什么年代的语言 https://time.graphics/line/776755 印欧语是指印欧语系,它最初被认为在公元前2500年左右分散流传于欧洲.亚洲和印 ...

- AutoTipZen 实时根据文字是否溢出 提示title

AutoTipZen 实时根据文字是否溢出 提示title <template> <div ref="autoTipRef" @mouseover="o ...

- 玩转Vue3之shallowRef和shallowReactive

前言 Vue3 作为一款现代的 JavaScript 框架,引入了许多新的特性和改进,其中包括 shallowRef 和 shallowReactive.这两个功能在Vue 3中提供了更加灵活和高效的 ...

- manjaro系统的xfce桌面环境的的壁纸存放位置

/usr/share/backgrounds/xfce 添加新照片的命令是: sudo mv 目录/* /usr/share/backgrounds/xfce

- 市场主流的G-sensor芯片盘点

一 前记 1.简介 随着可穿戴智能硬件的广泛发展,G-sensor成了一个必不可少的器件.梳理,测试和运用这些传感器.是做可穿戴产品必不可少的环节. 二 产品解析 1.ST的G-sensor型号LIS ...

- BigDecimal类处理高精度计算

BigDecimal类处理高精度计算 Java在java.math包中提供的API类BigDecimal,用来对超过16位有效位的数进行精确的运算.双精度浮点型变量double可以处理16位有效数,但 ...

- openssl 版本兼容问题 备忘录

第三方依赖openssl,但openssl却有版本不同符号不兼容的问题,由于条件限制不得不使用固定版本的openssl,又或者同时有两个第三方依赖不同版本的openssl,只能靠手动,为了备忘. 1. ...

- leetcode数据库sql之Delete Duplicate Emails

leetcode原文引用: Write a SQL query to delete all duplicate email entries in a table named Person, keepi ...