FPGA使用两个HC595驱动8位数码管

FPGA使用两个HC595驱动8位数码管

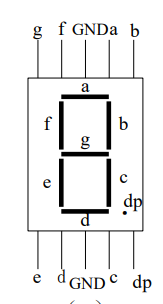

本文章给出使用FPGA3根线来驱动8位数码管的示例代码,输入为disp_data,共7*8=56位,输出输入如图所示。

硬件方面参数

- 该程序只能控制数码管的7位,如有小数点位则控制不了,如有需要请自行修改。

- 最低7位是最右边的那个数码管(这个需要根据你自己的板子硬件连接来看)。

- 0是亮,1是灭(共阳极数码管是这样,共阴极则相反,如为共阴极则需要修改

HEX8中对应的内容)。 - a是7位中的最低位。

程序

- 顶层程序

module HEX_top(

Clk,

Rst_n,

disp_data,

SH_CP,

ST_CP,

DS

);

input Clk; //50M

input Rst_n;

output SH_CP; //shift clock

output ST_CP; //latch data clock

output DS; //data

input disp_data;

wire [7:0] sel;//数码管位选(选择当前要显示的数码管)

wire [6:0] seg;//数码管段选(当前要显示的内容)

wire [55:0] disp_data;

HEX8 HEX8(

.Clk(Clk),

.Rst_n(Rst_n),

.En(1'b1),

.disp_data(disp_data),

.sel(sel),

.seg(seg)

);

HC595_Driver HC595_Driver(

.Clk(Clk),

.Rst_n(Rst_n),

.Data({1'b1,seg,sel}),

.S_EN(1'b1),

.SH_CP(SH_CP),

.ST_CP(ST_CP),

.DS(DS)

);

endmodule

- 8位7段数码管显示设计

module HEX8(

Clk,

Rst_n,

En,

disp_data,

sel,

seg

);

input Clk; //50M

input Rst_n;

input En; //数码管显示使能,1使能,0关闭

input [55:0]disp_data;

output [7:0] sel;//数码管位选(选择当前要显示的数码管)

output wire [6:0] seg;//数码管段选(当前要显示的内容)

reg [14:0]divider_cnt;//25000-1

reg clk_1K;

reg [7:0]sel_r;

reg [7:0]data_tmp;//数据缓存

// 分频计数器计数模块

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

divider_cnt <= 15'd0;

else if(!En)

divider_cnt <= 15'd0;

else if(divider_cnt == 24999)

divider_cnt <= 15'd0;

else

divider_cnt <= divider_cnt + 1'b1;

//1K扫描时钟生成模块

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

clk_1K <= 1'b0;

else if(divider_cnt == 24999)

clk_1K <= ~clk_1K;

else

clk_1K <= clk_1K;

//8位循环移位寄存器

always@(posedge clk_1K or negedge Rst_n)

if(!Rst_n)

sel_r <= 8'b0000_0001;

else if(sel_r == 8'b1000_0000)

sel_r <= 8'b0000_0001;

else

sel_r <= sel_r << 1;

always@(*)

case(sel_r)

8'b0000_0001:data_tmp = disp_data[6:0];

8'b0000_0010:data_tmp = disp_data[13:7];

8'b0000_0100:data_tmp = disp_data[20:14];

8'b0000_1000:data_tmp = disp_data[27:21];

8'b0001_0000:data_tmp = disp_data[34:28];

8'b0010_0000:data_tmp = disp_data[41:35];

8'b0100_0000:data_tmp = disp_data[48:42];

8'b1000_0000:data_tmp = disp_data[55:49];

default:data_tmp = 7'b0000000;

endcase

assign seg = data_tmp;

assign sel = (En)?sel_r:8'b0000_0000;

endmodule

- 74HC595移位寄存器驱动设计

module HC595_Driver(

Clk,

Rst_n,

Data,

S_EN,

SH_CP,

ST_CP,

DS

);

parameter DATA_WIDTH = 16;

input Clk;

input Rst_n;

input [DATA_WIDTH-1 : 0] Data; //data to send

input S_EN; //send en

output reg SH_CP; //shift clock

output reg ST_CP; //latch data clock

output reg DS; //shift serial data

parameter CNT_MAX = 4;

reg [15:0] divider_cnt;//分频计数器

wire sck_pluse;

reg [4:0]SHCP_EDGE_CNT;//SH_CP EDGE counter

reg [15:0]r_data;

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

r_data <= 16'd0;

else if(S_EN)

r_data <= Data;

else

r_data <= r_data;

//clock divide

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

divider_cnt <= 16'd0;

else if(divider_cnt == CNT_MAX)

divider_cnt <= 16'd0;

else

divider_cnt <= divider_cnt + 1'b1;

assign sck_pluse = (divider_cnt == CNT_MAX);

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)

SHCP_EDGE_CNT <= 5'd0;

else if(sck_pluse)begin

if(SHCP_EDGE_CNT == 5'd31)

SHCP_EDGE_CNT <= 5'd0;

else

SHCP_EDGE_CNT <= SHCP_EDGE_CNT + 1'd1;

end

else

SHCP_EDGE_CNT <= SHCP_EDGE_CNT;

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)begin

SH_CP <= 1'b0;

ST_CP <= 1'b0;

DS <= 1'b0;

end

else begin

case(SHCP_EDGE_CNT)

5'd0:begin SH_CP <= 1'b0; ST_CP <= 1'b1; DS <= r_data[15]; end

5'd1:begin SH_CP <= 1'b1; ST_CP <= 1'b0;end

5'd2:begin SH_CP <= 1'b0; DS <= r_data[14];end

5'd3:begin SH_CP <= 1'b1; end

5'd4:begin SH_CP <= 1'b0; DS <= r_data[13];end

5'd5:begin SH_CP <= 1'b1; end

5'd6:begin SH_CP <= 1'b0; DS <= r_data[12];end

5'd7:begin SH_CP <= 1'b1; end

5'd8:begin SH_CP <= 1'b0; DS <= r_data[11];end

5'd9:begin SH_CP <= 1'b1; end

5'd10:begin SH_CP <= 1'b0; DS <= r_data[10];end

5'd11:begin SH_CP <= 1'b1; end

5'd12:begin SH_CP <= 1'b0; DS <= r_data[9];end

5'd13:begin SH_CP <= 1'b1; end

5'd14:begin SH_CP <= 1'b0; DS <= r_data[8];end

5'd15:begin SH_CP <= 1'b1; end

5'd16:begin SH_CP <= 1'b0; DS <= r_data[7];end

5'd17:begin SH_CP <= 1'b1; end

5'd18:begin SH_CP <= 1'b0; DS <= r_data[6];end

5'd19:begin SH_CP <= 1'b1; end

5'd20:begin SH_CP <= 1'b0; DS <= r_data[5];end

5'd21:begin SH_CP <= 1'b1; end

5'd22:begin SH_CP <= 1'b0; DS <= r_data[4];end

5'd23:begin SH_CP <= 1'b1; end

5'd24:begin SH_CP <= 1'b0; DS <= r_data[3];end

5'd25:begin SH_CP <= 1'b1; end

5'd26:begin SH_CP <= 1'b0; DS <= r_data[2];end

5'd27:begin SH_CP <= 1'b1; end

5'd28:begin SH_CP <= 1'b0; DS <= r_data[1];end

5'd29:begin SH_CP <= 1'b1; end

5'd30:begin SH_CP <= 1'b0; DS <= r_data[0];end

5'd31:begin SH_CP <= 1'b1; end

endcase

end

endmodule

代码来自于小梅哥的资料,进行了部分修改,使得整个程序可以更方便的被移植

FPGA使用两个HC595驱动8位数码管的更多相关文章

- 树莓派进阶之路 (016) - 通过595驱动4位LED显示系统时间

模块图片,4位共阳极数码管. 我们使用树莓派wiringPi的库来通过74HC595驱动4位数码管: C 代码如下: #include <wiringPi.h> #include < ...

- 【C语言】求两个数中不同的位的个数

//求两个数中不同的位的个数 #include <stdio.h> int count_different(int a, int b) { int count = 0; int c = a ...

- AVR单片机8位数码管显示的程序实现

AVR单片机8位数码管显示的程序实现 转载:http://www.sohu.com/a/117255149_119709 2016-10-26 16:30 我们接着来完成 数码管的显示实验.现在我 ...

- #51单片机#8位数码管(74HC595芯片)的使用方法

数码管基本属性:1.采用2片595驱动数码管,需要单片机3路IO口,根据数码管动态扫描原理进行显示:2.宽工作电压3.3V到5V:3.PCB板尺寸:71mm*22mm4.数码管型号:0.36 4位共阳 ...

- 基于FPGA的4x4矩阵键盘驱动调试

好久不见,因为博主最近两个月有点事情,加上接着考试,考完试也有点事情要处理,最近才稍微闲了一些,这才赶紧记录分享一篇博文.FPGA驱动4x4矩阵键盘.这个其实原理是十分简单,但是由于博主做的时候遇到了 ...

- 我的 FPGA 学习历程(10)—— 实验:数码管驱动

根据黑金 AX301 手册,数码管位选信号命名为 SEL[5:0],其中 SEL[5] 对应最左边的数码管,而SEL[0] 对应最右边数码管:作为约定,在下面的描述中我们对应的称之为数码管 5 和数码 ...

- python-mysql驱动64位

安装Python-MySQL驱动一直没有成功: https://pypi.python.org/pypi/MySQL-python/1.2.5#downloads 上面网站下的版本安装都不能通过 提示 ...

- 两个int(32位)整数m和n的二进制表达中,有多少个位(bit)不同

思路:利用&用算加右移的方法来提取二进制中的每一位数,然后进行比较,查看是否相同. #include<stdio.h> #include<stdlib.h> int m ...

- C++:用字符串数组实现大数运算,以两个不高于40位的大数运算为例。

因为基本数据类型中整型的内存范围有限,所以直接进行大数之间的运算,不仅浪费空间,而且运行缓慢,甚至有些会导致数据溢出. 那怎么办呢? 这时我们就想直接不行,那咱们来间接的. 这就是我们今天主要要讲的: ...

- FPGA图像处理 两路sensor的色调不一致

怎么调?可以让两路sensor的色调一致.

随机推荐

- 告别手动敲代码!VSCODE 风格在线可视化开发平台,效率飙升!

2025 年 2 月 21 日消息,对于广大开发者而言,今天迎来一则重大利好消息!一款操作布局与 VSCODE 极为相似的可视化开发神器 --Joker 智能可视化开发平台正式上线.无论你是深耕前端领 ...

- Spring定时任务的秘密

Spring定时任务的秘密 在 Spring 框架中,定时任务主要通过 @Scheduled 注解或 TaskScheduler 接口实现. 1.基本使用 在 Spring Boot 项目中,通过 @ ...

- 团队小规模本地大模型服务平台搭建 - Ubuntu

实现目标和考虑因素 部署一个支持多用户同时使用.多模型运行的离线局域网大模型服务器 需要考虑以下几个关键因素: 大模型的加载和管理.使用一个基础大模型,根据实战需要创建多个专用模型,模型管理方便可靠. ...

- 一个属性同时使用Autowired和Resource注解会发生什么?

首发于公众号:BiggerBoy 右侧图片wx扫码关注有惊喜 欢迎关注,查看更多技术文章 如题,如果在同一个属性上使用@Autowired注解注入bean1,然后使用@Resource注解注入bean ...

- MySQL性能调优必知:Performance Schema引擎的配置与使用

当你在MySQL高并发情况下的进行性能调优时,需要知道调整后的影响.例如查询是否变快了?锁是否会减慢运行速度?内存使用情况如何?磁盘IO等待时间变了吗? . Performance Schema就有一 ...

- 【Python】面向对象版学员管理系统

面向对象版学员管理系统 一. 系统需求 使用面向对象编程思想完成学员管理系统的开发,具体如下: 系统要求:学员数据存储在文件中 系统功能:添加学员.删除学员.修改学员信息.查询学员信息.显示所有学员信 ...

- 【电脑】重装Win10之后无法唤醒和正常关机(Y9000P 2022)

问题: Y9000P 2022 改Windows10后经常关机关不全(自带键盘灯亮,电源指示灯不灭),这还不是最重要的,它一会儿不用到时间自动休眠后还经常唤醒不了 解决: 两个问题,总结一下: 一.关 ...

- TCP延迟调优之PSH参数与passt延迟问题修复

qemu中使用passt来作为虚拟机的网卡NAT实现,希望能够利用它IP地址与host一致的优点.这本来是没有啥问题的,但是不知道为什么它的TCP入口流量的延迟很严重. 好吧,反正以后总是要改pass ...

- Windows 左ctrl和左alt键互换

reg代码 Windows Registry Editor Version 5.00 [HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Control\Keyb ...

- docker发布简单python服务

进入机器创建一个目录mkdir dockerbuild1.编写简单flask代码vi flaskapp.pyfrom flask import Flaskimport os app = Flask(_ ...