MMCM与PLL

MMCM与PLL

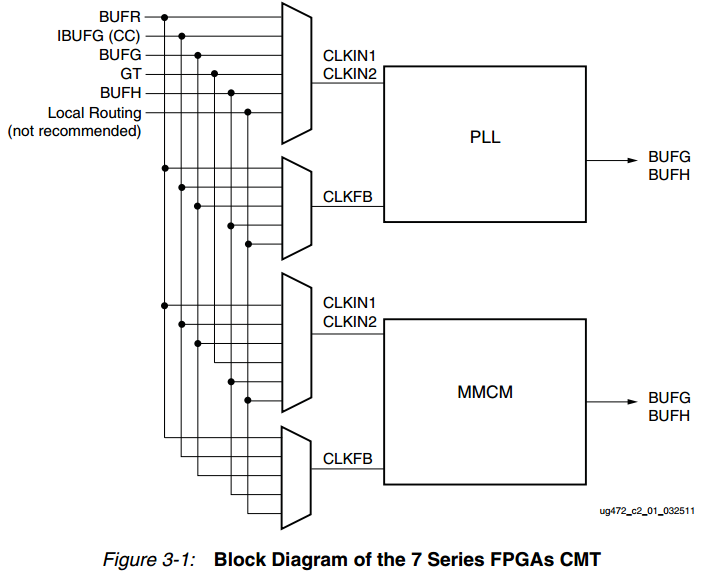

1.the clock management title(CMT)

弄清楚BUFR, IBUFG,BUFG,GT,BUFH,是什么。

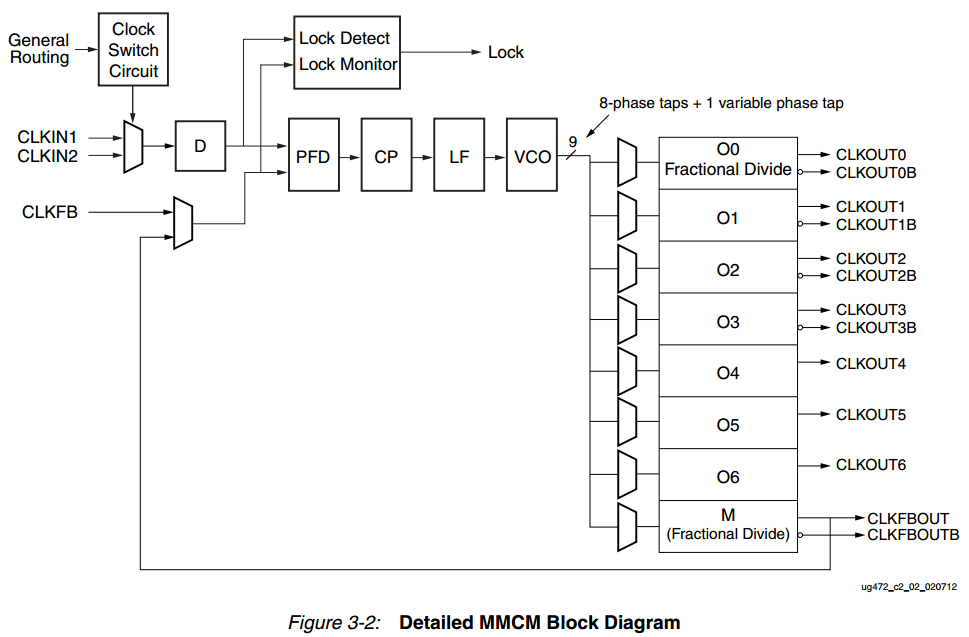

2.MMCM内部结构

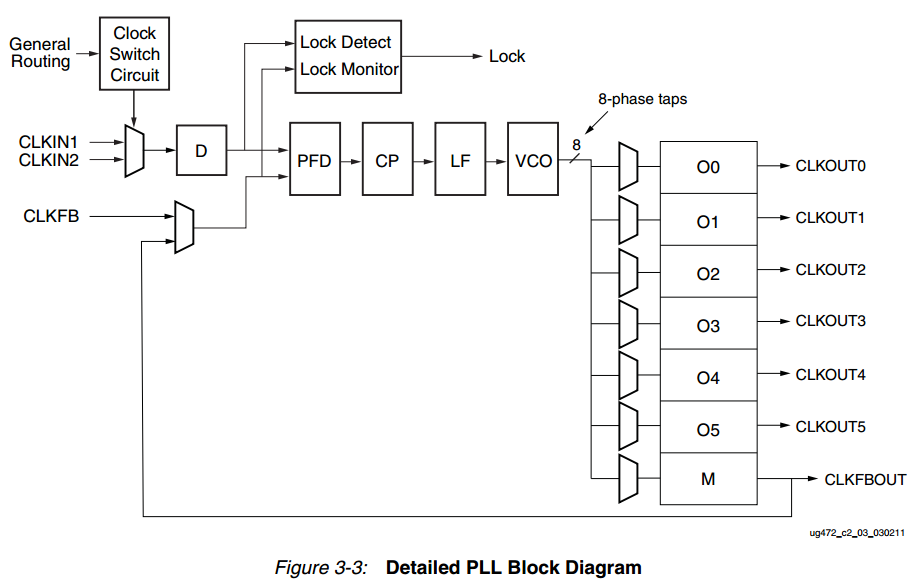

3.PLL内部结构

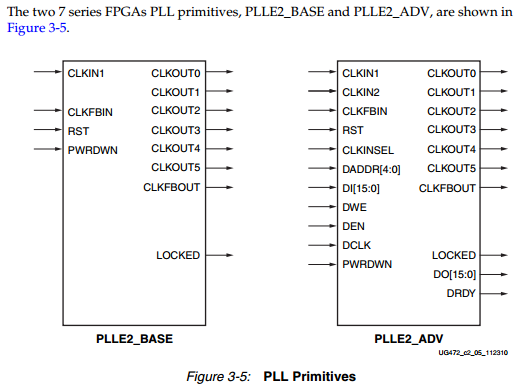

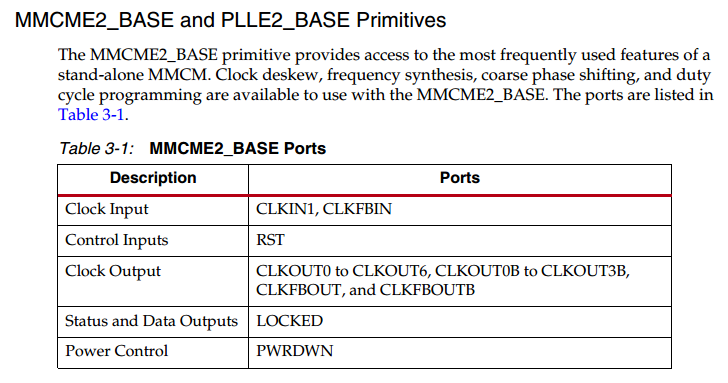

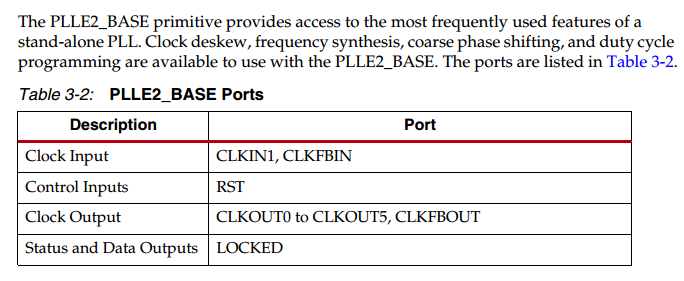

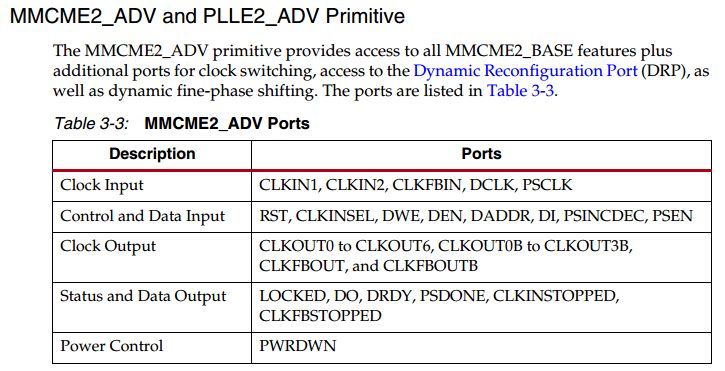

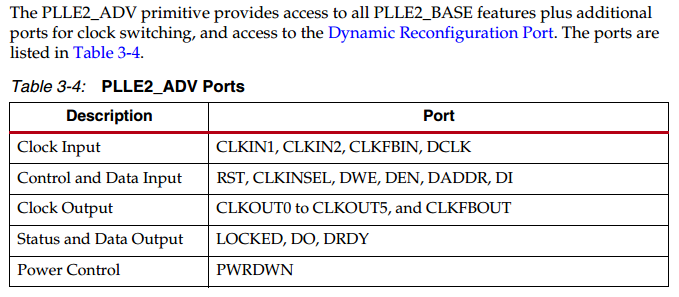

4.源语调用

MMCM与PLL的更多相关文章

- mmcm 和pll

这个2个有什么区别啊 mmcm 和pll? 1.DCM实际上就是一个DLL,可以对输入时钟进行相位移动,补偿,产生倍频和分频时钟,但是5以及以后的产品不用了.2.PLL相对于DCM,除了不能相移时钟 ...

- DCM、PLL、PMCD、MMCM相关

摘自网上 : http://xilinx.eetop.cn/viewnews-1482 The DCM is a Digital Clock Manager - at its heart it is ...

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- Vivado Design Suite用户指南之约束的使用第二部分(约束方法论)

Constraints Methodology(约束方法论) 关于约束方法论 设计约束定义了编译流程必须满足的要求,以使设计在板上起作用. 并非所有步骤都使用所有约束在编译流程中. 例如,物理约束仅在 ...

- 对FPGA的时钟资源理解(更新中)

7系列FPGA中包含了多达24个CMT(时钟管理单元)(实际上V7常见只有20个),MMCM和PLL均为时钟综合器,对外部输入时钟.内部时钟进行处理,生成需要的低抖动时钟.PLL是MMCM的功能子集, ...

- Xilinx FPGA复位逻辑处理小结(转)

Xilinx FPGA复位逻辑处理小结 1. 为什么要复位呢? (1)FPGA上电的时候对设计进行初始化: (2)使用一个外部管脚来实现全局复位,复位作为一个同步信号将所有存储单元设置为一个已知的状态 ...

- FPGA基础学习(9) -- 复位设计

目录 1. 常见问题 2. 常见的复位方式 3. 合理的复位设计 3.1 复位电平 3.2 异步复位同步化 3.3 恰到好处的复位 4. 补充 4.1 所谓的上电初始化 参考文献 一开始接触到FPGA ...

- Xilinx FPGA的专用时钟引脚及时钟资源相关

主要参考了https://www.eefocus.com/liu1teng/blog/12-02/237897_4533d.html .Xilinx UG471.UG472以及Xilinx Forum ...

- vivado下创建基本时序周期约束

创建基本时钟周期约束.(验证我们的设计能否在期望的频率上运行) (学习记录,晚一点会做实验传上来的.) 时钟基本概念:https://blog.csdn.net/wordwarwordwar/arti ...

随机推荐

- [学习日志]2018-11-18 主要: idea更改java版本

idea更改java版本 问题: 解决办法:

- foreach遍历数组、数组的转置与方阵的迹

public class Copy1 { public static void main(String[] args) { array1(); //如果不初始化元素,默认为0 int [][] a = ...

- Python根据路径名称获取文件的名称以及所在的路径

大神一看题目就知道用python中的string.split('\'),记得之前处理大量的文件的时候,有时候有几十万的文本文件,经常会读取获取名称,并且保存为名字一样的另外一种格式的文件 其实pyth ...

- Java中double转BigDecimal的注意事项

先上结论:不要直接用double变量作为构造BigDecimal的参数! 线上有这么一段Java代码逻辑: 1,接口传来一个JSON串,里面有个数字:57.3. 2,解析JSON并把这个数字保存在一个 ...

- C语言--成绩汇总(5班)

一.成绩列表 第0周成绩:[http://www.cnblogs.com/ranh941/p/7587567.html] 第1周成绩:[http://www.cnblogs.com/ranh941/p ...

- 2018.4.3 配置AD服务器步骤

net ads命令表 配置AD服务器步骤:1. 安装rpm依赖包yum -y install pam_krb5* krb5-libs* krb5-workstation* krb5-devel* kr ...

- linux下使用小票打印

linux下使用小票打印 打印机: Xprinter XP-58IIH指令支持: ESC/POS接口: USB, 蓝牙 Linux系统: Centos7 蓝牙配对很快, 配对好后就是连接状态. 但很快 ...

- 简单了解version control

1.什么是版本控制: 版本控制是指对软件开发过程中各种程序代码.配置文件及说明文档等文件变更的管理,是软件管理的核心思想之一 2.版本控制简述 版本控制最主要的功能就是追踪文件的变更.它将什么时候.什 ...

- 《DSP using MATLAB》Problem 6.24

代码: %% ++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++ %% Output In ...

- 【shell编程】之基础知识-文件包含

和其他语言一样,Shell 也可以包含外部脚本.这样可以很方便的封装一些公用的代码作为一个独立的文件. Shell 文件包含的语法格式如下: . filename # 注意点号(.)和文件名中间有一空 ...