(数字IC)低功耗设计入门(六)——门级电路低功耗设计优化

三、门级电路低功耗设计优化

(1)门级电路的功耗优化综述

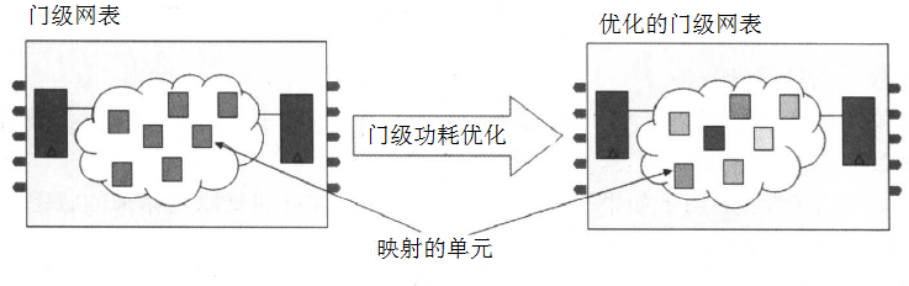

门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)是从已经映射的门级网表开始,对设计进行功耗的优化以满足功耗的约束,同时设计保持其性能,即满足设计规则和时序的要求。功耗优化前的设计是已经映射到工艺库的电路,如下图所示:

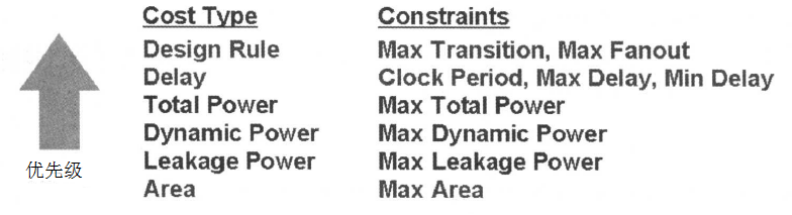

门级电路的功耗优化包括了设计总功耗,动态功耗以及漏电功耗的优化。对设计做优化时,优化的优先次序如下:

由此我们可以找到, 优化时,所产生的电路首先要满足设计规则的要求,然后满足延迟(时序)约束的要求,在满足时序性能要求的基础上,进行总功耗的优化,再进行动态功耗的优化和漏电功耗的优化,最后对面积进行优化。

优化时先满足更高级优先权的约束。进行低级优先权约束的优化不能以牺牲更高优先权的约束为代价。功耗的优化不能降低设计的时序。为了有效地进行功耗优化,需要设计中有正的时间冗余(timing slacks)。功耗的减少以时序路径的正时间冗余作为交换,即功耗优化时会减少时序路径上的正的时间冗余。因此,设计中正的时间冗余越多,就越有潜力降低功耗。

通过上面的描述,对门级功耗优化有了一下了解之后,这里先介绍一下静态功耗优化的方法——多阈值电压设计,然后介绍基于EDA工具的动态功耗的优化,接着介绍总体功耗的优化;在最后介绍一种常用的门级低功耗的方法——电源门控。电源门控我放在明天发表,今天的内容主要就是围绕静态、动态、总功耗来写。

(2)多阈值电压设计

①多阈值电压设计原理

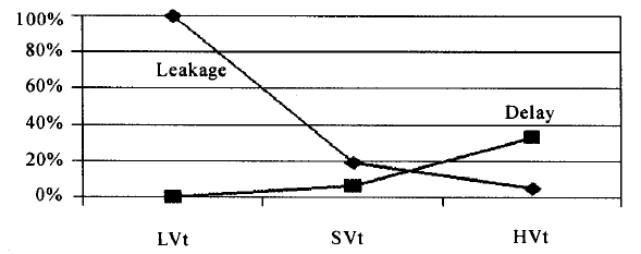

由于半导体工艺越来越先进,半导体器件的几何尺寸越来越小,器件中的晶体管(门)数越来越多,器件的供电电压越来越低,单元门的阈值电压越来越低。由于单位面积中的单元门越来越多,功耗密度高,器件的功耗大。因此,设计时,我们要对功耗进行优化和管理。在90nm或以下的工艺,静态功耗要占整个设计功耗的20%以上。因此,使用超深亚微米工艺时,除了要降低动态功耗,还要降低静态功耗。在超深亚微米工艺,单元门的阈值电压和漏电功耗(静态功耗)有如下图所示的关系:

由图可见,阈值电压Vt以指数关系影响着漏电功耗。阈值电压Vt与漏电功耗和单元门延迟有如下关系:

阈值电压Vt越高的单元,它的漏电功耗越低,但门延迟越长,也就是速度慢;

阈值电压Vt越低的单元,它的漏电功耗越高,但门延迟越短,也就是速度快。

我们可以利用多阈值电压工艺库的这种特点,进行漏电功耗的优化,设计静态功耗低性能高的电路。

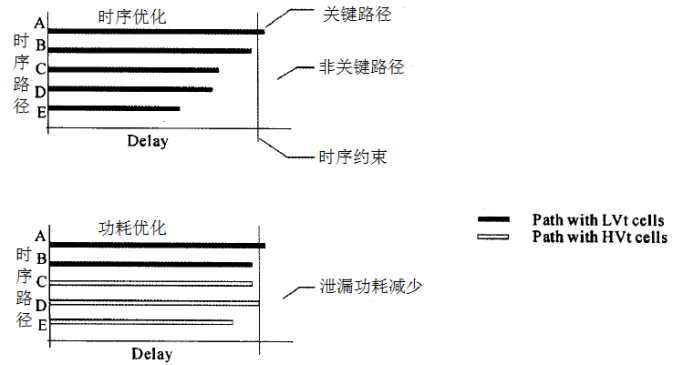

一般的设计中,一个时序路径组((timing path group)有多条时序路径,延迟最大的路径称为关键路径。根据多阈值电压单元的特点,为了满足时序的要求,关键路径中使用低阈值电压的单元(low Vt cells),以减少单元门的延迟,改善路径的时序。而为了减少静态功耗,在非关键路径中使用高阈值电压的单元(high Vt cells),以降低静态功耗。因此,使用多阈值电压的工艺库,我们可以设计出低静态功耗和高性能的设计。上面的描述如下图所示:

②门级网表/RTL代码的多阈值电压设计

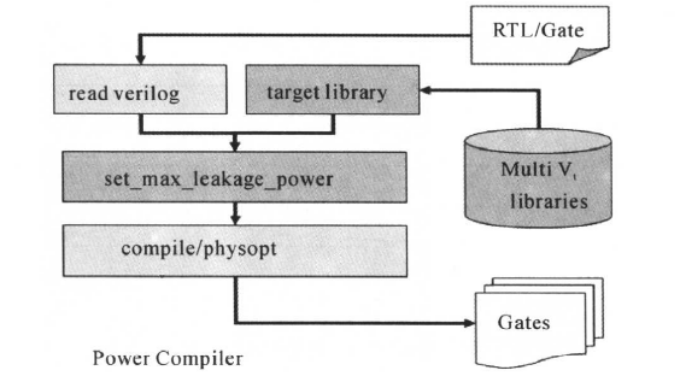

多阈值电压设计可以在门级网表或者RTL代码的时候就进行,也可以在后面布线后进行。门级网表/RTL代码的多阈值电压设计(或者说是静态功耗优化)流程如下所示:

一个对应的示例脚本如下所示:

set target_library "hvt.db svt.db lvt.db"

······

read_verilog mydesign.v

current_design top

source myconstraint.tcl

······

set_max_leakage -power 0mw

compile

······

与以前的脚本不同,设置target_library时,我们用了多个库。上列中,目标库设置为 "hvt.db svt.db lvt.db"脚本中使用set_max_leakage_power命令为电路设置静态功耗的约束。在运行compile命令时,Power Compiler将根据时序和静态功耗的约束,在目标库选择合适的单元,在满足时序约束的前提下,尽量使用Svt或Hvt单元,使优化出的设计性能高,静态功耗低。

PS:如果在Physical Compiler工具(现在我们使用DC的拓扑模式)里做漏电功耗优化时,我们可以保留一点正的时间冗余(positive slack),使电路不会在极限的时序下工作.这些时间冗余量也可被后面其他的优化算法所使用。设置时间冗余的命令如下:

set physopt_power_critical_range 时间量

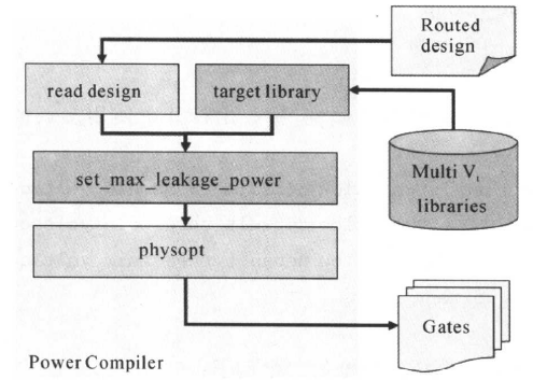

③布线后的多阈值电压设计

上面是门级网表/RTL代码的多阈值电压设计,下面简单介绍布线后的多阈值电压设计,流程如下图所示:

相应的一个示例脚本如下所示:

set target_library "hvt.db svt.db lvt.db"

read_verilog routed_design.v

current_design top

source top.sdc

······

set_max_leakage -power 0mw

physopt -preserve_footprint -only_power_recovery -post_route -incremental

physopt命令中使用了“-poat_route”的选项,特别用于进行布线后的漏电功耗的优化。优化时,单元的外形名称(footprint)保留下来,原有的布线保持不变。

④多阈值电压设计与多阈值库的报告

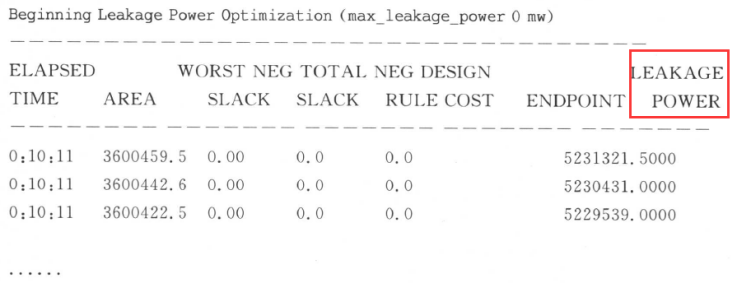

进行漏电功耗的优化时,Power Compile将报告如下的漏电优化的信息:

LEAKAGE POWER的列(Column)展出了内部优化的漏电成本值。它和报告出来的漏电功耗可能不一样。我们用“report_power”命令得到功耗的准确的报告。

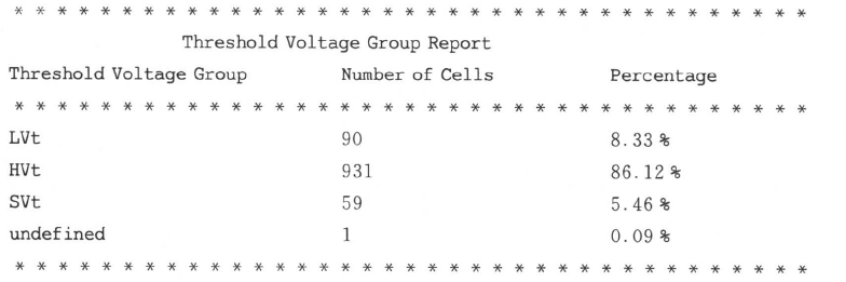

======================================================================

我们现在来看一下多阈值库。多阈值库定义了两个属性,一个为库属性:default_threshold_voltage_group,另一个为单独库单元的属性:threshold_voltage_group。然后报告多阈值电压组的命令是:report_threshold_voltage_group.我们可以使用多阈值库的这两个属性,报告出设计中使用多域值库单元的比例,一个示例的脚本如下所示:

set_attr -type string lvt.db:slow default_threshold_voltage_group LVt

set_attr -type string svt.db:slow default_threshold_voltage_group SVt

set_attr -type string hvt.db:slow default_threshold_voltage-group HVt

report_threshold_voltage_group

报告得到的结果如下所示:

(3)基于EDA工具的动态功耗优化

前面介绍了静态功耗的优化,下面介绍动态功耗的优化。动态功耗优化通常在做完时序优化后进行。动态功耗优化时,需要提供电路的开关行为,工具根据每个节点的翻转率,来优化整个电路的动态功耗。用compile/physopt命令可以同时对时序和功耗做优化。设置动态功耗的命令为:

set_max_dynamic_power xxmw.(一般设置为0)

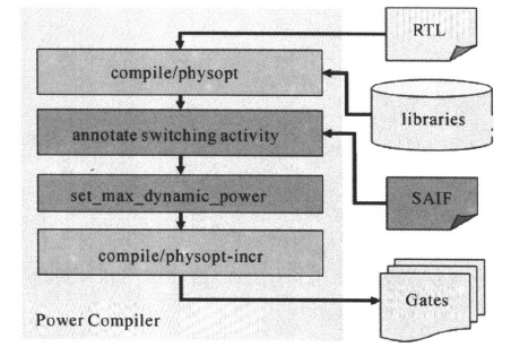

动态功耗优化的流程如下所示:

一个对应的示例脚本如下所示:

read_verilog top.v

source constraints.tcl

set target_library "tech.db"

compile

read_saif

set_ max_dynamic_power 0 mw

compile -inc

动态功耗的优化的实现如上面所示。优化过程用了很多技术比如插入缓冲器、相位分配之类的。由于这些都是power compiler在背后自动实现(或者说是进行低功耗优化时工具使用的原理),不需要我们进行设置,因此这里不进行介绍。

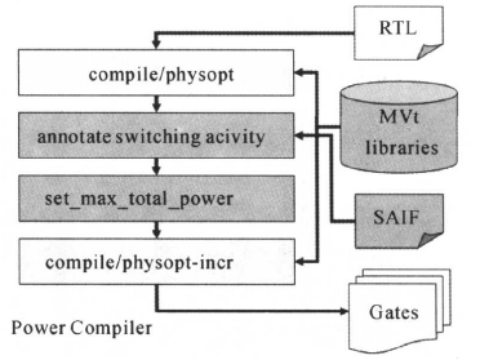

(4)总体功耗优化

前面分别介绍了静态功耗和动态功耗的优化方法。我们可以把它们结合在一起,进行整个设计总功耗的优化。总功耗是动态功耗和静态功耗的和,总功耗的优先级比动态功耗和静态功耗高。总功耗优化时,工具尽量减少动态功耗和静态功耗的和。优化时如果减少了漏电功耗增加了动态功耗,但它们的和减少了,优化是有效的。反之亦然。我们可以通过设置开关,使动态功耗优化和静态功耗优化用不同的努力级别(effort levels)和权重(weights)进行优化。

总功耗的优化流程如下图所示:

一个对应的示例脚本如下所示:

read_verilog top.v

source constraints.tcl

set target_library "hvt.db svt.db lvt.db"

······

compile

read_saif

set_max_total_power 0 mw -leakage_weight 30

compile -inc

······

脚本中,target_library设置为多阈值电压的库,用于做静态功耗的优化。读入含有开关行为的saif文件,用于约束动态功耗的优化。在设置总功耗的约束时,我们可以在set_max_total_power命令中使用静态或/和动态功耗权重(weight)的选项,使工具在优化时,偏重于静态或动态功耗。假设P、Pd和Pl分别为总功耗、动态功耗和静态功耗,Wd和Wl分别为动态功耗和静态功耗的权重,则

总功耗P = (Wd*Pd+Wl*P1)/Wd

我们可以在DC或PC中设定只对功耗做优化。这时候,工具仅优化设计的功耗,而不会对更高优先级的约束做任何的优化和修正设计规则DRC违例。但是这种优化也不会使设计的更高优先级约束的性能变差和引起DRC违例。这种优化的优点在于运行时间较短,可用于优化设计的动态功耗、静态功耗和总功耗。在DC和PC中,只能以增量编辑的形式工作。

PC中只对功耗做优化的命令如下:

set_max_total -power 0 mw

physopt -only_power_recovery

DC中只对功耗做优化的命令如下(由于现在PC在DC中,因此下面的脚本更常用):

set compile_power_opto_only true

set_max_leakage_power 0 mw

compile -inc

今天就先介绍到这里,明天将介绍门控电源的内容。

(数字IC)低功耗设计入门(六)——门级电路低功耗设计优化的更多相关文章

- (数字IC)低功耗设计入门(七)——门级电路低功耗设计优化(续)

前面讲解了门级功耗的优化方法,包括静动态和总体的功耗.现在来记录一下门级层次(有点书也说是在系统级)常用的一种低功耗方法--电源门控. ①电源门控概述与原理 电源门控是指芯片中某个区域的供电电源被关掉 ...

- (数字IC)低功耗设计入门(八)——物理级低功耗设计&to be continued?

前面学习了从系统级到门级的低功耗设计,现在简单地了解了一下物理级设计.由于物理级的低功耗设计与后端有关了,这里就不详细学习了.这里主要是学习了一些基本原则,在物理级,进行低功耗设计的基本原则是: ...

- (数字IC)低功耗设计入门(二)——功耗的分析

前面学习了进行低功耗的目的个功耗的构成,今天就来分享一下功耗的分析.由于是面向数字IC前端设计的学习,所以这里的功耗分析是基于DC中的power compiler工具:更精确的功耗分析可以采用PT,关 ...

- VerilogHDL概述与数字IC设计流程学习笔记

一.HDL的概念和特征 HDL,Hard Discrimination Language的缩写,翻译过来就是硬件描述语言.那么什么是硬件描述语言呢?为什么不叫硬件设计语言呢?硬件描述语言,顾名思义就是 ...

- 数字IC笔试题-芯源

前言 由于最近开始找数字IC的工作,所以准备多练笔试题,下面贴上芯源笔试题,来源微信公众号<数字IC打工人> 参考资源: 1. mu_guang_ 2. 李锐博恩 3. 长弓的坚持 4. ...

- (数字IC)低功耗设计入门(三)——系统与架构级

前面讲解了使用EDA工具(主要是power compiler)进行功耗分析的流程,这里我们将介绍在数字IC中进行低功耗设计的方法,同时也结合EDA工具(主要是Design Compiler)如何实现. ...

- (数字IC)低功耗设计入门(四)——RTL级低功耗设计

二.RTL级低功耗设计 前面介绍了系统级的低功耗设计,换句话说就是在系统级降低功耗可以考虑的方面.系统级的低功耗设计,主要是由系统级设计.具有丰富经验的人员实现,虽然还轮不到我们设计,我们了解一下还是 ...

- (数字IC)低功耗设计入门(五)——RTL级低功耗设计(续)

二.RTL级低功耗设计(续) 前面一篇博文我记录了操作数隔离等低功耗设计,这里就主要介绍一下使用门控时钟进行低功耗设计. (4)门控时钟 门控时钟在我的第一篇博客中有简单的描述,这里就进行比较详细的描 ...

- (数字IC)低功耗设计入门(一)

低功耗设计这个专题整理了好久,有一个月了,有图有证据: 然而最近一直有些烦心事.郁闷事,拖延了一下,虽然现在还是有点烦,但是还是先发表了吧.下面我们就来聊聊低功耗设计吧,由于文章比较长,因此我就不一次 ...

随机推荐

- 设计模式的征途—3.工厂方法(Factory Method)模式

上一篇的简单工厂模式虽然简单,但是存在一个很严重的问题:当系统中需要引入新产品时,由于静态工厂方法通过所传入参数的不同来创建不同的产品,这必定要修改工厂类的源代码,将违背开闭原则.如何实现新增新产品而 ...

- Doctype 文档类型,标准模式,混杂模式

HTML4.01和XHTML1.0 基于 SGML,支持DTD声明,HTML5不是,但是需要 doctype 来规范浏览器的行为. 标准模式是指,DTD声明定义了标准文档的类型后,浏览器按W3C标准解 ...

- 【Tomcat源码学习】-1.概述

Tomcat是用java语言开发的一个Web服务器,最近花了差不多两周时间对Tomcat 9.0源码进行了一遍学习,由于知识储备有限,也只是理解了一个大概,下面就由我来给大家分享一下我对Tomcat的 ...

- css3 新属性

一 选择器1 兄弟选择器 0 以第一个选择器开始,往后找满足条件的兄弟节点 class~class() <-- lorem+数字 -tab --> 可以输出默认文字2 属性选择器 标签[a ...

- 【Android N_启示录】

[啰嗦~]自从接触Android以来,大概也有3年时间,基本是跟着项目走,做过的东西不算多也不算少,从当初做上层应用到系统级应用,再到Framework,以及后来接触功耗.性能优化等需求.给我的感觉就 ...

- LinkedList 学习笔记

先摆上JDK1.8中hashMap的类注释:我翻译了一下 /** * Doubly-linked list implementation of the {@code List} and {@code ...

- 自定义TextView跑马灯

本篇主要介绍TextView的可控制跑马灯效果实现. Android自带的TextView添加几个属性就可以实现跑马灯效果,大概是这样 android:ellipsize="marquee& ...

- 【Java SE】如何用Java实现冒泡排序

摘要: 作为一名Java开发工程师,手头如果不会几个常见的排序算法,怎么可能经过笔试题这一关呢.据我所知,许多大型的公司的笔试题都有排序题,那我们先从最简单的排序:冒泡排序开始,以后几篇博客将继续更新 ...

- jquery ajax自定义分页组件(jquery.loehpagerv1.0)原创

简单的两个步骤截可调用 <script src="<%=basePath%>/resources/js/jquery-1.7.1.min.js"></ ...

- java入门基础

什么是java? java是一门编程语言 编程语言有很多种 你比如 C语言 等等 为什么学习java呢! 因为你要和计算机交互 当然了你用汉语跟她说她听不懂 所以你要学习编程语言 那么额咱们的ja ...