PCB设计AD规则设置(按照嘉立创设置)

本文转载自https://blog.csdn.net/subtitle_/article/details/121648972

官方参考https://www.jlc.com/portal/vtechnology.html

前言

视图->切换单位(快捷键q或者Ctrl+q)可以切换mm和mil单位。方便下面规则设置的单位转换。

按照嘉立创的相关加工能力进行设置。

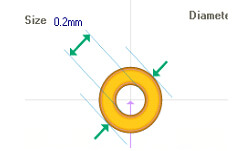

1.Hole Size(钻孔孔径)

嘉立创要求钻孔孔径在0.2-6.3mm,并给了公差(如下图给出了钻孔孔径和公差)

| 项目 | 加工能力 | 工艺详解 | 图解 |

|---|---|---|---|

| 钻孔孔径(机械钻) | 0.2~6.3mm | 最小孔径0.2mm,最大孔径6.3mm,如果大于6.3mm工厂要另行处理。机械钻头规格为0.05mm为一阶,如0.2,0.3mm |  |

规则设置位置:Manufacturing->Hole Size,这里就改一下数值,最小设置为0.2mm,最大设置为6.3mm。

PS:0.2mm ≈ 7.874mil , 6.3mm ≈ 248.031mil

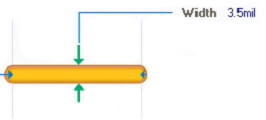

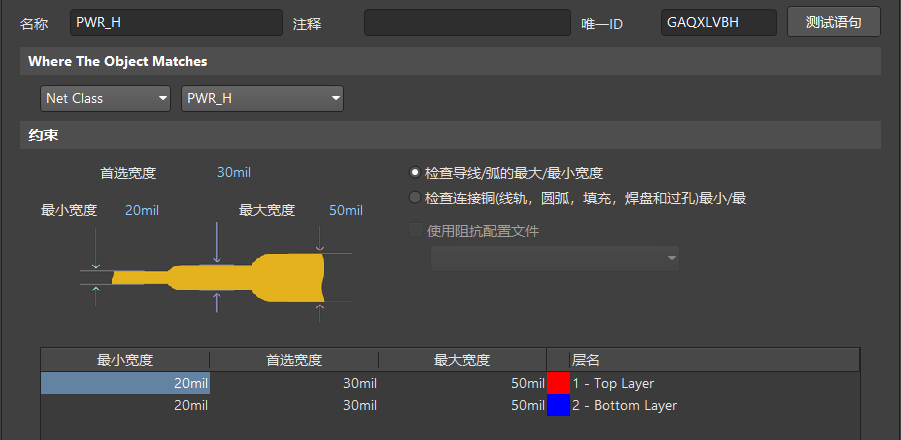

2.Width(线宽)

嘉立创要求线宽多层板最小为3.5mil,单双层板最小为5mil(如下图给出了线宽)

| 项目 | 加工能力 | 工艺详解 | 图解 |

|---|---|---|---|

| 线宽 | 3.5mil | 多层板3.5mil 单双面板5 mil (1OZ完成铜厚),2OZ完成铜厚最小线宽线隙8mil |

|

规则设置位置:Routing->Width,我目前只画过双层板,按我的设置如下,最小的线宽设置为10mil,首选线宽为20mil,最大线宽为100mil,这是信号线的(一般可以设置在10-20mil之间都没有问题),如果是电源线的话建议线宽要大一点了(因为电流比较大,一般可以设置为20-50mil)。

顺便补充一下,线宽的大小影响承载电流的多少,这个关系可以从下面这张表知道,根据线路的电流大小在工艺许可的范围内选择合适的线宽就可以了。

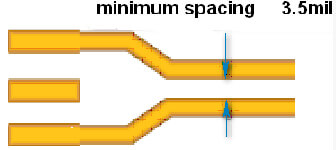

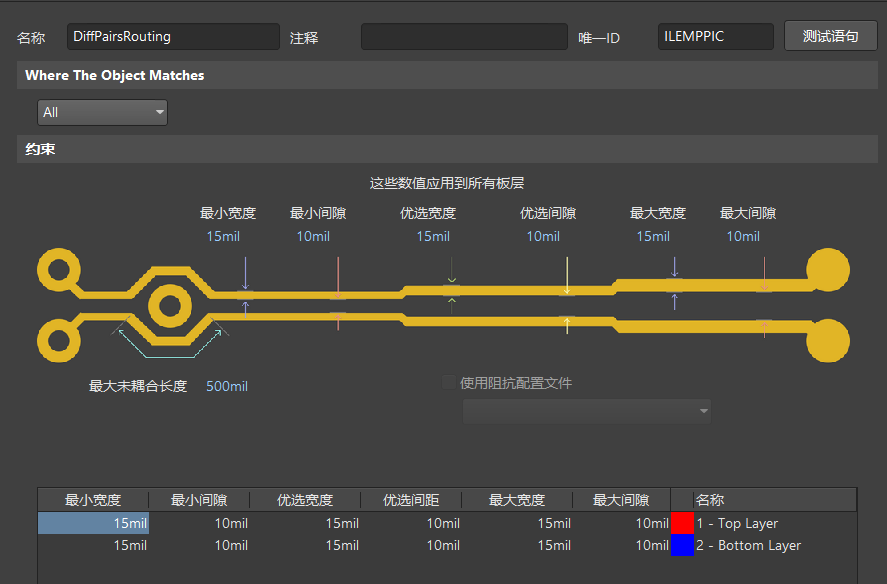

3.Diff Pair Routing(线隙)

嘉立创要求线隙多层板双层板最小为3.5mil,单双层板最小为5mil(如下图给出了线隙)

| 项目 | 加工能力 | 工艺详解 | 图解 |

|---|---|---|---|

| 线隙 | 3.5mil | 多层板3.5mil 单双面板5 mil (1OZ完成铜厚),2OZ完成铜厚最小线宽线隙8mil |

|

规则设置位置:Routing->Diff Pair Routing,我这里其实按的是默认设置没有改动(最小的线隙(间隙)设置为10mil)。

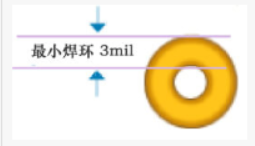

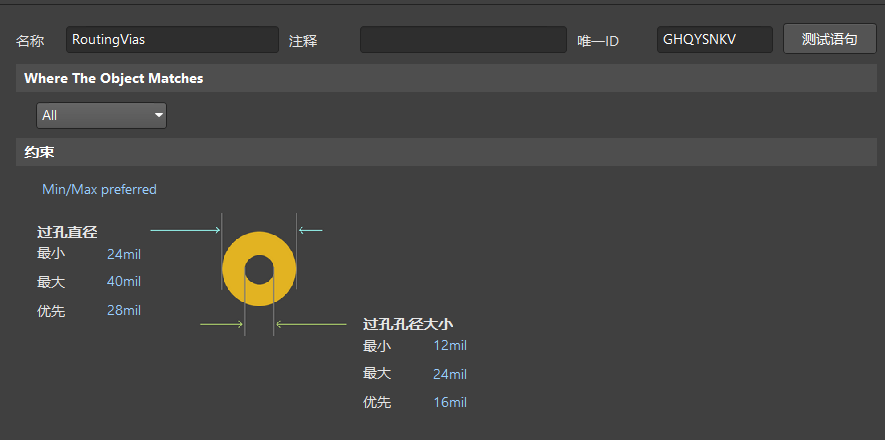

4.Routing Via Style(最小过孔内径及外径 & 过孔单边焊环)

嘉立创要求多层板最小内径0.2mm,最小外径0.4mm,最小内径0.3mm,最小外径0.5mm(如下图给出了最小过孔内径及外径)。过孔单边焊环3mil(参数是极限值)。

| 项目 | 加工能力 | 工艺详解 | 图解 |

|---|---|---|---|

| 最小过孔内径 及外径 | 内径(hole)最小0.2mm,外径(diameter)最小0.4mm | 多层板最小内径0.2mm,最小外径为0.4mm,双面板最小内径0.3mm,最小外径0.5mm |

|

| 过孔单边焊环 | 3mil | 参数为极限值,尽量大于此参数 |  |

规则设置位置:Routing->Routing Via Style,我是按mil为单位进行设置的,且为了满足过孔单边焊环的要求,我的具体数值如图,过孔孔径最小12mil(0.305mm),最大24mil(0.61mm),优先选择16mil(0.406mm),过孔外径最小25mil(0.635mm),最大40mil(1.016mm),优先选择28mil(0.711mm)。

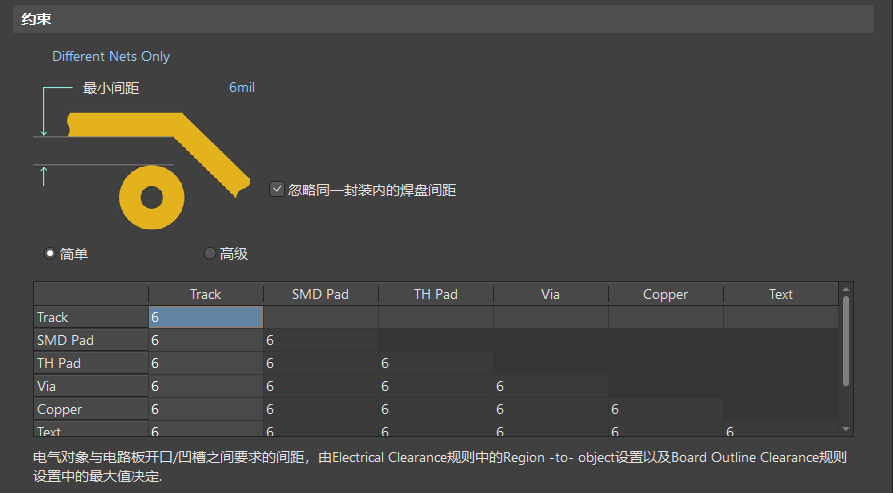

5.Clearance(焊盘边缘到线距离)

嘉立创要求大于5mil(如下图给出了焊盘边缘到线的距离)

| 项目 | 加工能力 | 工艺详解 | 图解 |

|---|---|---|---|

| 焊盘边缘到线距离 | 5mil | 参数为极限值,尽量大于此参数 |  |

规则设置位置:Electrical->Clearance,5mil是极限值,这里设置的大一点,我设置为6mil。

6.最小字符宽

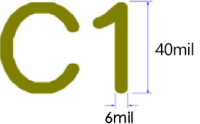

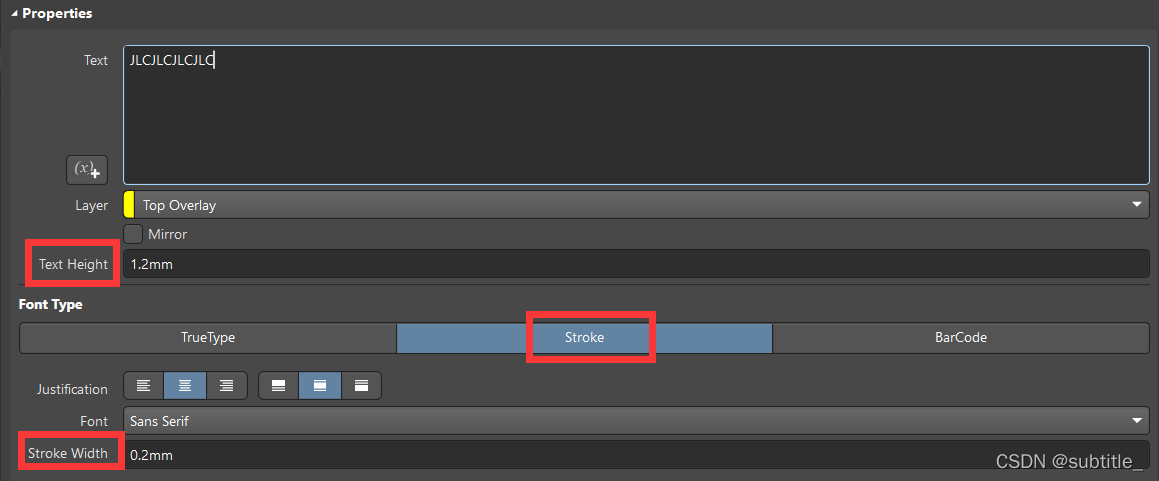

嘉立创要求字符线宽6mil,字符高32mil(如下图给出了焊盘边缘到线的距离)。

| 项目 | 加工能力 | 工艺详解 | 图解 |

|---|---|---|---|

| 最小字符宽 | 线宽6mil,字符高40mil | 参数为极限值,尽量大于此参数 |  |

在规则里不能找到这个选项,但是可以在放置字符的时候按Tab键进行修改,我这边一般选择的是Stroke字体,设置的是高度为1.2mm(47.244mil),宽度为0.2mm(7.874mil)。

7.其他

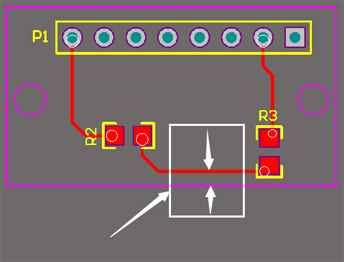

- 走线和焊盘距离板边的距离应该大于等于0.3mil,防止切割的时候碰到焊盘和走线。

| 项目 | 加工能力 | 工艺详解 | 图解 |

|---|---|---|---|

| 单片出货:走线和焊盘距板边距离 | ≥0.3mm | 否则可能涉及到板内的线路及焊盘 |  |

设计钻孔的孔径要比元器件至少大

0.1mm以上,要不然插不进去。插件管脚是方的,做封装时不能直接用长和宽绘制,正确的应该时用管脚的对角线加上公差,封装还是至少要比元器件大

0.1mm以上。

总结一下,以后可以回来查看!

PCB设计AD规则设置(按照嘉立创设置)的更多相关文章

- PCB设计常见规则及基本原则

一.PCB基础知识 1.全称:印制电路板或者印制线路板 2.分类 材质分类:硬板(Rigid PCB).软板FPC(Flexible PCB).软硬结合板(Rigid-Flex PCB).HDI板(含 ...

- AD小白如何发板厂制板--导出gerber文件和钻孔文件+嘉立创下单教程

AD如何发工程制板子? 方式1,发PCB源文件给板厂 方式2,发一些工艺文件给板厂,这样就无须泄漏你的PCB源文件了,一个硬件工程师必须要掌握方式2. 方式2要做的就是导出gerber文件和钻孔文件, ...

- PCB各层介绍及AD软件画PCB时的规则

好久没画过板了,最近因为工作关系,硬件软件全部得自己来,不得不重新打开闲置很久的AltiumDesigner.以前做过点乱七八糟的笔记,本来想回头翻看一下,结果哪儿也找不到,估计已经被不小心删掉了. ...

- 嘉立创制作PCB流程

现在做板子基本上是选择嘉立创和捷配,今天看一下嘉立创如何下PCB和STM贴片单,改天再写一下捷配的下单 我喜欢用下单助手,比较方便 注意需要把自己的板子的PCB文件用压缩软件生成压缩包文件,名字自己取 ...

- J20航模遥控器开源项目系列教程(四)PCB打印 | 嘉立创PCB下单教程,5元顺丰包邮解君愁!

我们的开源宗旨:自由 协调 开放 合作 共享 拥抱开源,丰富国内开源生态,开展多人运动,欢迎加入我们哈~ 和一群志同道合的人,做自己所热爱的事! 项目开源地址:https://github.com/J ...

- JLC PCB 嘉立创自动确认生产稿,不讲武德?耗子尾汁!!!

首先,开局一张图,嘉立创又不做人的一天.嘉立创不讲武德,耗子尾汁!!! 之前下单,勾选了确定生产稿和不加客编,结果生产稿出来还是给我加了客编.那我出10元的意思何在?让我自己花3元看我花的10元有没有 ...

- PCB设计检查表

PCB设计检查表 一.确保PCB网表与原理图描述的网表一致 二.布局大致完成后需检查 外形尺寸 确认外形图是最新的 确认外形图已考虑了禁止布线区.传送边.挡条边.拼板等问题 确认PCB 模板是最新的 ...

- PCB设计备忘录

在PCB设计过程中,常常有很多细节只有在实践中才能体会到其重要性,本人记性不好,索性把相关的注意点记录下来,也顺便希望能够给读者朋友们一些帮助. 接插件以及连接器比较常用的针脚之间间距有2.54mm/ ...

- 原理图及PCB设计

原理图以及元件的绘制1. 画数据总线时,需要给总线一个Net Label,例如:databus[0..7],并且还需要在每个入口和出口处设置一致的标号.2. ERC 电气规则检查,Electronic ...

- 十条最有效的PCB设计黄金法则

十条最有效的PCB设计黄金法则 尽管目前半导体集成度越来越高,许多应用也都有随时可用的片上系统,同时许多功能强大且开箱即用的开发板也越来越可轻松获取,但许多使用案例中电子产品的应用仍然需要使用定制PC ...

随机推荐

- Element——前端样式美化

Element 简介 Element 快速入门 https://element.eleme.cn/#/zh-CN/component/button Element 布局 ht ...

- hive操作 -- zeppelin安装及配置

当时写hive用的是zeppelin,这个工具可以直接在页面上写sql语句,操作服务器上的hive库,还挺方便的 通过zeppelin实现hive的查询结果的可视化 启动过程中会报错:User: to ...

- 北京智和信通受邀出席2022IT运维大会,荣获“2022智能运维星耀榜最具影响力企业”

9月8日,由IT运维网.<网络安全和信息化>杂志社联合主办的"2022(第十三届)IT运维大会"在北京辽宁大厦成功举办.大会以"智慧先行,运维有术" ...

- 《Vue.js 设计与实现》读书笔记 - 第7章、渲染器的设计

第7章.渲染器的设计 7.1 渲染器与响应系统的结合 渲染器需要有跨平台的能力. 在浏览器端会渲染为真实的 DOM 元素. const { effect, ref } = VueReactivity ...

- 【转】sqlplus/RMAN/lsnrctl 等工具连接缓慢

AIX上sqlplus /as sysdba rman target / 或者lsnrctl start时或者通过sqlplus system/oracle@orcl这样通过监听连接等方式来登陆时非常 ...

- 云原生爱好者周刊:使用 AWS 开源的 FireCracker 来创建和管理 K8s 集群

开源项目推荐 KubeFire 这个项目比较有创意,它使用 AWS 开源的轻量级虚拟化项目 FireCracker 来创建和管理 Kubernetes 集群,摒弃了传统的 qcow2 和 vhd 等虚 ...

- 极客时间「大师课·深度剖析 RocketMQ5.0」上线啦,欢迎免费领取!

从初代开源消息队列崛起,到 PC 互联网.移动互联网爆发式发展,再如今 IoT.云计算.云原生引领了新的技术趋势,消息中间件的发展已经走过了 30 多个年头. 目前,消息中间件在国内许多行业的关键应用 ...

- 【FAQ】HarmonyOS SDK 闭源开放能力 —IAP Kit(3)

1.问题描述: 已经购买订阅型物品,未调用finishPurchase接口, 重新购买该物品,createPurchase接口返回的是001860001错误:System internal error ...

- 狂神说-Docker基础-学习笔记-07 容器数据卷

狂神说-Docker基础-学习笔记-07 容器数据卷 视频地址:https://www.bilibili.com/video/BV1og4y1q7M4?p=21 什么是容器数据卷 运行时数据都在容器中 ...

- LeetCode题目练习记录 _数组和链表01 _20211007

LeetCode题目练习记录 _数组和链表01 _20211007 26. 删除有序数组中的重复项 难度简单2247 给你一个有序数组 nums ,请你原地 删除重复出现的元素,使每个元素 只出现一次 ...