HDLbits——Lfsr32

//Build a 32-bit Galois LFSR with taps at bit positions 32, 22, 2, and 1.

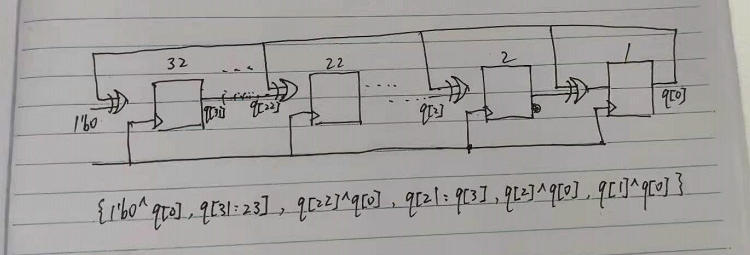

草图

verilog描述

module top_module(

input clk,

input reset, // Active-high synchronous reset to 32'h1

output reg [31:0] q

);

always @(posedge clk) begin

if(reset)begin

q <= 32'h1;

end

else begin

q <= {1'b0^q[0],q[31:23],q[22]^q[0],q[21:3],q[2]^q[0],q[1]^q[0]};

end

end

endmodule

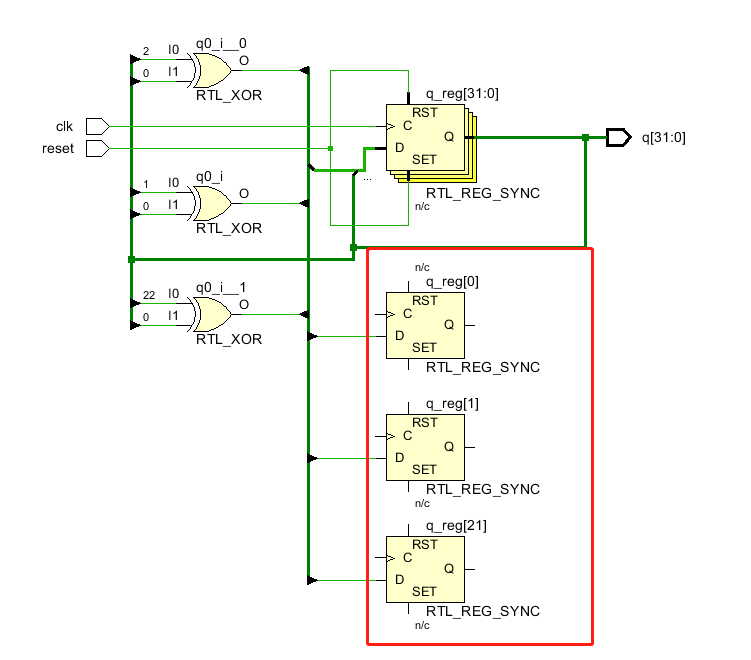

vivado下的RTL原理图:

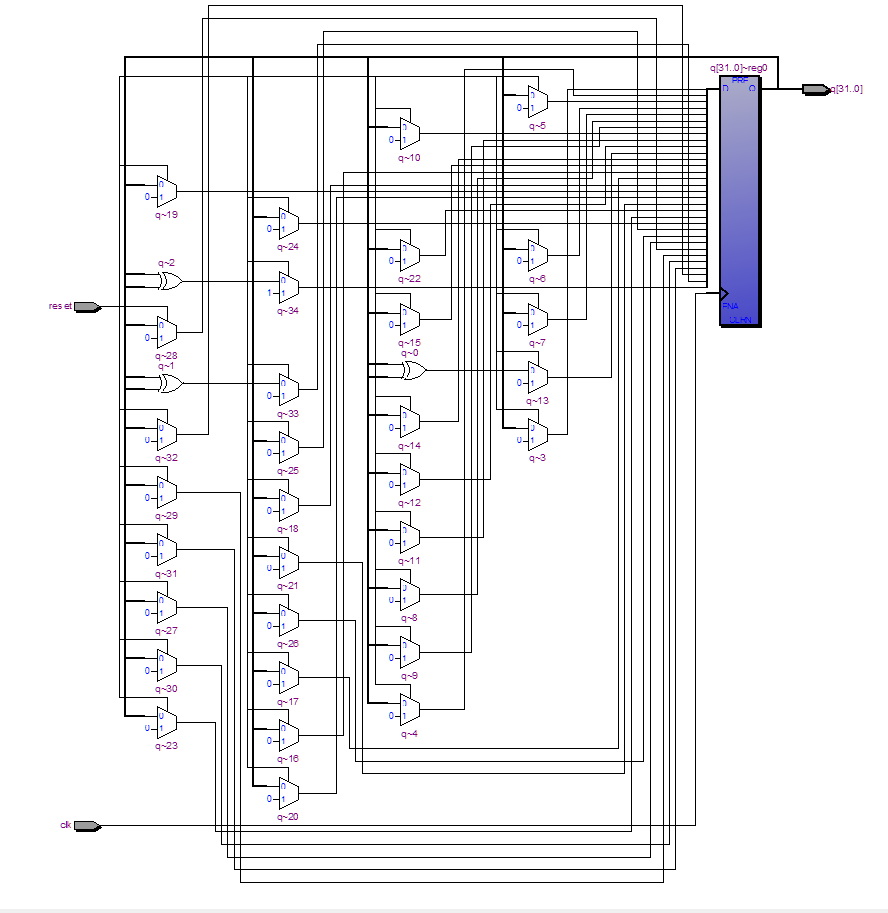

quartus下的RTL原理图:采用大量选择器

HDLbits——Lfsr32的更多相关文章

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- HDLBits答案——Circuits

1 Combinational Logic 1.1 Basic Gates 1.1.1 Exams/m2014 q4h module top_module ( input in, output out ...

- HDLBits答案——Verification: Writing Testbenches

1 clock module top_module ( ); reg clk; dut U1(.clk(clk)); initial begin clk = 0; end always begin # ...

- HDLBits答案——Verification: Reading Simulations

1 Finding bugs in code 1.1 Bugs mux2 module top_module ( input sel, input [7:0] a, input [7:0] b, ou ...

- HDLBits答案——Verilog Language

Verilog Language 1 Basics 1.1 Wire module top_module( input in, output out ); assign out = in; endmo ...

- HDLBits答案——Getting started

Getting started 1 Step one module top_module( output one ); // Insert your code here assign one = 1' ...

- verilog常见错误列表

Error/Warning 来源:https://hdlbits.01xz.net/wiki/ 题目: 1.Quartus Warning 10235: Warning (): Verilog HDL ...

- Verilog HDL

https://wenku.baidu.com/view/9943b7acf524ccbff1218463.html https://hdlbits.01xz.net/wiki/Main_Page h ...

- Verilog设计技巧实例及实现

Verilog设计技巧实例及实现 1 引言 最近在刷HDLBits的过程中学习了一些Verilog的设计技巧,在这里予以整理.部分操作可能降低代码的可读性和Debug的难度,请大家根据实际情况进行使用 ...

- 入行数字IC验证的一些建议

0x00 首先,推荐你看两本书,<"胡"说IC菜鸟工程师完美进阶>(pdf版本就行)本书介绍整个流程都有哪些岗位,充分了解IC行业的职业发展方向.<SoC设计方法 ...

随机推荐

- C# 报表接口样例,简单实用

//连接视图名称,视图在数据库写好<%@ WebHandler Language="C#" Class="GetwmsReport" %> usin ...

- 深入理解JVM - 自动内存管理

对于从事C.C++程序开发的开发人员来说,在内存管理领域,他们既是拥有最高权力的"皇帝",又是从事最基础工作的劳动人民--既拥有每一个对象的"所有权",又担负着 ...

- python日志logging配置

python日志logging配置 为了方便ELK收集日志,将日志打印成json格式 开发过程中,使用json格式不方便排查问题 本文章使用python的logging模块,一步步增加配置,来说明每个 ...

- 题解[CF1628F]A_Random_Code_Problem

题意 给定一个数组 \(a\),进行 \(k\) 次操作.第 \(i\) 操作等概率随机 \(a\) 中一个元素 \(a_x\),将这个元素的值加入答案,并使其减去 \(a_x\bmod i\) .问 ...

- python web自动化-文件上传-亲身实践

文件上传三种方式: (一)查看元素标签,如果是input,则可以参照文本框输入的形式进行文件上传 方法:和用户输入是一样的,使用send_keys 步骤:1.找到定位元素,2,输入文件路径 ele=d ...

- git 修改commit 备注

1.没有push 1.修改最后一次的提交备注 git commit --amend 输入 i 进行编辑模式,修改好以后 esc 退出编辑模式 :wq 保存并退出. 2.修改之前的备注 git reba ...

- js检测数组是否有重复的数据,

function(arr){ let hash={} for (const key in arr){ if(hash[arr[key]]){ return true } hash[arr[key]]= ...

- Vue.js的使用经验

Vue.js的使用经验 Vue.js的意义 解耦了视图与数据 可复用的组件 前端路由 状态管理 虚拟DOM Vue提供了很多实例属性与方法,都以$开头 $el可以访问挂载Vue实例的元素. $se ...

- 如何理解Vue中的组件?

Vue2.6已经更新了关于内容插槽和作用域插槽的API和用法,为了不误导大家,我把插槽的内容删除了.详情请看官网 2018-07-19更新: 更新作用域插槽的属性: scope -> slot- ...

- docker安装postgres并启用postgis扩展

镜像 查看所有镜像 docker images 可以直接拉取postgis镜像 docker pull postgis 也可以在已有镜像上安装postgres,再启用扩展: docker pull p ...