AXI4 STREAM DATA FIFO

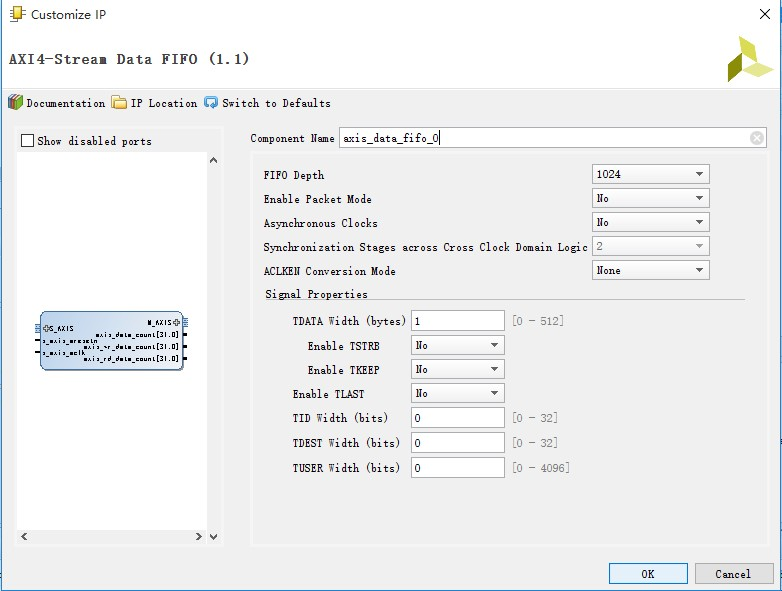

Component Name:

元件名字:该IP核生成后的模块名;

FIFO Depth:

FIFO深度:该设定为指定例化FIFO的深度。当FIFO的深度为16或者32时利用基于FIFO的LUTRAM,其他深度的FIFO将利用BLOCK RAM实现。

Enable Packet Mode:

使能包模式:设置为Yes将使能包模式。此项设定需要TLAST信号被使能。FIFO的操作在包模式下被修改为存储传送的数据,知道TLAST信号被断言(响应)。当TLAST信号被响应或者FIFO满了,存储的传送数据将被送至AXI4-Stream master interface。

Asynchronous Clocks:

异步时钟:如果设定了Yes,S_AXIS_ACLK和M_AXIS_ACLK被设定为与彼此异步,该IP将在异步模式进行操作。

Synchronization Stages across Cross Clock Domain Logic:

跨交叉时钟域逻辑的同步阶段:

当S_AXIS_ACLK和M_AXIS_ACLK是与彼此异步的,此项参数指定了用于跨时钟域逻辑的同步阶段的阶数。增加这个值可以增加设计的MTBF,但是会增加延迟时间和逻辑利用。参考the FIFO Generator Product Guide(PG075)获得该参数的更多信息。

ACLKEN Conversion Mode

ACLKEN转换模式:

这个下拉选项为ACLKEN信号的转换模式。当ACLKEN转换执行时会消耗额外的延迟和逻辑。这个选项有:

None - 这里没有ACLKEN信号关联于IP。

S AXIS Only - 一个S_AXIS_ACLKEN信号关联到S_AXIS_ACLK时钟信号和没M_AXIS_ACLKEN信号。

M AXIS Only - 一个M_AXIS_ACLKEN信号关联到M_AXIS_ACLK时钟信号和没有S_AXIS_ACLKEN信号。

S AXIS & M AXIS - 两边时钟都有 ACLKEN信号关联到他们。

Signal Properties:

信号特性:

当使用IP集成器是,Vivado IDE会自动计算这些参数的值。

TDATA Width(bytes):

TDATA位宽(字节为最小单位):

该参数指定了所有AXI4-Stream interfaces中的TDATA信号的位宽,以字节为最小单位。该参数为整数,在0到512之间。设为0将省略TDATA信号。如果TDATA信号被省略,TKEEP和TSTRB信号也会被省略。接口数据的位宽按bits计算,需要乘以8。

Enable TSTRB

使能TSTRB信号

如果设定为Yes,这个参数指定是否在所有AXI4-Stream interfaces使用可选的TSTRB信号。这个选项只能在TDATA Width(bytes)参数大于0时才可以使能。

Enable TKEEP

使能TKEEP信号

如果设定为Yes,这个参数指定是否在所有AXI4-Stream interfaces使用可选的TKEEP信号。这个选项只能在TDATA Width(bytes)参数大于0时才可以使能。

Enable TLAST:

使能TLAST:

如果设定为Yes,这个参数指定是否在所有AXI4-Stream interfaces使用可选的TLAST信号。对于TLAST信号要重点说明,因为在使用STREAM FIFO时TLAST的作用特别的重要。对于STREAM FIFO来说,TLAST信号的作用是指示一次传输数据流的最后一个数据,也指示着该数据流的结束。其会记录下TLAST信号的位置,及当其SLAVE接口(SFIFO的数据写入接口)的某一个数据写入的同时TLASET信号也为高的话,当MASTER接口(SFIFO的数据读出接口)读出该数据的同时也会将TLAST信号拉高。总结起来就是,进的数据有TLAST,该数据出的时候就会有TLAST。

TID Width(bits):

TID位宽(比特为单位):

如果该参数大于0,这个参数指定是否在所有的AXI4-Stream interfaces中使用TID信号。值大于0省略这个信号。

TDEST Width(bits):

TDEST位宽(bits):

如果该参数大于0,这个参数指定是否在所有的AXI4-Stream interfaces中使用TDEST信号。值大于0省略这个信号。

TUSER Width(bits):

TUSER 位宽(bits):

如果该参数大于0,这个参数指定是否在所有的AXI4-Stream interfaces中使用TDEST信号。值大于0省略这个信号。

这里重点说下Synchronization Stages across Cross Clock Domain Logic,这个参数的出现是由于在进行跨时钟域操作时,即FIFO的读写时钟异步时,在读时钟域与写时钟域进行数据交互时可能会存在亚稳态,而通过在数据交换节点插入连续的寄存器进行时钟同步,而这个参数的数值就是插入的同步寄存器的个数,或者叫做阶数。阶数越高,MTBF(Mean Time Between Failures,平均无故障时间)越大,则出现亚稳态的几率越小,但是同时也会增加信号传输的延迟和增加额外的逻辑资源。

还有一个参数Packet Mode,当开启整包发送模式后,FIFO会一直检测当前接收数据量,只有当数据量到达FIFO的深度时,即FIFO满的时候(在实际测试中发现当STREAM FIFO满的时候不会输出TLAST信号),或者是FIFO的SLAVE接口接收到TLAST信号时,该FIFO的MASTER接口才可以输出有效数据,及才会允许后级模块接收FIFO内数据。

在使用STREAM FIFO的应用中只应用到了TDATA、TVALID、TREADY以及TLAST信号,所以接下来对STREAM FIFO的功能说明只要是针对只是用以上信号的条件下的。

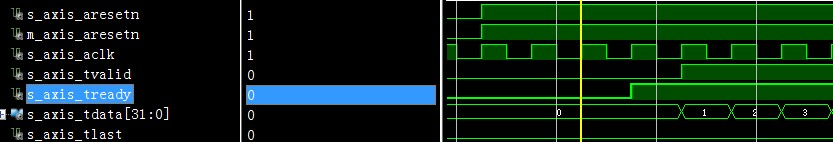

STREAM FIFO的复位信号为低有效,当复位信号拉高后的第三个时钟上升沿s_axis_tready信号会自动拉高,该fifo处于等待接收数据状态。

当STREAM FIFO的前端有数据需要发送时,在s_axis_tready为高时拉高s_axis_tvalid信号,在下个时钟上升沿,STREAM FIFO便开始收数。

当STREAM FIFO内部的数据达到fifo的深度时,在接收进最后一个数据的同时,s_axis_tready将会变为低,告诉前级fifo已满,不能在收数据了。其实S_axis_tready信号相当于普通FIFO的full与empty信号的综合体。

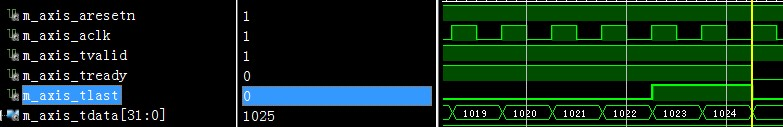

对STREAM FIFO 的MASTER接口为FIFO的数据输出接口。当STREAM FIFO接收到数据并传到MASTER接口上时,m_axis_tvalid便会拉高,由于使用的STREAM FIFO为异步时钟模式,数据写入时钟比数据读出时钟要快,而读数据计数器的刷新是在读数据时钟的上升沿,所以可以从图中看到读数据计数器的值是跳跃上升的。当FIFO的后端将m_axis_tready拉高时,MASTER接口便会将数据送出去。

最后再来观测下TLAST信号:

为了说明TLAST信号的传输特点,我们在SLAVE的写入数据时在数据1023 和数据1024的时候将s_axis_tlast拉高。然后打开MASTER接口将STREAM FIFO内部的数据读出。

从MASTER接口的数据流可以看出,将数据1023和数据1024读出的同时也会将m_axis_tlast信号拉高。

最后说明一下STREAM FIFO的Packet mode包模式,开启包模式必须是采用同步时钟,而且TLAST信号必须使用。

在包模式下,数据将是以包的单位,而包内数据的数量由TVALID、TREADY和TLAST信号控制,TVALID信号和TREADY信号一起为包数据的开始,TLAST信号为包数据的结束。当STREAM FIFO里面没有收到一包的数据时,FIFO的MASTER接口将处于关闭状态,即m_axis_tvalid将一直保持为低。当STREAM FIFO内部数据有至少一包及以上的数据时,MASTER接口将开启,m_axis_tvalid将会拉高,当后级将存的包数据取完之后,MASTER接口又将关闭,m_axis_tvalid将拉低,直到接收到下一包数据之后才会重新打开。

AXI4 STREAM DATA FIFO的更多相关文章

- 学习笔记20151211——AXI4 STREAM DATA FIFO

AXI4 STREAM DATA FIFO是输入输出接口均为AXIS接口的数据缓存器,和其他fifo一样是先进先出形式.可以在跨时钟域的应用中用于数据缓冲,避免亚稳态出现.支持数据的分割和数据拼接.在 ...

- Putting Apache Kafka To Use: A Practical Guide to Building a Stream Data Platform-part 1

转自: http://www.confluent.io/blog/stream-data-platform-1/ These days you hear a lot about "strea ...

- FunDA(4)- 数据流内容控制:Stream data element control

上节我们探讨了通过scalaz-stream-fs2来驱动一套数据处理流程,用fs2的Pipe类型来实现对数据流的逐行操作.本篇讨论准备在上节讨论的基础上对数据流的流动和元素操作进行优化完善.如数据流 ...

- Putting Apache Kafka To Use: A Practical Guide to Building a Stream Data Platform-part 2

转自: http://confluent.io/blog/stream-data-platform-2 http://www.infoq.com/cn/news/2015/03/ap ...

- 利用ZYNQ SOC快速打开算法验证通路(4)——AXI DMA使用解析及环路测试

一.AXI DMA介绍 本篇博文讲述AXI DMA的一些使用总结,硬件IP子系统搭建与SDK C代码封装参考米联客ZYNQ教程.若想让ZYNQ的PS与PL两部分高速数据传输,需要利用PS的HP(高性能 ...

- Bit error testing and training in double data rate (ddr) memory system

DDR PHY interface bit error testing and training is provided for Double Data Rate memory systems. An ...

- Why Apache Beam? A data Artisans perspective

https://cloud.google.com/dataflow/blog/dataflow-beam-and-spark-comparison https://github.com/apache/ ...

- nodeJS之流stream

前面的话 当内存中无法一次装下需要处理的数据时,或者一边读取一边处理更加高效时,我们就需要用到数据流.NodeJS中通过各种Stream来提供对数据流的操作.本文将详细说明NodeJS中的流strea ...

- Java 8新特性:新语法方法引用和Lambda表达式及全新的Stream API

新语法 方法引用Method references Lambda语法 Lambda语法在AndroidStudio中报错 Stream API 我正参加2016CSDN博客之星的比赛 希望您能投下宝贵 ...

随机推荐

- maven导入外部jar包的方法

maven的导入外部jar包的方法(前提还有外部jar包) 1.问题: 在maven添加依赖包时,添加不成功,可以选择通过外部命令导入到仓库里. 2.命令:(在Dos命令行) mvn install: ...

- css 3 新特性

CSS3的新特性大致分为以下六类 1.CSS3选择器 2.CSS3边框与圆角 3.CSS3背景与渐变 4.CSS3过渡 5.CSS3变换 6.CSS3动画 下面分别说一说以上六类都有哪些内容 CSS3 ...

- feign多文件上传

参考地址:https://www.cnblogs.com/standup/p/9090113.html https://www.cnblogs.com/standup/p/9093753.html 1 ...

- 聊聊 Scala 的伴生对象及其意义

2019-04-22 关键字:Scala 伴生对象的作用 关于 Scala 伴生对象,比教材更详细的解释. 什么是伴生对象? 教材中关于伴生对象的解释是:实现类似 Java 中那种既有实例成员又有静态 ...

- vim主题颜色

1.VIM主题 查看Vim示例当前的颜色主题 打开一个Vim窗口,输入命令:color或:colorscheme后回车查看当前的颜色主题. Vim实例中设置颜色主题 输入命令"colorsc ...

- 【dp】P2642 双子序列最大和

题目描述 给定一个长度为n的整数序列,要求从中选出两个连续子序列,使得这两个连续子序列的序列和之和最大,最终只需输出最大和.一个连续子序列的和为该子序列中所有数之和.每个连续子序列的最小长度为1,并且 ...

- calico客户端工具calicoctl

工具介绍: Calico的二进制程序文件calicoctl可以直接操作Calico存储来查看,修改或配置Calico系统特性. 三种方式部署calicoctl:①二进制安装:②docker安装:③运行 ...

- linux查看主板型号、CPU、显卡、硬盘等信息

系统 uname -a # 查看内核/操作系统/CPU信息 head -n 1 /etc/issue # 查看操作系统版本 cat /proc/cpuinfo # 查看CPU信息 hostname # ...

- mysql 修改表结构、表字段注释语句

虽然现在有各种各样的工具可以直接对表结构进行修改,但是我还是喜欢使用语句进行修改.以下语句是对表增加字段.给字段加注释的语句 alter table orders add column isupdyq ...

- python第十三天,函数的嵌套定义,global,nonlocal关键字的使用,闭包及闭包的运算场景,装饰器

今日内容 1. 函数的嵌套定义 2.global,nonlocal关键字 3.闭包及闭包的运用场景 4.装饰器 函数的嵌套定义 1. 概念:在一个函数内部定义另一个函数 2 .为什么要有函数的嵌套定义 ...