全志A40i+Logos FPGA开发板(4核ARM Cortex-A7)硬件说明书(上)

前 言

本文档主要介绍TLA40iF-EVM工业评估板硬件接口资源以及设计注意事项等内容。

核心板的ARM端和FPGA端的IO电平标准一般为3.3V,上拉电源一般不超过3.3V,当外接信号电平与IO电平不匹配时,中间需增加电平转换芯片或信号隔离芯片。按键或接口需考虑ESD设计,ESD器件选型时需注意结电容是否偏大,否则可能会影响到信号通信。

核心板CPU、ROM、RAM、电源、晶振等所有器件均采用国产工业级方案,国产化率100%。同时,评估底板大部分元器件亦采用国产工业级方案。

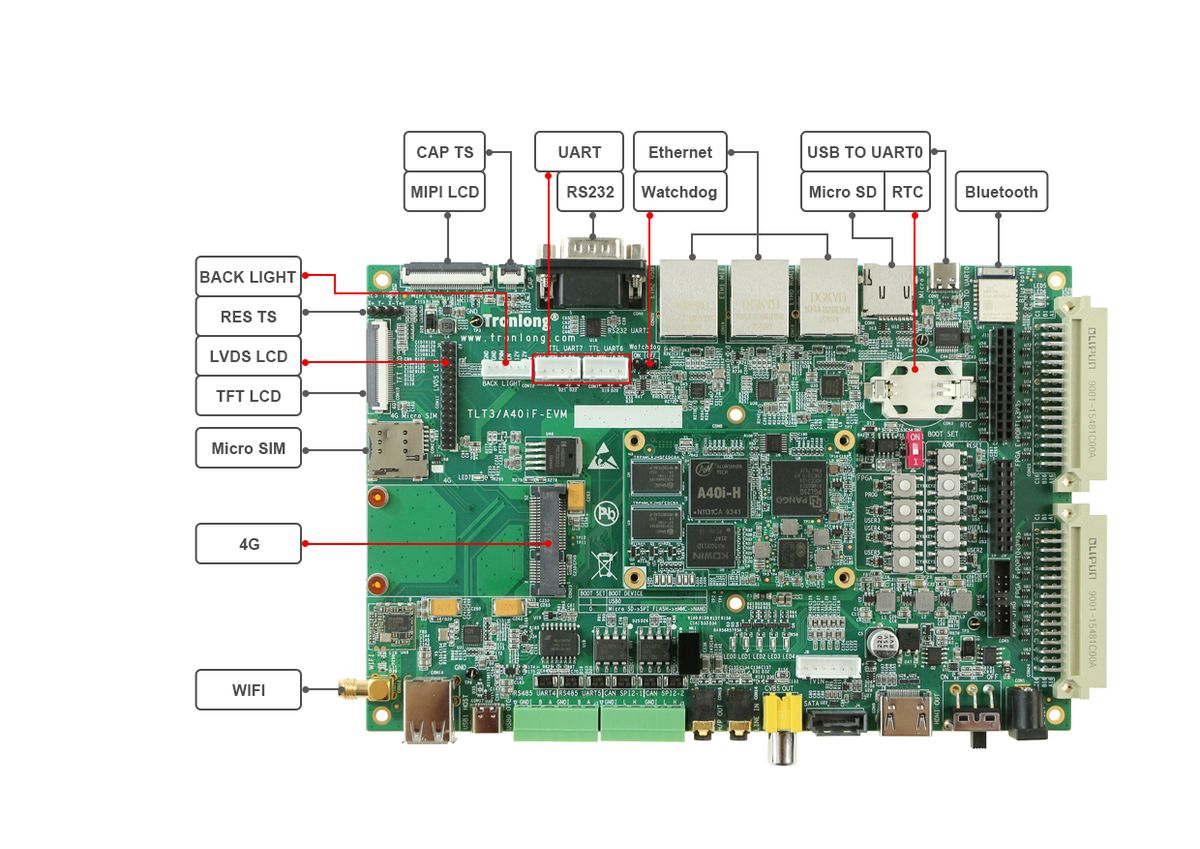

图 1 评估板硬件资源图解1

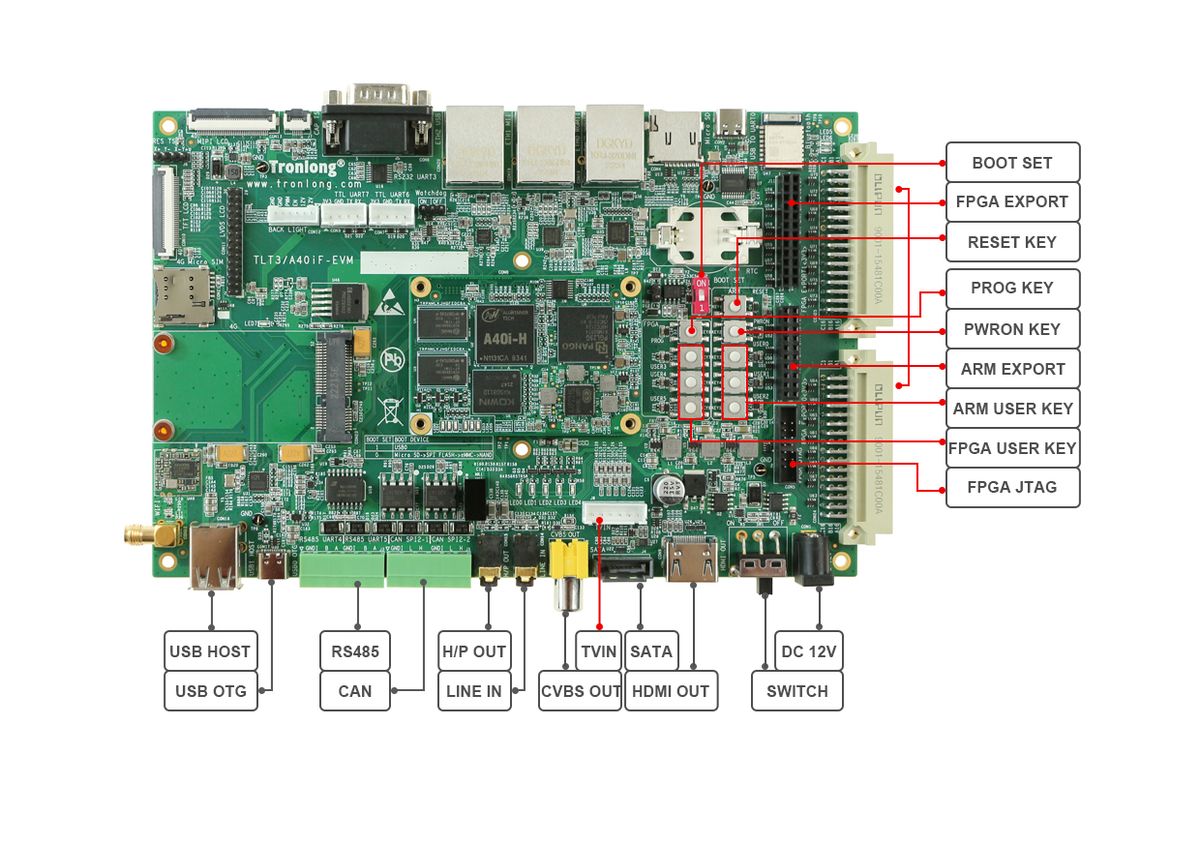

图 1 评估板硬件资源图解1 图 2 评估板硬件资源图解2

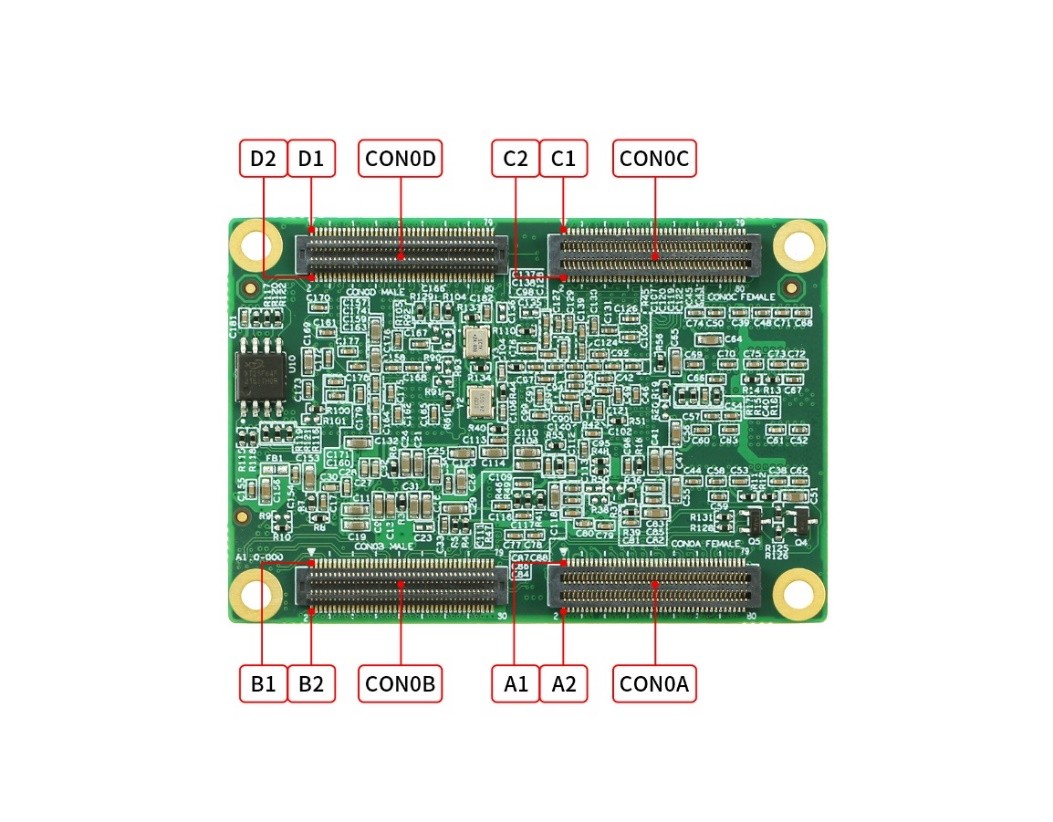

图 2 评估板硬件资源图解2SOM-TLA40iF核心板

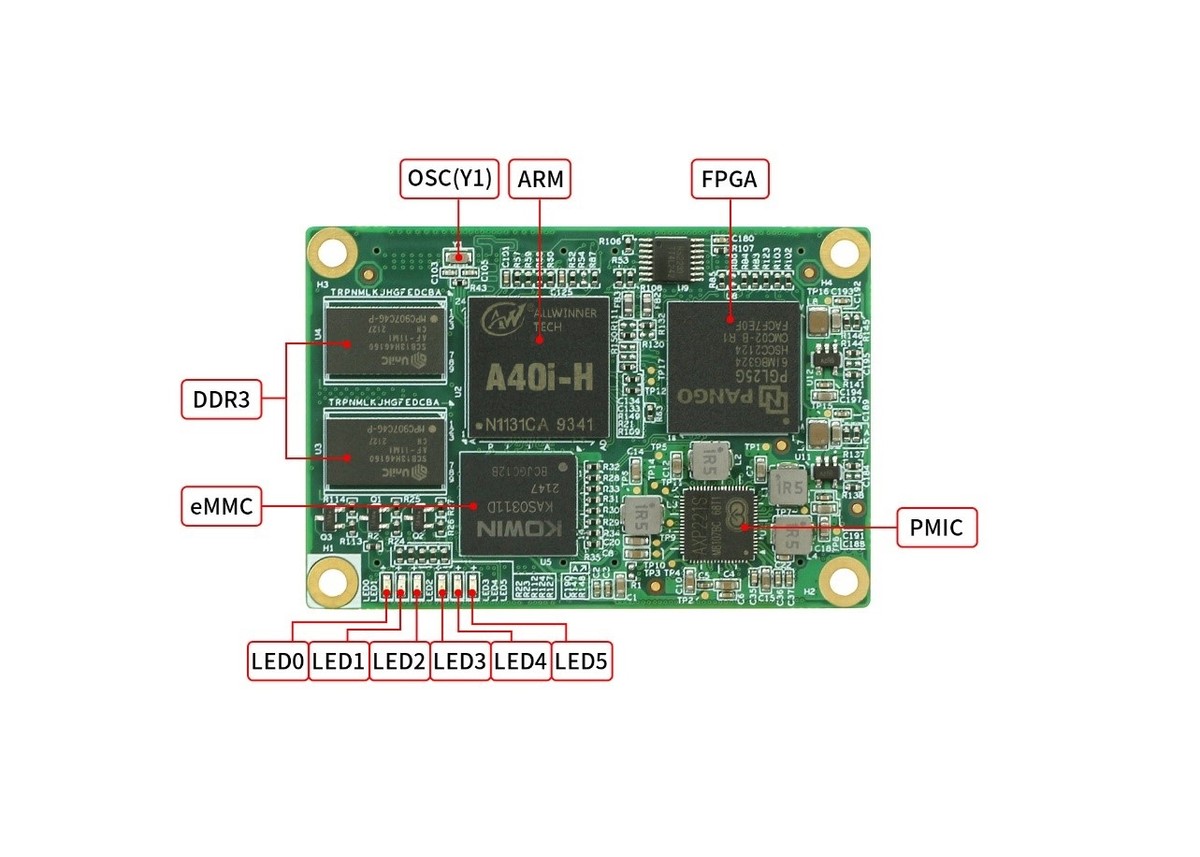

SOM-TLA40iF核心板板载CPU、ROM、RAM、晶振、电源、LED等硬件资源,并通过工业级B2B连接器方式引出IO。核心板硬件资源、引脚说明、电气特性、机械尺寸、底板设计注意事项等详细内容,请查阅《SOM-TLA40iF工业核心板硬件说明书》。

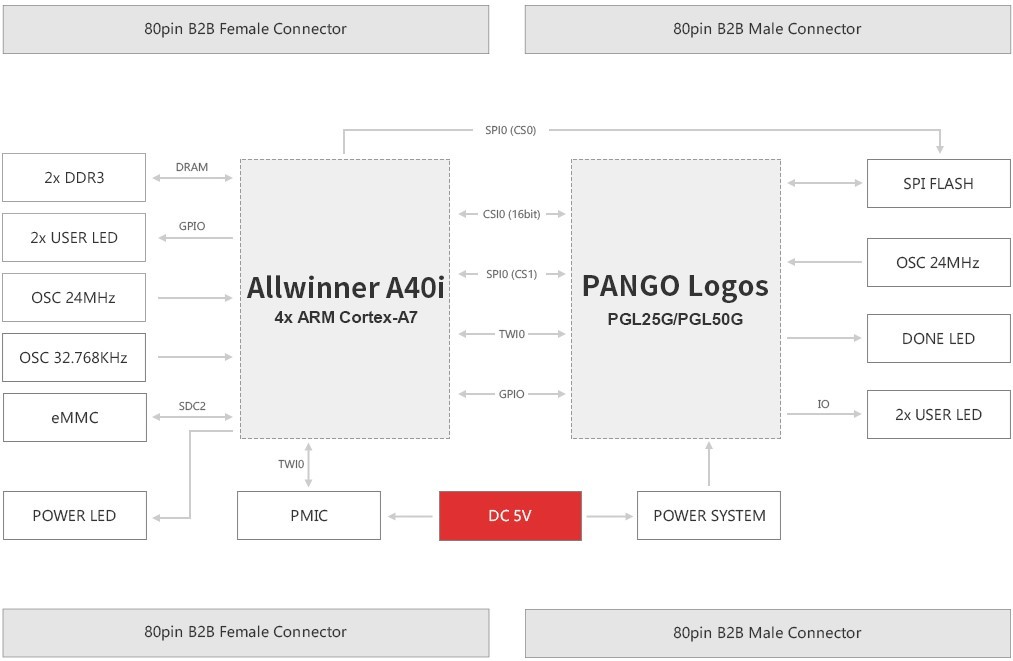

图 3 核心板硬件框图

图 3 核心板硬件框图 图 4

图 4 图 5

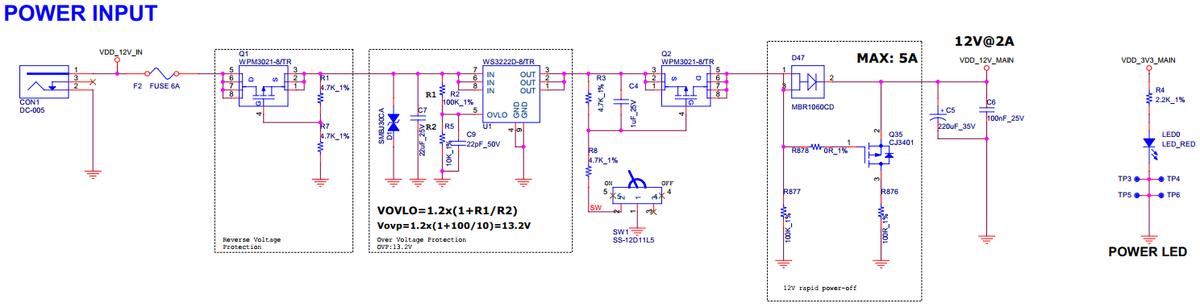

图 5电源接口

CON1为采用12V直流输入DC-005电源接口,可接外径5.5mm、内径2.1mm的电源插头。电源输入带有过流过压保护功能。

SW1为电源拨动开关。

图 6

图 6 图 7

图 7 图 8

图 8 图 9

图 9 图 10

图 10设计注意事项:

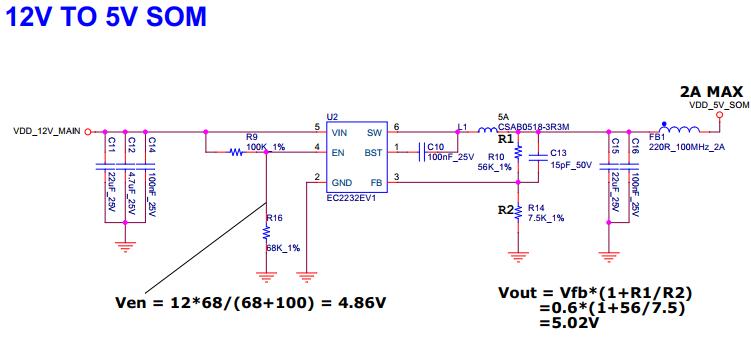

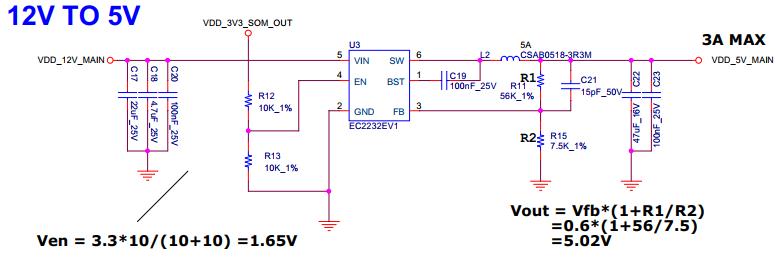

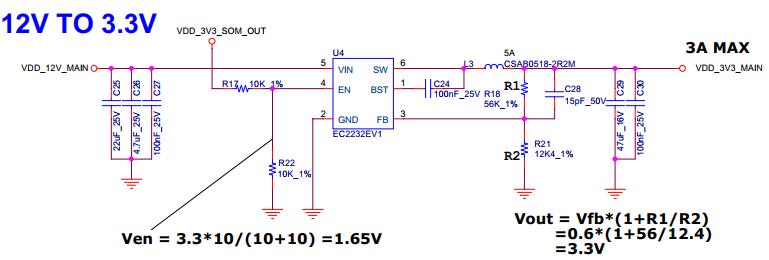

- VDD_12V_MAIN通过EC2232EV1(DC-DC降压芯片)输出VDD_5V_SOM供核心板使用,通过另2路EC2232EV1芯片分别输出VDD_5V_MAIN和VDD_3V3_MAIN供评估底板外设使用。

- 为使VDD_5V_MAIN、VDD_3V3_MAIN满足系统上电、掉电时序要求,需使用核心板输出VDD_3V3_SOM_OUT来控制VDD_5V_MAIN和VDD_3V3_MAIN的电源使能,使评估底板VDD_5V_MAIN和VDD_3V3_MAIN电源在核心板电源之后上电,且在AP-RESETn/3V0复位信号之前上电,即评估底板VDD_5V_MAIN和VDD_3V3_MAIN电源需晚于12V输入电源200ms内完成上电。

- VDD_5V_SOM在核心板内部未预留总电源输入的储能大电容。底板设计时,请在靠近B2B连接器焊盘位置放置储能大电容。

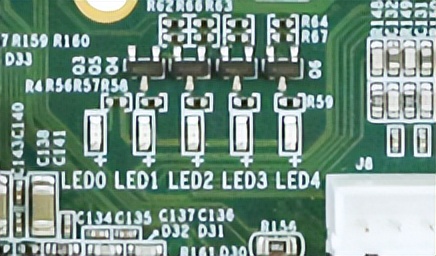

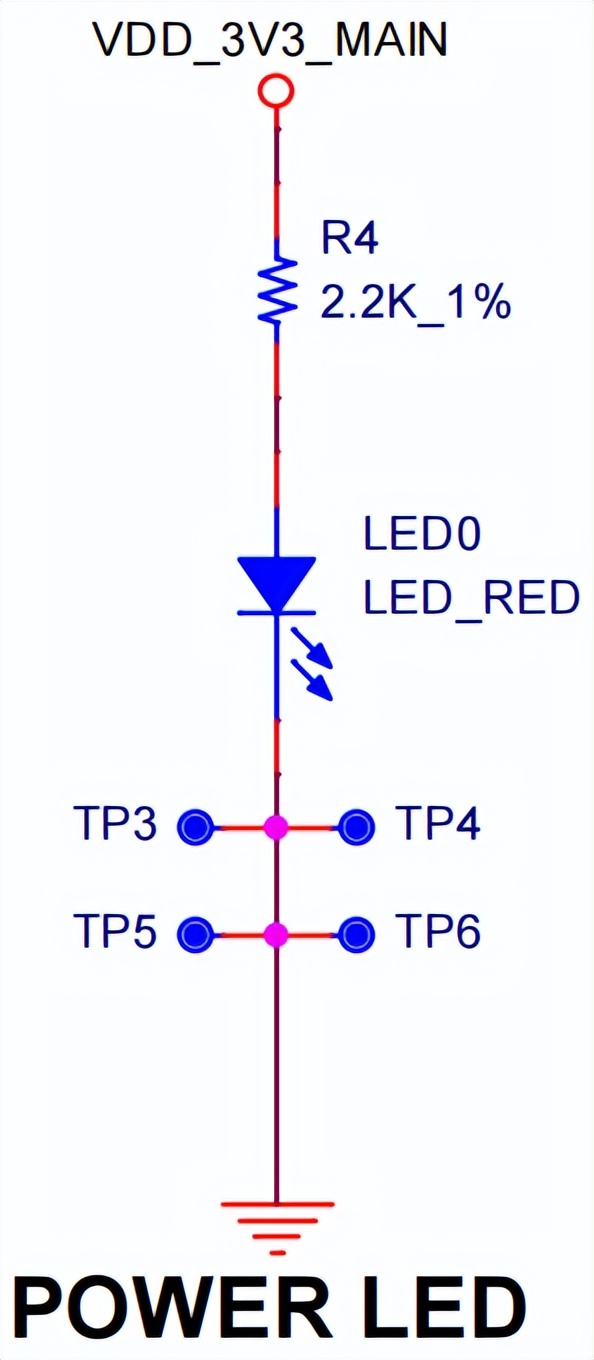

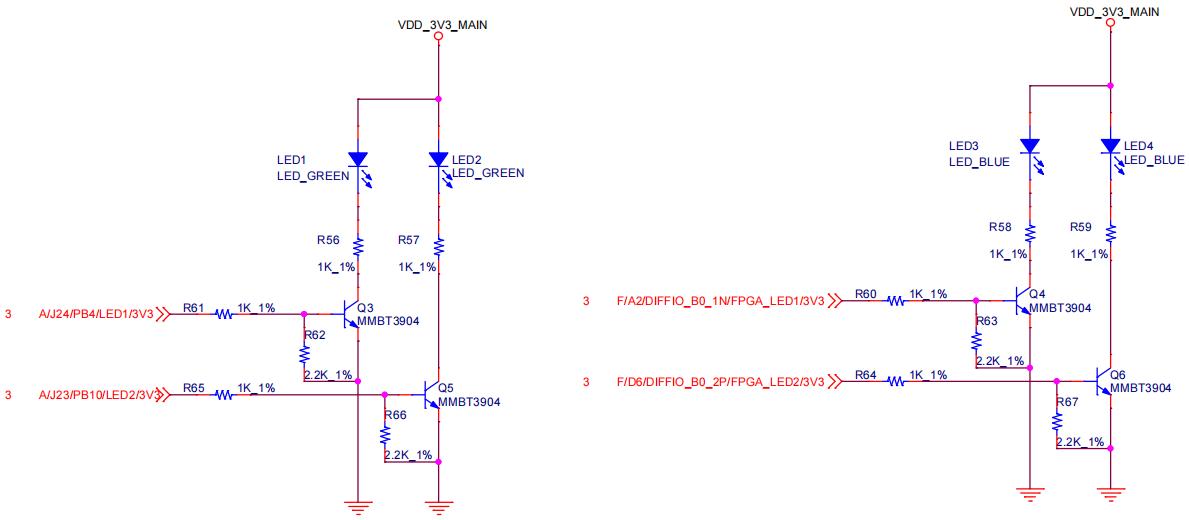

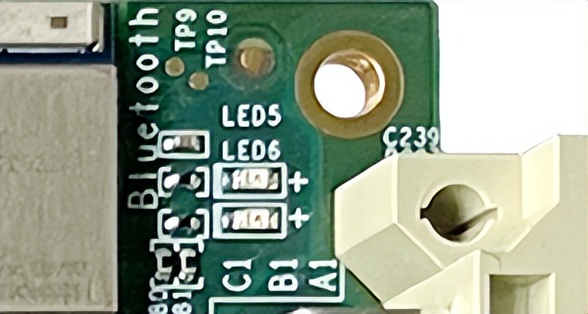

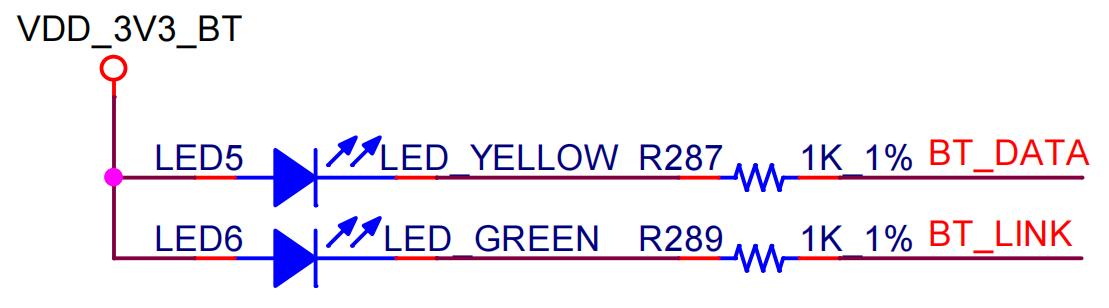

LED

评估底板板载8个LED。LED0为3.3V电源指示灯,上电默认点亮;LED1、LED2为ARM端用户可编程指示灯,通过GPIO控制,默认高电平点亮;LED3、LED4为FPGA端用户可编程指示灯,通过GPIO控制,默认高电平点亮;LED5、LED6为蓝牙模块状态指示灯;LED7为4G模块状态指示灯。

图 11 电源指示灯和用户可编程指示灯

图 11 电源指示灯和用户可编程指示灯 图 12

图 12 图 13

图 13 图 14

图 14 图 15

图 15 图 16 4G模块状态指示灯

图 16 4G模块状态指示灯 图 17

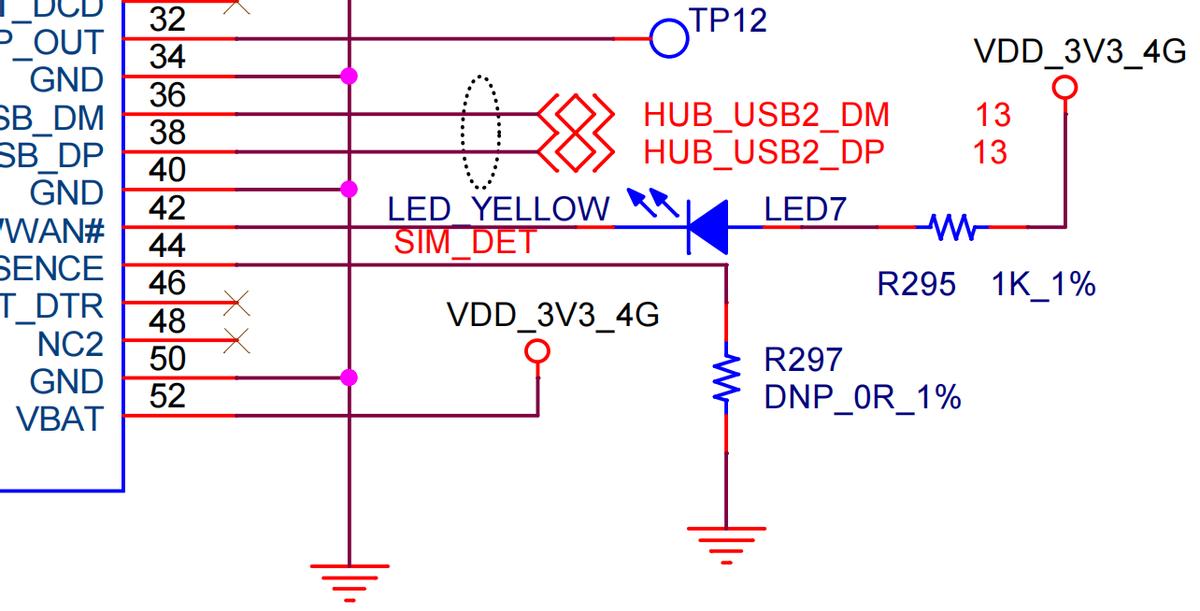

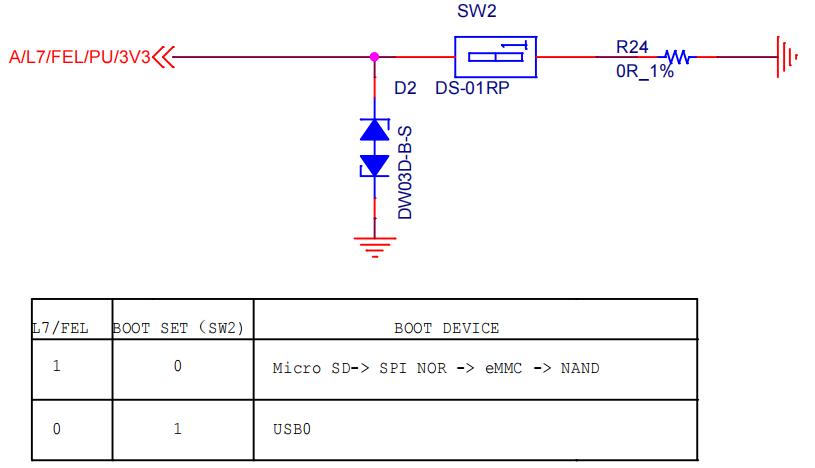

图 17BOOT SET启动方式选择拨码开关

SW2为1bit启动方式选择拨码开关,支持Micro SD、SPI FLASH、eMMC、NAND FLASH和USB启动。

当BOOT SET为0时(根据评估底板丝印确认),CPU将按Micro SD -> SPI FLASH -> eMMC -> NAND顺序检测存储设备并启动系统。

- 0:Micro SD -> SPI FLASH -> eMMC -> NAND。

- 1:USB0。

图 18

图 18 图 19

图 19设计注意事项:

- 核心板内部L7/FEL已设计10K上拉电阻,当L7/FEL为高电平(即SW2为0)时,CPU会按顺序检测对应设备并启动系统。

- 请参考评估底板BOOT SET电路进行启动配置电路设计。

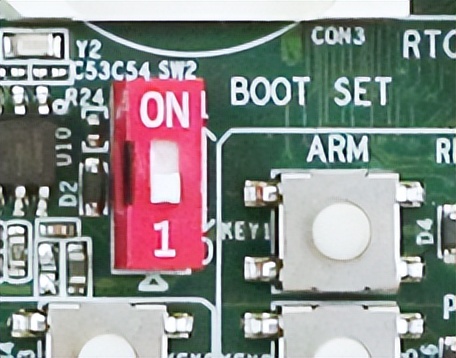

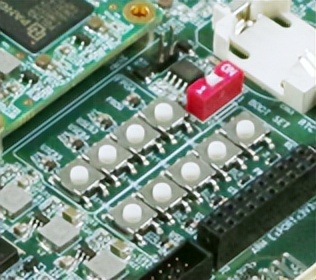

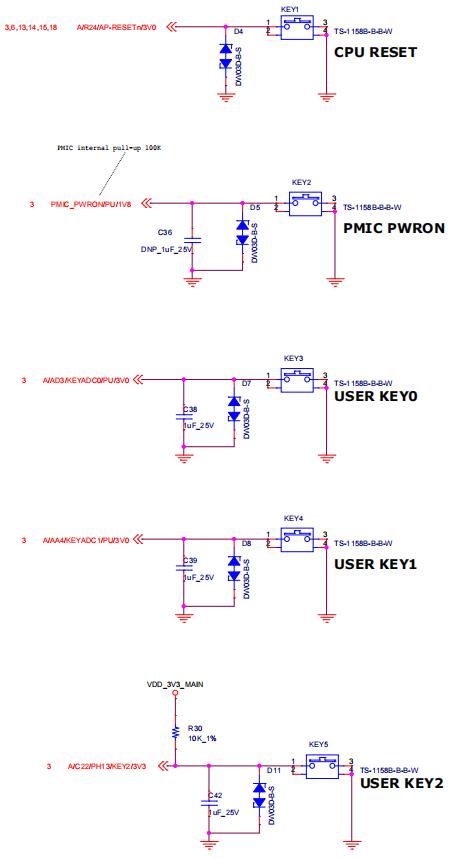

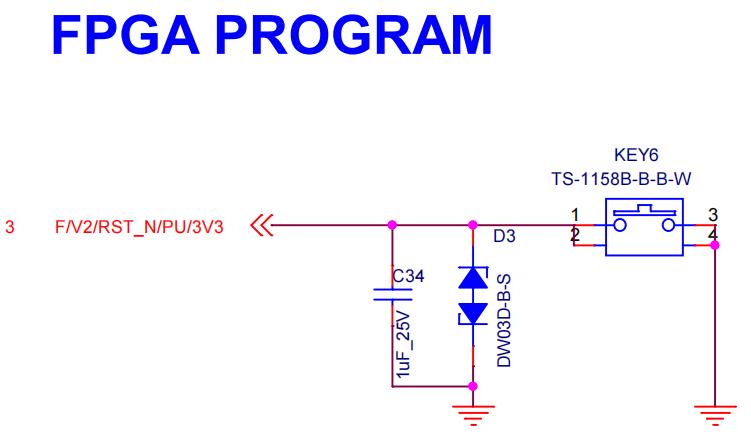

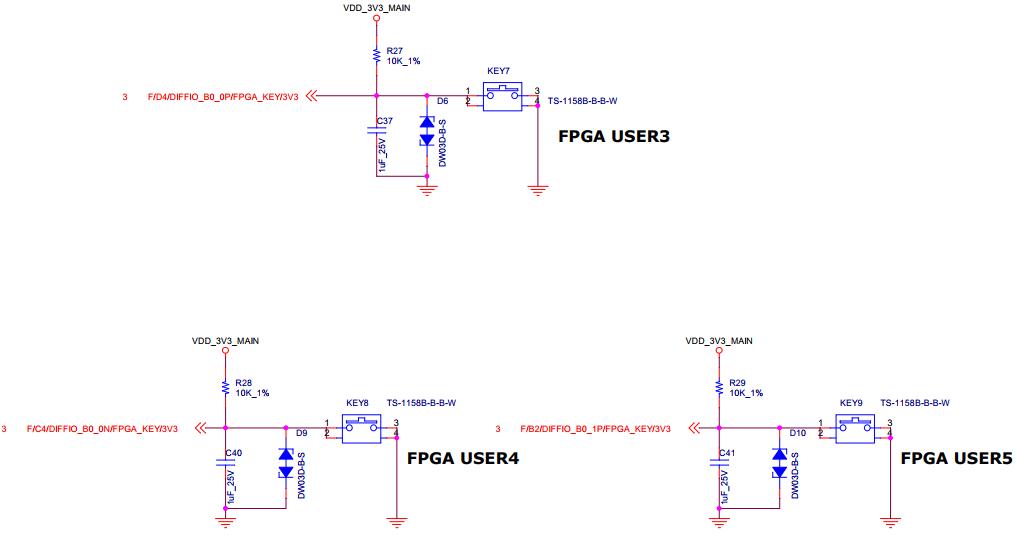

KEY

评估底板ARM端包含1个系统复位按键RESET(KEY1),1个PMIC开关机按键PWRON(KEY2),3个用户输入按键USER0(KEY3)、USER1(KEY4)、USER2(KEY5)。FPGA端含1个PROG按键(KEY6)、3个用户输入按键USER3(KEY7)、USER4(KEY8)、USER5(KEY9)。

图 20

图 20 图 21

图 21 图 22

图 22 图 23

图 23设计注意事项:

- A/R24/AP-RESETn/3V0为CPU的复位输入引脚,直连至PMIC的PWROK输出引脚。默认情况,请悬空处理,以避免影响上电时序。

- PMIC_PWRON/PU/1V8为PMIC的开关机控制引脚,长按PMIC将会关机。再次长按,PMIC将切换为开机。PMIC内部已上拉100K电阻,默认情况,请悬空处理。

- KEYADC0、KEYADC1的输入范围为0~2V,在核心板内部已上拉100K电阻至3V,底板可通过分压电阻将输入电压控制在0~2V之间。

- F/D4/DIFFIO_B0_0P/FPGA_KEY/PU/3V3在核心板上已上拉1K电阻至3.3V,该信号引脚为FPGA端IO上电期间的状态配置引脚。当IO_STATUS_C=0,使能内部pullup,当IO_STATUS_C=1,关掉内部pullup。

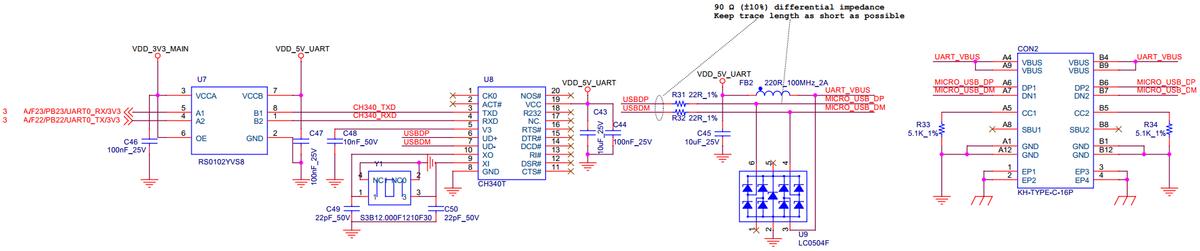

串口

评估底板板载6个串口,CON2为USB TO UART0串口,CON6为RS232 UART3串口,J3为RS485 UART4、RS485 UART5串口,CON7、CON8分别为TTL UART6、TTL UART7串口。

USB TO UART0串口

评估板通过CH340T芯片将UART0转成Type-C接口,作为系统调试串口使用。

图 24

图 24 图 25

图 25设计注意事项:

- 为避免RX端在底板上电之前,提前带电,并向CPU灌输电流,导致CPU无法启动,底板设计时,建议参考评估底板的电平转换隔离方案或使用带电平隔离的调试工具进行调试。

- 底板上电过程中需保持RX端电平稳定,以避免系统无法进入内核阶段的情况,底板设计时,建议参考评估底板的电平转换隔离方案或者使用带电平隔离的调试工具进行调试。

- 请注意TX、RX接口电平皆为3.3V,请勿使用5V电平接口的调试工具直接连接,否则将会导致核心板IO损坏。

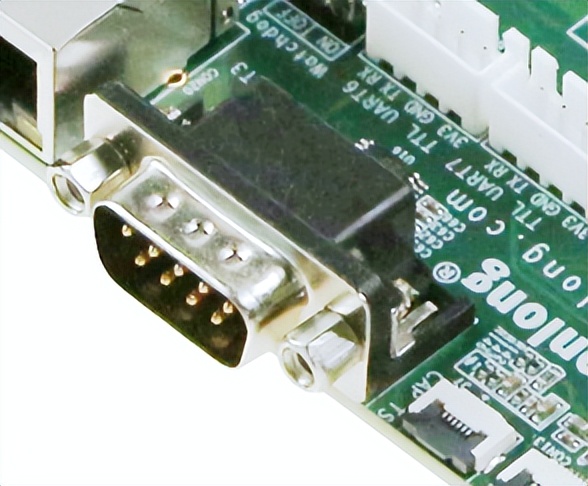

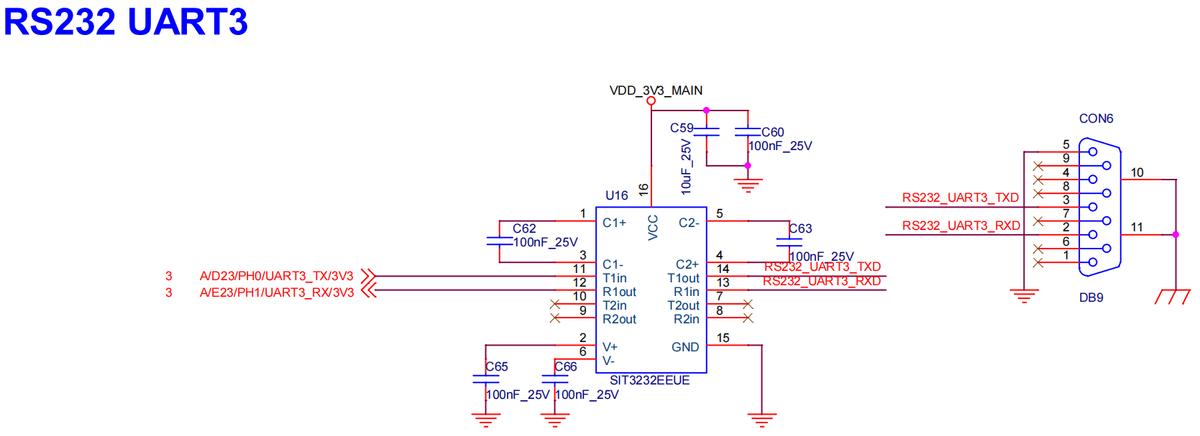

RS232 UART3串口

评估板通过SIT3232EEUE串口电平转换芯片将UART3转换为RS232串口,使用9针DB9接口。

图 26

图 26 图 27

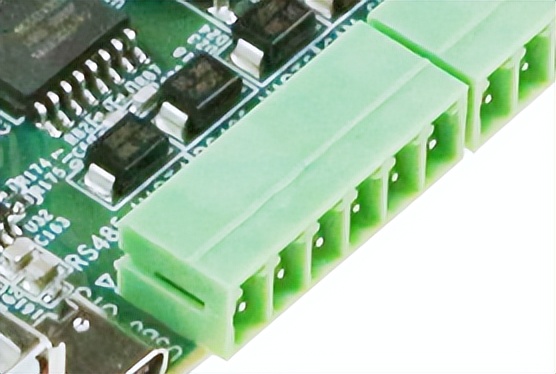

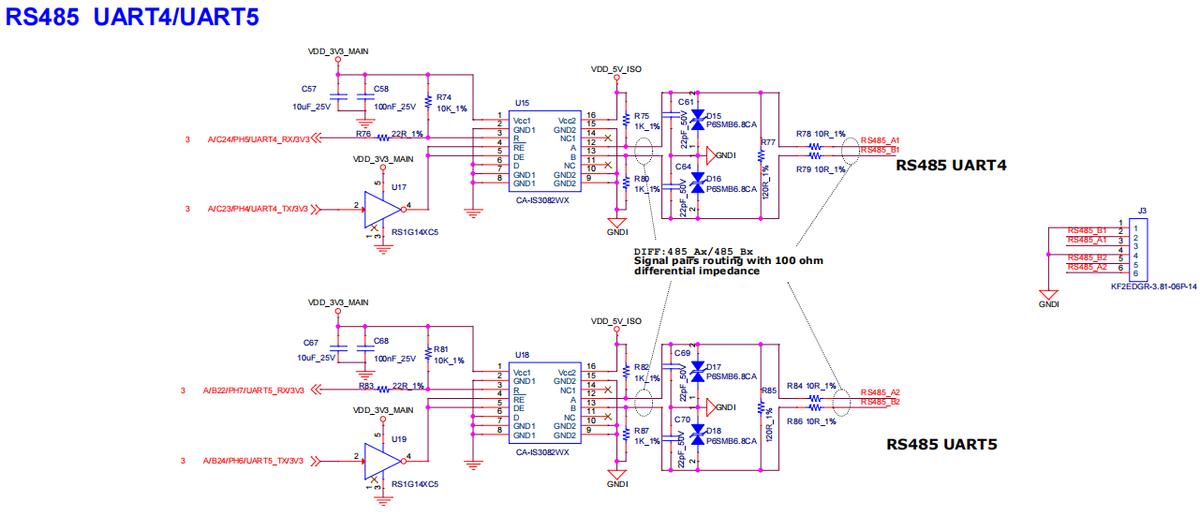

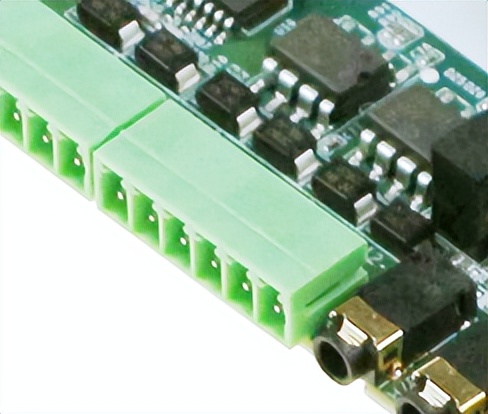

图 27RS485 UART4/RS485 UART5串口

评估板通过2个隔离收发器CA-IS3082WX,将UART4、UART5分别转换为RS485串口,采用6pin 3.81mm绿色端子方式引出。

图 28

图 28 图 29

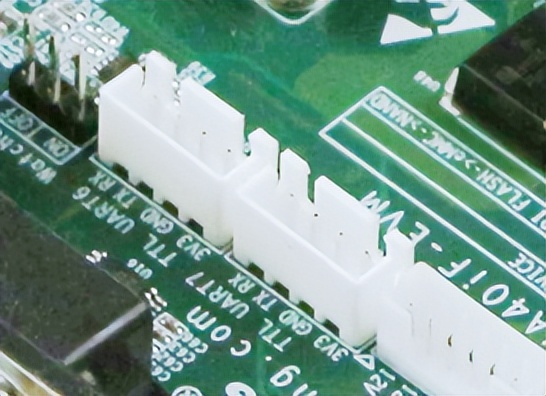

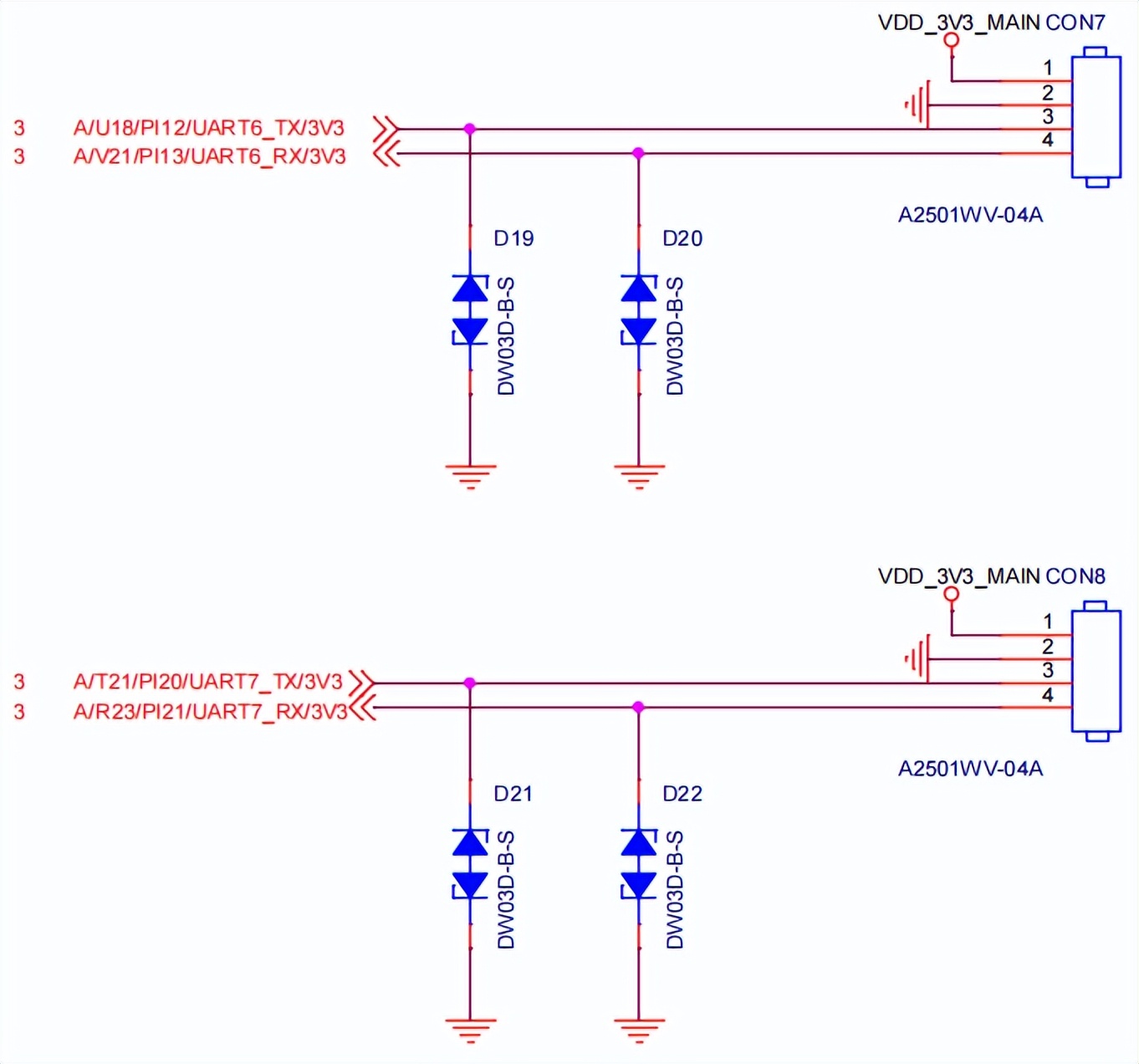

图 29TTL UART6/UART7串口

评估板直接引出UART6、UART7作为TTL串口,接口均采用4pin 2.54mm白色端子方式。

图 30

图 30 图 31

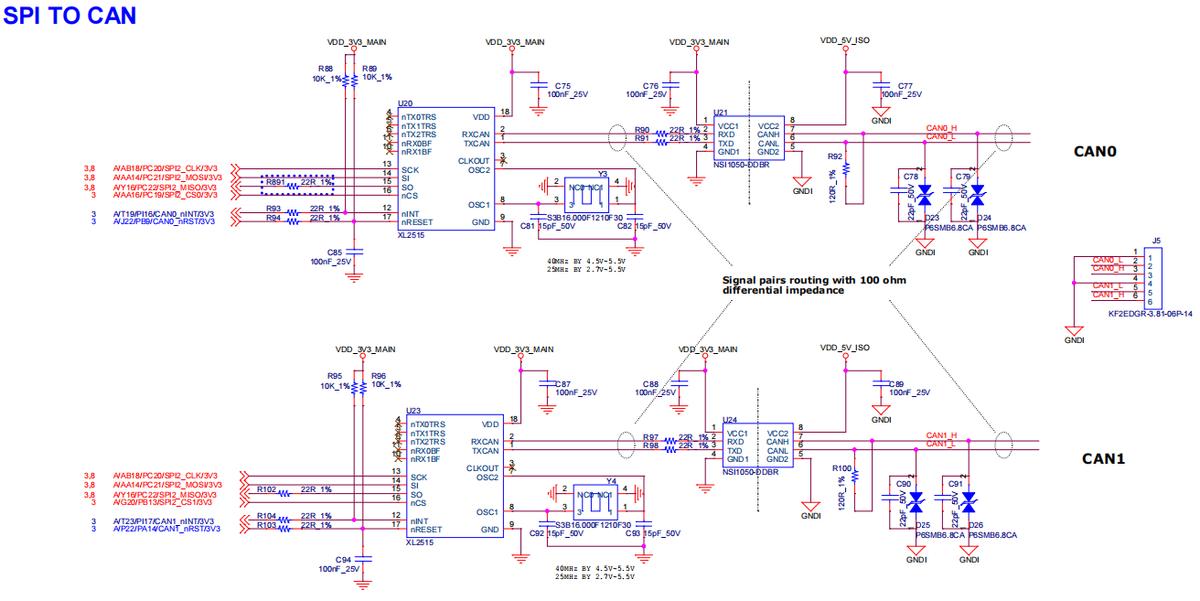

图 31CAN接口

J5为通过SPI2总线(2个片选)拓展引出的2路CAN接口,分别为CAN SPI2-1、CAN SPI2-2,均采用6pin 3.81mm绿色端子方式。

图 32

图 32 图 33

图 33设计注意事项:

(1)若U20和U23的nINT引脚需分配使用其他IO,请使用引脚信号名称包含EINTx字段(支持中断功能)的IO引脚。

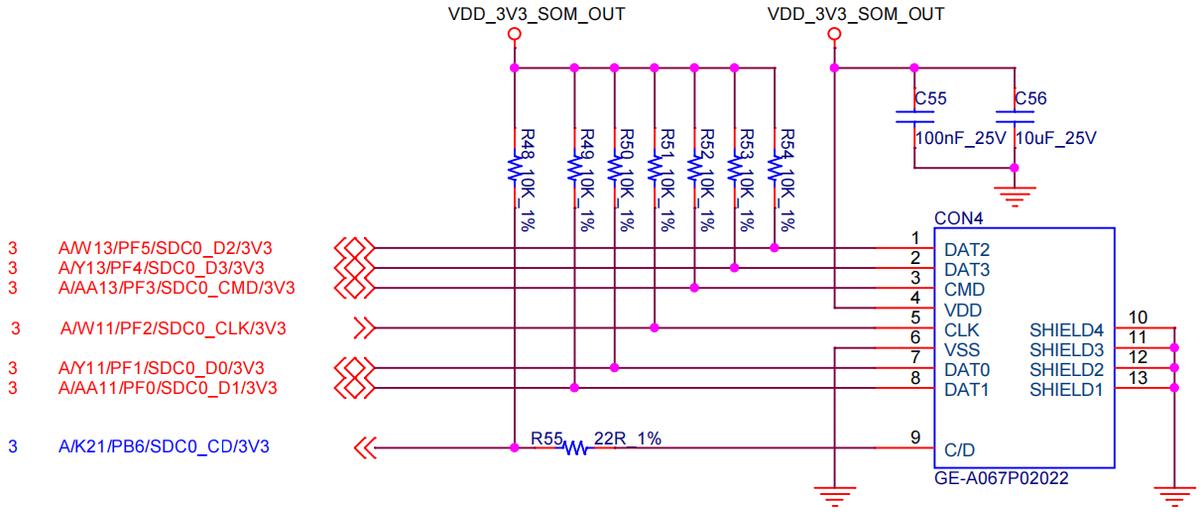

Micro SD接口

CON4为Micro SD卡接口,通过SDC0总线引出,采用4bit数据线模式。

图 34

图 34 图 35

图 35设计注意事项:

- 需将TF座子外壳的SHIELD[1:4]接至数字地。

- 建议使用核心板的输出电源VDD_3V3_SOM_OUT给Micro SD(CON4)供电。如使用VDD_3V3_MAIN供电,将可能因该电源存在供电延迟,导致CPU无法正确地读取到Micro SD卡设备而启动失败。

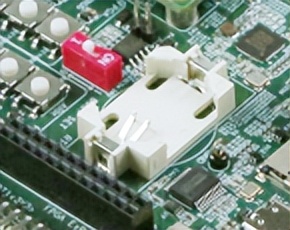

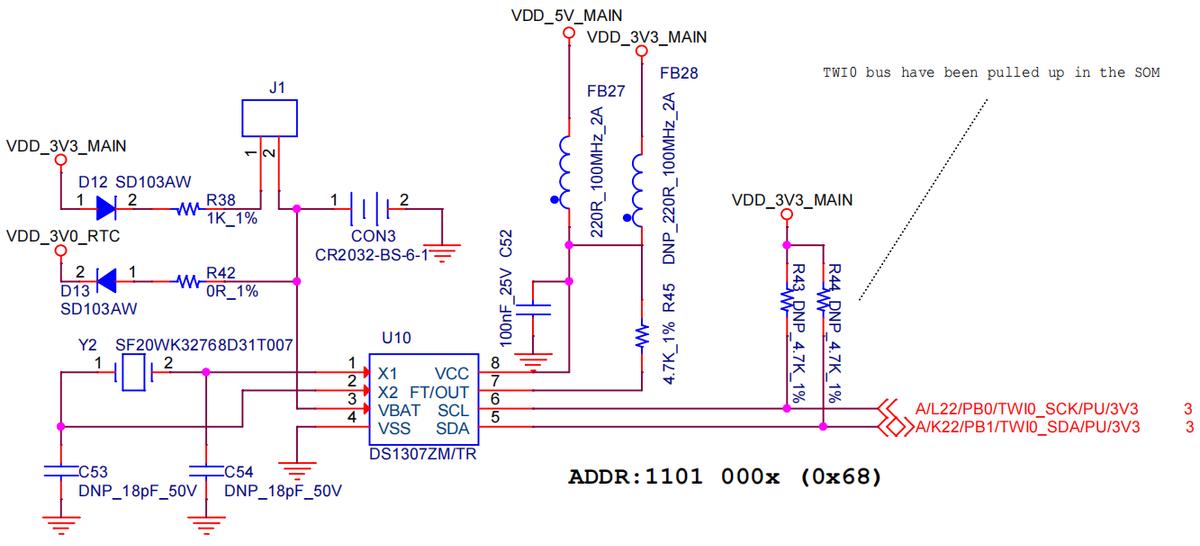

RTC座

评估底板使用DS1307ZM/TR芯片实现外部RTC功能。CON3为RTC纽扣电池座,适配纽扣电池ML2032(3V可充)、CR2032(3V不可充)。使用可充电电池时,可将跳线帽插入J1接口实现充电。使用不可充电电池时,请勿将跳线帽插入J1接口。

图 36

图 36 图 37

图 37设计注意事项:

- TWI0总线在核心板内部已设计上拉2K电阻至3.3V。

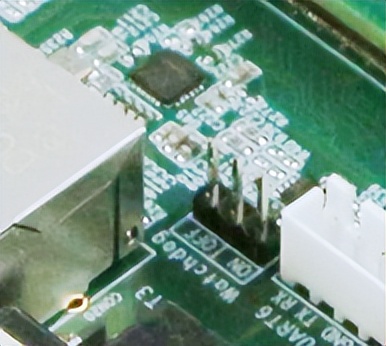

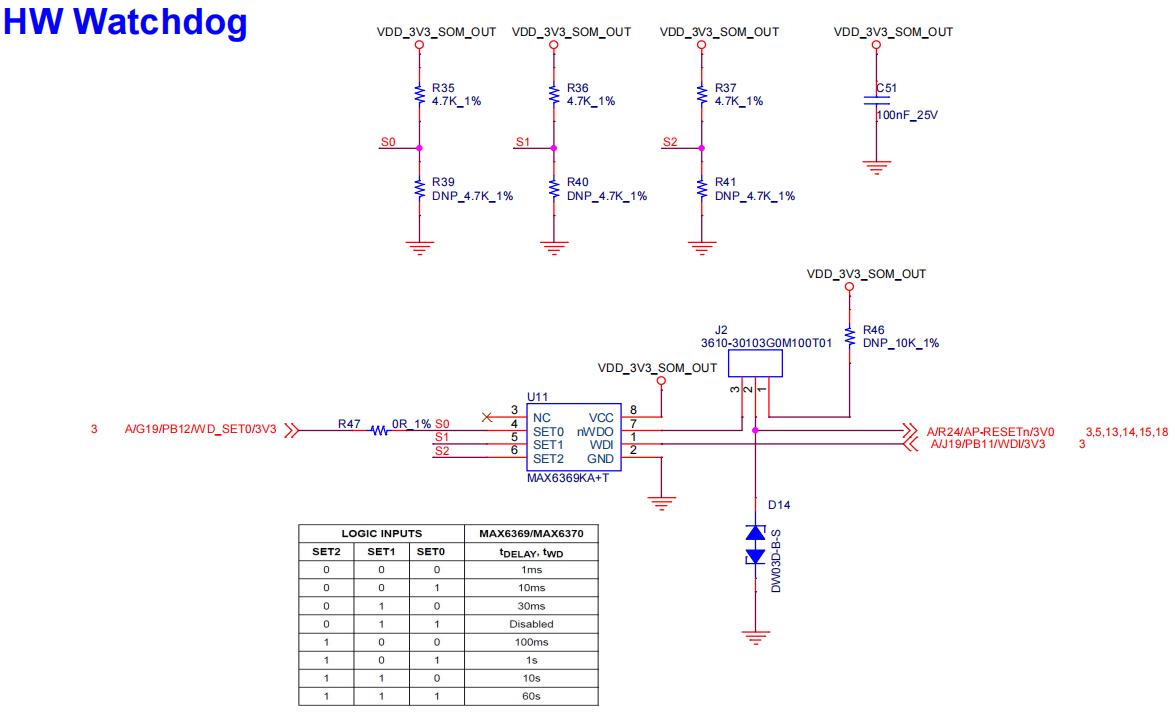

Watchdog接口

评估底板引出3pin 2.54mm间距排针(J2)作为Watchdog功能配置接口,可通过跳线帽配置使能Watchdog功能。软件上可通过A/G19/PB12/WD_SET0/3V3来控制Watchdog超时时长。

备注:Watchdog芯片生产商为美国厂家。

图 38

图 38 图 39

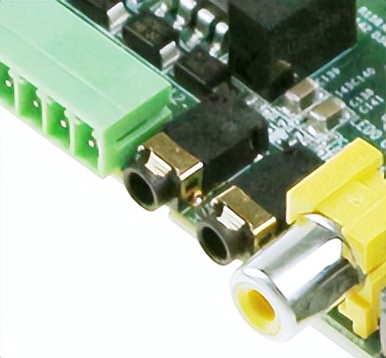

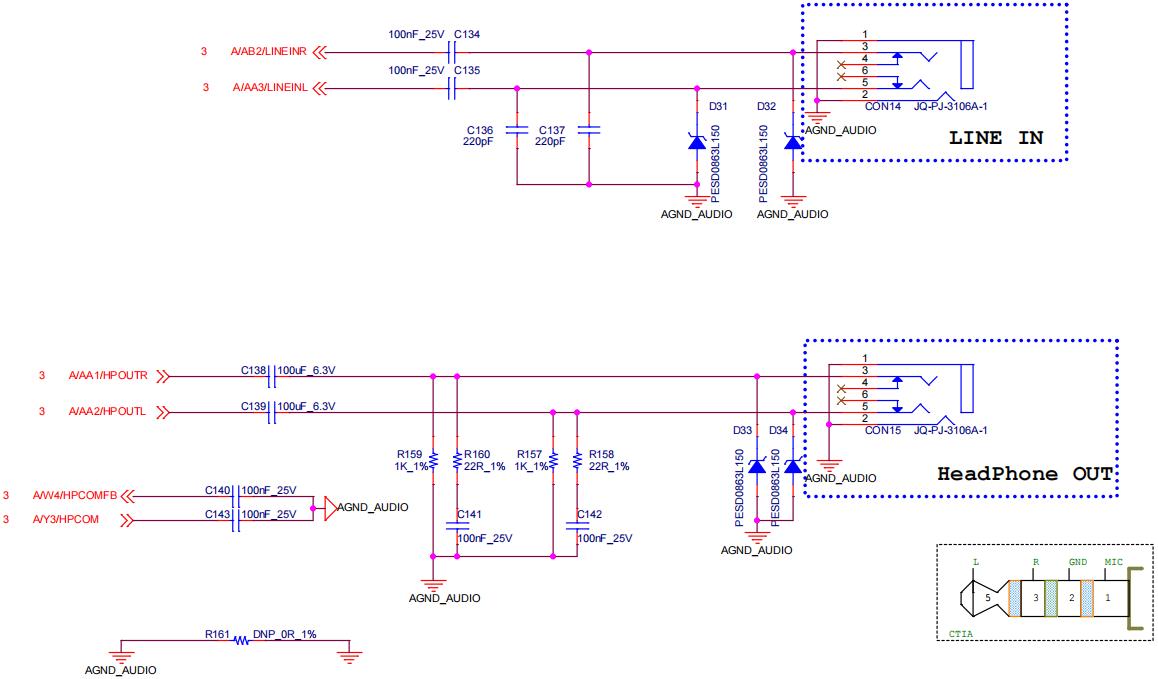

图 39AUDIO接口

CON14为LINE IN音频接口,CON15为H/P(Headphone) OUT音频接口,均采用3.5mm音频插座。

图 40

图 40 图 41

图 41由于篇幅过长原因,文章分为上下篇,想要查看更多详细硬件参数说明,请点击账户查看其他文章,感谢您的关注,有开发上的问题欢迎在评论区留言。

全志A40i+Logos FPGA开发板(4核ARM Cortex-A7)硬件说明书(上)的更多相关文章

- 关于DE2-115 FPGA开发板无法烧写程序的解决方法

友晶科技推出的DE2-115 FPGA开发板,有时候莫名奇妙,无法烧写或者固化程序.利用JTAG 向DE2-115开发板烧写.sof文件失败,并提示以下错误,如图1和图2所示 图1 图2 解决方法:只 ...

- FPGA 开发板入手途径有哪些呢?

买到一块 FPGA 开发板,你如何入手呢? 根据博主的经验,你可以通过如下途径来学习: 1.如果你是淘宝上买的,那么可以在淘宝上搜索你的开发板(一般 FPGA 开发板生厂商在淘宝上卖都会附带教程,如米 ...

- 迅为三星Exynos 4412开发板四核Cortex-A9ARM安卓linux开发板

开发板光盘资料包含:原理图(PDF格式).底板PCB(Allegro格式).驱动程序源码.芯片和LCD数据手册.开发环境.产品使用手册. 4412开发板简介: iTOP-Exynos4412开发板采用 ...

- FPGA开发板

kingst.cnblogs.com 各种应用需要的接口不同: 做数字信号处理的,需要有AD/DA, 做图像处理,需要有图像接口.如果是通信的,需要有通信的接口,例如PCI/LVDS等.... 然后根 ...

- 至芯FPGA培训中心-1天FPGA设计集训(赠送FPGA开发板)

至芯FPGA培训中心-1天FPGA设计集训(赠送开发板) 开课时间2014年5月3日 课程介绍 FPGA设计初级培训班是针对于FPGA设计技术初学者的课程.课程不仅是对FPGA结构资源和设计流程的描述 ...

- SoC FPGA开发板的FPGA配置数据下载和固化

小梅哥编写,未经许可,严禁用于任何商业用途 2018年7月2日星期一 soc fpga的烧写和固化方式与传统的纯fpga固化方式即存在形式上的相同,也存在细节上的差异,特整理此文. AC501-So ...

- 使用FPGA开发板驱动VGA显示器

1. 本次使用的是cyclone4开发板,先看下原理图,因为右边的RGB应该是模拟信号量,但是本次例程只接了3根线,那就是说颜色只有8种. 2. 代码,输出信号有R,G,B三色,就是上图右边的,行同步 ...

- JZ2440开发板:修改ARM芯片时钟(学习笔记)

想要修改ARM芯片的时钟,需要去查询芯片手册和原理图,获取相关的信息(见下方图片) 首先来看时钟的结构图 根据结构图可以看出,时钟源有两种选择:1. XTIpll和XTOpll所连接的晶振 2. EX ...

- 【STM32-V7】STM32H743XIH6开发板,丰富软件资源,强劲硬件配置,大量软件解决方案持续更新中(2019-12-12)

说明: 争取做更多的实战性应用,分享更多的嵌入式技术,希望能在实际项目中帮到大家. (1)V7将大力加强对初学者的支持力度,已经更新至63章,下载链接,后37章和一批视频教程将加紧制作. (2)事隔五 ...

- 【ARM-Linux开发】ARM7 ARM9 ARM Cortex M3 M4 有什么区别

ARM7 ARM9 ARM Cortex M3 M4 区别 arm7 arm9 可以类比386和奔腾, 不同代,arm9相比arm7指令集和性能都有所增强,arm7和arm9都有带mmu和无mmu的版 ...

随机推荐

- 聊聊流言协议(Gossip)

什么是流言协议? 在分布式系统中,以下两个是典型的问题: 维护系统状态(节点的活跃性) 节点间的通信 解决这些问题的解决方案之一如下: 集中式状态管理服务 对等状态管理服务 集中式状态管理服务 像 A ...

- AI 编译器CINN中的OpLowering优化Pass

一.Lower 主逻辑 在 OpLower::Lower() 接口中,主要分为两大类: Elementwise类,主要涉及的 OpPattern 包括:kElementwise .kBroadcast ...

- ansible(11)--ansible的user和group模块

1. group模块 功能:管理被控端用户组: 主要参数如下: 参数 说明 name 指定创建的组名 gid 为组设置gid state 是否将组创建在远程主机上,创建:present(Default ...

- JavaScript算法---基础排序类

<html> <script> //正序排序,把大的放到最后,arr[j]>arr[j+1] let fz=(arr)=>{ for(let len=arr.len ...

- 【0day漏洞复现】北京慧飒科技有限责任公司WEB VIDEO PLATFORM存在未授权访问漏洞

阅读须知 花果山的技术文章仅供参考,此文所提供的信息只为网络安全人员对自己所负责的网站.服务器等(包括但不限于)进行检测或维护参考,未经授权请勿利用文章中的技术资料对任何计算机系统进行入侵操作.利用此 ...

- vulnhub靶场-->MATRIX-BREAKOUT: 2 MORPHEUS

靶机下载地址 MATRIX-BREAKOUT: 2 MORPHEUS << 点我下载 开始打靶 IP发现 nmap扫描网段发现靶机ip:192.168.111.139 端口发现 对靶机进行 ...

- Github打不开解决办法(最新有效)

Github打不开解决办法(最新有效) 1. 先看没解决之前的截图: 2. 解决方法(手动修改DNS): 2.1 以win11为例,第一步:打开 设置 - 网络和Internet,找到 高级网络 ...

- 基于FPGA的4x4矩阵键盘驱动设计---第一版

欢迎各位朋友关注"郝旭帅电子设计团队",本篇为各位朋友介绍基于FPGA的4x4矩阵键盘驱动设计---第一版 功能说明: 1. 驱动4x4矩阵键盘:按下任意一个按键,解析出对应按键信 ...

- SASS 运算 (Operations)符的基本使用

sass 运算符虽然没有像那些编程语言那么强大,但为了更灵活的输出css,也增强了一些运算符的功能,例如赋值运算符.等号操作符.比较运算符.逻辑运算符.字符串运算符...等等,接下来就来详细介绍下 ...

- android studio 安装与配置

android studio 下载地址:http://www.android-studio.org/ 找一个存储空间,我在D盘上,建好如下目录 : 找到刚才在载的文件 android-stu ...