FPGA大疆考试准备内容

1.寄存器与锁存器

flip-flop:触发器,是时钟边沿触发,可存储1 bit data,是register的基本组成单位,结构图如下:

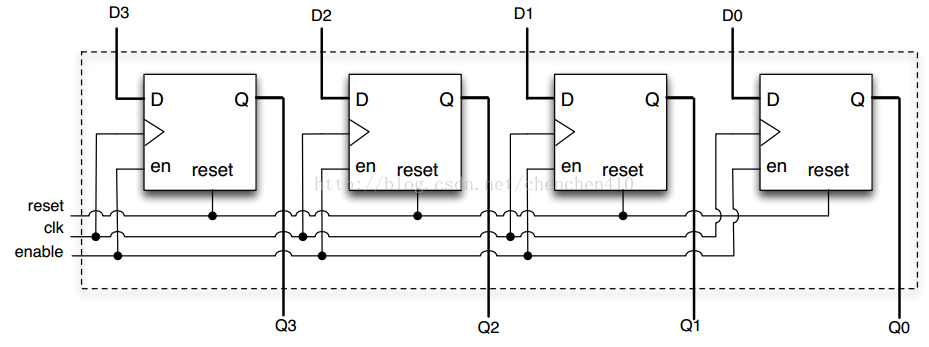

register:寄存器,a hardware register stores bits of information in such a way that systems can write to or read out all the bits simultaneously.就是时钟边沿触发的存储结构,是由多个flip-flop组成,可以构成register file, SRAM等,结构如下:

latch:锁存器,是由电平触发,结构图如下:

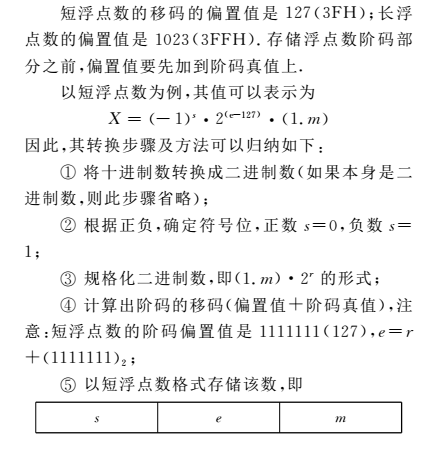

那么其在FPGA上的实现方法:

但是为什么这样的方法就可以实现FPGA的浮点输的转化呢?表示比较疑惑

但是为什么这样的方法就可以实现FPGA的浮点输的转化呢?表示比较疑惑

7.状态机设计:实现序列检测:

根据要检测的序列的长度决定状态的个数,然后设计好状态转移图:根据三段式的设计方案,即可以实现状态机的编写:

三段式序列检测"" module seqdet(din,clk,rst,dout);

input din; //输入

input clk;

input rst;

output dout; //输出

reg dout; reg [:] CS; //现态寄存器

reg [:] NS; //次态寄存器 parameter [:] IDLE = 'b00000, //独热码

A = 'b00001,

B = 'b00010,

C = 'b00100,

D = 'b01000,

E = 'b10000; always @ (posedge clk or negedge rst)

if (!rst)

CS <= IDLE;

else

CS <= NS ; always @ ( CS or din ) begin

NS = 'bx;

case (CS)

IDLE : NS = din ? A : IDLE;

A : NS = din ? A : B;

B : NS = din ? A : C;

C : NS = din ? D : IDLE;

D : NS = din ? A : E;

E : NS = din ? A : C; default: NS = IDLE;

endcase

end always @ ( posedge clk or negedge rst)

if (!rst)

dout <= 'b0;

else

begin

dout <= 'b0;

if (NS == E)

dout <= 'b1;

end

endmodule

状态机之并行数据串行化:

//并行数据串行化

module b2c(din8,clk,slr,din);

input clk,clr;

input [:]din8;

output din;

reg [:]cs,ns;

reg dout;

always@(posedge clk or posedge clr)

begin

if(clr) cs<=;

else cs<=ns;

end always@(clk or din8 or dout)

begin

case(cs)

'b0:

begin

din<din8[];

ns<='b1;

end

'b1:

begin

din<din8[];

ns<='b2;

end

'b2:

begin

din<din8[];

ns<='b3;

end

'b3:

begin

din<din8[];

ns<='b4;

end

'b4:

begin

din<din8[];

ns<='b5;

end

'b5:

begin

din<din8[];

ns<='b6;

end

'b6:

begin

din<din8[];

ns<='b7;

end

'b7:

begin

din<din8[];

ns<='b0;

end

default:

begin

din<='b0;

ns<=;

end

endcase

end

endmodule

8.FIFO深度计算,原来这也是一个神奇的问题啊,首先需要了解其应用的场景,FIFO主要用于数据的缓存,在写快但是读慢的情形下,主要考虑到读写时钟的不一致性问题,主要的计算公式:depth of fifo=FIFO被填满的时间*(w_clk - r_clk)大于数据包的传送时间=数据量 / 写入速度。

以下是网上整理到的资料:

首先,一定要理解清楚FIFO的应用场景,这个会直接关系到FIFO深度的计算,如果是面试官抛出的问题,那么有不清楚的地方,就应该进行询问。如果是笔试或者工程中需要计算FIFO深度的话,那么就需要自己考虑清楚。

其次,异步FIFO,读写时钟不同频,那么FIFO主要用于数据缓存,我们选择的FIFO深度应该能够保证在最极端的情况下,仍然不会溢出。因此考虑的前提一般都是写时钟频率大于读时钟频率,但是若写操作是连续的数据流,那么再大的FIFO都无法保证数据不溢出。因此可以认为这种情况下写数据的传输是“突发Burst”的,即写操作并不连续,设计者需要根据满标志控制或者自己来控制写操作的起止。

宏观地,从整个时间域上看,"写数据=读数据",这个条件必须要满足,如果这个大条件不满足的话,用FIFO是没有效果的。但是在发送方"突发"发送数据的时间T内,是很有可能写数据>读数据的,因此FIFO的深度要能够保证,在这段时间T内,如果接收方未能将发送方发送的数据接收完毕的话,剩下的数据都是可以存储在FIFO内部而且不会溢出的,那么在发送方停止发送数据的"空闲时隙"内,接收方可以从容地接收剩下来的数据。

写时钟周期w_clk,

读时钟周期r_clk,

写时钟周期里,每B个时钟周期会有A个数据写入FIFO

读时钟周期里,每Y个时钟周期会有X个数据读出FIFO

则,FIFO的最小深度是?

首先,这道题不一定有解

有解的必要条件是在一定时间内(足够长),写入的数据数量一定要等于读出的数据数量

因此有:A/B * w_clk = X/Y * r_clk

其次,算出写数据的最大burst_length。考虑最坏情况

比如,如果条件给出,每100个写时钟,写入80个数据,那么在背靠背的情况下,burst_length = 2*80=160

最后,fifo_depth = burst_length - burst_length * X/Y * r_clk/w_clk

BTW:通常,为了安全起见,都会多留一些depth的余度

个人觉得,公式应该是这样:

A/(B * w_clk) = X/(Y * r_clk)

fifo_depth = burst_length - burst_length * X/Y * w_clk /r_clk

举例说明:

如果100个写时钟周期可以写入80个数据,10个读时钟可以读出8个数据

其中w_ck=5ns,r_ck=10ns

如果按照之前的公式,得出的深度为:fifo_depth = burst_length - burst_length * X/Y * r_ck/w_clk=160-160*8/10*2=-94,显然是不对的

实际上,考虑背靠背(20个clk不发数据+80clk发数据+80clk发数据+20个clk不发数据的200个clk)

这样在中间160个写时钟周期连续写的情况下,只能读出160*5/(10*10)*8=64个数据,所以FIFO的深度应该为160-64=96

也就是fifo_depth = burst_length - burst_length * X/Y * w_clk /r_clk=160-160*8/10*5/10=96

9.同步异步电路分析

在同步电路设计中一般采用D触发器,异步电路设计中一般采用Latch。两者的最大的区别就在于,同步电路有统一的时钟,但是异步电路没有统一的时钟,

异步复位信号同步释放:其中的异步复位是指复位信号是异步有效的,即复位的发生与clk无关。后半句“同步释放”是指复位信号的撤除也与clk无关,但是复位信号是在下一个clk来到后起的作用(释放)。

10.各类存储器之间的区别(详见之前写的一篇博客的内容总结部分)。

11.对竞争冒险的理解,以及如何消除?

在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。产生毛刺叫冒险。如果布尔式中有相反的信号则可能产生竞争和冒险现象。解决方法:一是添加布尔式的消去项,二是在芯片外部加电容。

12分频器的设计(任意分频通用设计)

module square_generator#(parameter FREQ_WORD = 'd85899)

(LedCtlWordLocal,clk,rst_n,clk_outI,clk_outQ);

input LedCtlWordLocal;

input clk; //50MHz

input rst_n;//clock reset

output reg clk_outI,clk_outQ;

//--------------------------------------

reg [:] count='b1;

always@(posedge clk)

begin

count <= count + FREQ_WORD;

end

//--------------------------------------

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

clk_outI <= 'b1;

else

begin

if(count < 'h7FFF_FFFF)

clk_outI <= 'b1;

else

clk_outI <= LedCtlWordLocal;

if((count>'h3FFFFFFF)&&(count < 32'hbFFFFFFF))

clk_outQ <= 'b1;

else

clk_outQ <= LedCtlWordLocal;

end

end

endmodule

FPGA大疆考试准备内容的更多相关文章

- 【阿里聚安全·安全周刊】双十一背后的“霸下-七层流量清洗”系统| 大疆 VS “白帽子”,到底谁威胁了谁?

关键词:霸下-七层流量清洗系统丨大疆 VS "白帽子"丨抢购软件 "第一案"丨企业安全建设丨Aadhaar 数据泄漏丨朝鲜APT组织Lazarus丨31款违规A ...

- 小白学PID-以大疆M3508、M2006为例

前言: 最近用到了大疆的直流无刷(BLDC)减速电机M3508和M2006.做RoboMaster比赛的同学应该对它们很熟悉,这两款电机质量都不错,配套电调C620.C610功能强大,应用场景广泛.当 ...

- 大疆M3508、M2006必备CAN总线知识与配置方法

使用大疆M3508.M2006的CAN总线知识与配置方法 目录 使用大疆M3508.M2006的CAN总线知识与配置方法 前言: 0x00 需要额外的CAN收发器!!! 0x01 硬件层面分析 为什么 ...

- 双非本科进大疆(SP)!

哈喽,大家好,我是仲一.今天和大家分享的是一位优秀双非本科生上岸大疆的经历(羡慕哭了...). 今年4月底的时候,这位学弟和我分享了他拿下oppo,京东,联发科实习offer的经历,当时我还发了朋友圈 ...

- 企业私有源代码上传github致入侵之大疆案判决了

事件简单回顾: 1.2017年8月28日,大疆宣布“大疆威胁识别奖励计划”,最高3万美元: 2.然而在此之前,大疆农业事业部某员工将企业私有源代码上传到了github: 3.就职于大疆竞对公司Depa ...

- 让大疆去做测绘---航线规划软件APP

让大疆去做测绘---航线规划软件APP http://blog.zhulong.com/u10783270/blogdetail7162540.html RockyCapture无人机航线飞行控制软件 ...

- 大疆OSMO口袋云台相机惊艳上市!友商该如何是好。。。

2018.11.29 晚上更新: 下午看了大疆新出的口袋云台摄像机,感觉棒极了,于是我立刻去了京东下单预订了.目前是可以免息分期6个月就可以搞定了.‘ 大家敬请期待我的评测视频吧. ======== ...

- 大疆无人机 Android 开发总结——视频解码

DJI_Mobile_SDK是大疆为开发者提供的开发无人机应用的开发接口,可以实现对无人机飞行的控制,也可以利用无人机相机完成一些视觉任务.目前网上的开发教程主要集中于DJI 开发者社区,网上的资源非 ...

- 大疆2019校招FPGA笔试总结

1.对于同步fifo,每100个cycle可以写入80个数据,每10个cycle可以读出8个数据,fifo的深度至少为? 写时钟频率 w_clk, 读时钟频率 r_clk, 写时钟周期里,每B个时钟周 ...

随机推荐

- CENTOS YUM更新源

网络yum源和制作本地光盘yum源 配置CENTOS YUM更新源 yum安装rpm包安装后本地不清除的方法 sed -i 's#keepcache=0#keepcache=1#g' /etc/yum ...

- 2. 现代 javascript 新语法 及 对象专题

let , const 和 var javascript 里面的作用域 一个大括号 是一个作用域 { } var 会 在局部作用定义 被定义时 会提升作用域 如 if 的 {} 就属于 局部作用域 ...

- 配置window下python3环境

功能介绍 整理生信小知识库,一些技巧一些知识. 昨天 以下配置环境基于window操作系统,安装python3版本为例,推荐基础版配置. ! METHOD 1 (基础版) 官网下载对应电脑版本的p ...

- zabbix自定义邮件报警

1.启动动作 2.设定发件人邮箱 进入QQ邮箱: 通过短信验证开启如下服务,并生成授权码: 3.配置收件人

- python编程:从入门到实践----基础知识>第4章练习

4-1 比萨 :想出至少三种你喜欢的比萨,将其名称存储在一个列表中,再使用for 循环将每种比萨的名称都打印出来. a.修改这个for 循环,使其打印包含比萨名称的句子,而不仅仅是比萨的名称.对于每种 ...

- js运算符相关要点

取模运算的结果符号只与左边值的符号有关: var x = 7 % 3; // 结果为 1 var y = 7 % (-3); // 结果为 1 var z = (-7) % 3; // 结果为 -1

- 洛谷 P2622 关灯问题II【状压DP】

传送门:https://www.luogu.org/problemnew/show/P2622 题面: 题目描述 现有n盏灯,以及m个按钮.每个按钮可以同时控制这n盏灯--按下了第i个按钮,对于所有的 ...

- iTOP-4418开发板Qt Creator 编译注意事项

用“Qt Creator3.2.2”打开“qt4.7.1”环境下的工程文件可能会提示版本太旧.环境不匹 配导致程序无法编译,解决办法:建立新的工程把测试程序代码粘贴上去即可(界面需要自己 添加). 在 ...

- Rnotebook中用python画图

如果notebook需要转化为pdf, 能想到办法是保存图片文件,嵌入mardown语法中. 但是如果在html中显示, 可以考虑下面思虑, 比较取巧. ``` {python, engine.pat ...

- VB6的安装过程视频讲解

开发Windows桌面应用程序.开发Office的COM加载项,都离不开VB.本视频从VB安装包的下载和解压缩,一直讲到安装结束后创建项目为止.截图如下: 视频地址: https://pan.baid ...