USB小白学习之路(7) FPGA Communication with PC by CY7C68013,TD_init()解析

注:这个TD_Init()只对EP6进行了配置,将其配置成为Bluk_In端口,而没有对EP2进行配置。这篇文章直接把寄存器的图片贴上来了,看起来比较杂。感兴趣的可以看下一篇文章,是转自CSDN,对EP2和EP6都进行了配置,看起来更有条理。这个博客只对自己理解CY7C68013的配置有一定的帮助,对于配置CY7C68013,使其与FPGA通信,还是官方给的文档AN61345以及附件代码更详细直观。

void TD_Init(void)

{

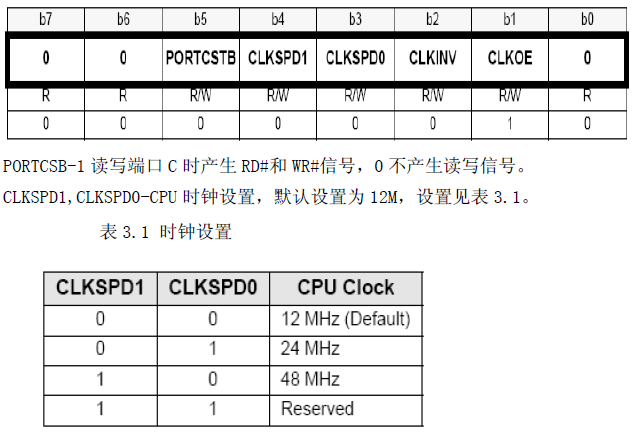

CPUCS = ((CPUCS & ~bmCLKSPD) | bmCLKSPD1); //设置CPU时钟频率为48M,寄存器CPUCS的位如下所示。此语句就是将CPUCS的b4,b3位设为10,

//同时不改变其他bit。

图1 寄存器CPUCS的描述

//USBCS = Ox80; //set high speed mode 添加此语句时工程编译不通过

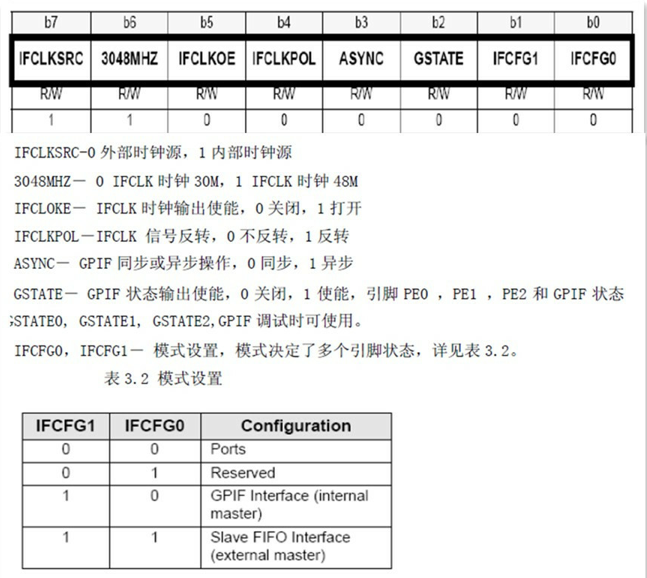

IFCONFIG = 0XCB; //选择内部时钟频率为48M,FIFO/GPIF采用异步操作模式,SLAVE FIFO接口(外部主控制器)

//IFCONFIG寄存器的描述如图2所示,0xCB = 1100_1011,可见:

//内部时钟,48MHz,IFCLK时钟输出关闭,IFCLK信号不翻转,GPIF异步操作,关闭GPIF输出,slave FIFO接口

图2 寄存器IFCONFIG的描述

SYNCDELAY; //里面是空语句,延时用

//REVCTL = 0X03; //0x01 //版本号,控制版本号的,不重要,不用管

//SYNCDELAY;

FIFOPINPOLAR = 0X00; //所有引脚为低电平有效,此寄存器控制Slave FIFO方式信号有效电平

SYNCDELAY; //FIFOPINPOLAR寄存器的描述如图3所示

图3 寄存器FIFOPINPOLAR的描述

$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$

$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$

FIFORESET = 0X80; //对从主机发送的数据进行握手

SYNCDELAY; //FIFORESET寄存器的描述如图4所示。由图4中可以看出,这里写入0x80是为了保证复位正常。

图4 寄存器FIFORESET的描述

FIFORESET = 0X02; //复位FIFO

SYNCDELAY;

FIFORESET = 0X04; //复位FIFO

SYNCDELAY;

FIFORESET = 0X06; //复位FIFO

SYNCDELAY;

FIFORESET = 0X08; //复位FIFO

SYNCDELAY;

//由图4可以看出,这四条语句分别复位端点:EP2,EP4,EP6,EP8

FIFORESET = 0X00; //保存操作,这里也是由图4可以得到,写入0x00是为了使能相应请求。

SYNCDELAY;

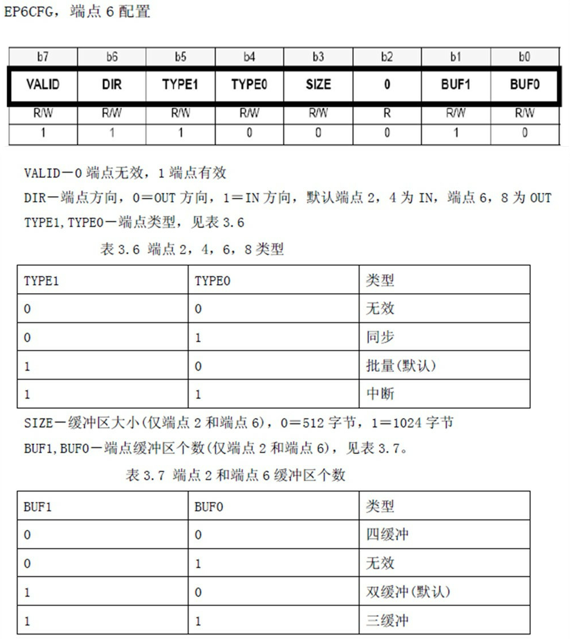

EP6CFG =0xE0; //使能端点6,端点方向为输入,块传输方式,端点大小512字节,端点为4重缓冲

SYNCDELAY; //EP6CFG寄存器的描述如图5所示,0xE0 = 1110_0000;

图5 寄存器EP6CFG的描述

EP6FIFOCFG = 0X0C; // AUTOIN=1 ZEROLEN=1 WORDIDE=0 设置端点6为自动输入,选择总线数据宽度为8位

SYNCDELAY; //EP6FIFOCFG 寄存器的描述如图6所示。0x0C = 0000_1100;

图6 寄存器EP6FIFOCFG的描述

PINFLAGSAB = 0X00; //确定引脚FLAGA为EPX的PF标志,FLAGB为EPX的EF标志,FLAGC为EPX的FF标志///

SYNCDELAY; //PF表示FIFO编程标志,EF表示FIFO已空,FF表示FIFO已满

PINFLAGSCD = 0X00; //确定引脚FLAGA为EPX的PF标志,FLAGB为EPX的EF标志,FLAGC为EPX的FF标志///

SYNCDELAY; //PINFLAGSAB寄存器的描述如图7所示。

图7 寄存器PINFLAGSAB和PINFLAGSCD的描述

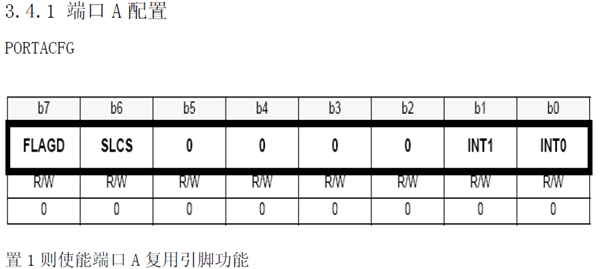

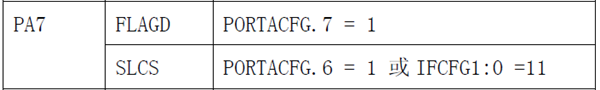

PORTACFG = 0X40; //PORTACFG.6=1 设置IOPA7为CS引脚

SYNCDELAY; //PORTACFG寄存器的描述如图8所示,图9为Port A复用的描述

图8 寄存器PORTACFG的描述

图9 Port A的复用功能

EP6AUTOINLENH = 0X02; //端点6 AUTOIN包长度高字节

SYNCDELAY;

EP6AUTOINLENL = 0X00; //端点6 AUTOIN包长度高字节

SYNCDELAY; //这里就是包长度的寄存器,由这两个寄存器可以得到,包长度为512Byte,这里设置包长度要小于前面设置的EP6CFG中缓冲区的大小

EP6BCH = 0x02; //512byte///*

SYNCDELAY;

EP6BCL = 0x00; //512byte///*

SYNCDELAY; //这两个是端点的计数寄存器,这里往里写入是为了触发

EP6FIFOPFH = 0X80; //端点6/SLAVE FIFO 可编程成级标志的高位(高速方式和全速方式)//不懂///

SYNCDELAY;

EP6FIFOPFL = 0X00; //端点6/SLAVE FIFO 可编程成级标志的高位(高速方式和全速方式) //不懂///

SYNCDELAY;

OUTPKTEND =0X82; //启动OUT缓冲区

SYNCDELAY;

OUTPKTEND =0X82; //启动OUT缓冲区

SYNCDELAY;

//AUTOPTRSETUP |= 0x01; //使能自动指针

Rwuen = TRUE; //睡眠唤醒,控制主函数睡眠中的死循环结束。

}

USB小白学习之路(7) FPGA Communication with PC by CY7C68013,TD_init()解析的更多相关文章

- USB小白学习之路(10) CY7C68013A Slave FIFO模式下的标志位(转)

转自良子:http://www.eefocus.com/liangziusb/blog/12-11/288618_bdaf9.html CY7C68013含有4个大端点,可以用来处理数据量较大的传输, ...

- USB小白学习之路(8)FX2LP cy7c68013A——Slave FIFO 与FPGA通信(转)

此博客转自CSDN:http://blog.csdn.net/xx116213/article/details/50535682 这个博客只对自己理解CY7C68013的配置有一定的帮助,对于配置CY ...

- USB小白学习之路(11) Cy7c68013A驱动电路设计注意事项(转)

Cy7c68013A驱动电路设计注意事项 转自:http://group.chinaaet.com/116/79029#0-tsina-1-71467-397232819ff9a47a7b7e80a4 ...

- USB小白学习之路(12) Cy7c68013A固件之Slave FIFO(转)

Cy7c68013固件之Slave FIFO 转自:http://blog.csdn.net/zengshaoqing/article/details/53053539 选择SlaveFIFO传输方式 ...

- USB小白学习之路(5) HID鼠标程序

HID鼠标程序 1. 特别注意 需要特别注意,各个例程中的设备描述符,配置描述符等各种描述符都是已经配置好了的,我们需要做的只是在例程中将代码修改为自己需要的部分即可,一般情况下是不可以串搭配的. 2 ...

- USB小白学习之路(4)HID键盘程序

HID键盘程序 1. 特别注意 需要特别注意,各个例程中的设备描述符,配置描述符等各种描述符都是已经配置好了的,我们需要做的只是在例程中将代码修改为自己需要的部分即可,一般情况下是不可以串搭配的. 2 ...

- USB小白学习之路(3) 通过自定义请求存取外部RAM

通过自定义请求存取外部RAM 1. 实验简述 此实验是对自定义的供应商特殊命令(vendor specific command bRequest = 0xA3)进行解析,程序中的read me说明如下 ...

- USB小白学习之路(2)端点IN/OUT互换

端点2(out)和端点6(in)的out_in互换 注:这里的out和in都是以host为标准说的,out是host的out,在设备(Cy7c68013)这里其实是输入端口:in是host的in,在设 ...

- USB小白学习之路(1) Cypress固件架构解析

Cypress固件架构彻底解析及USB枚举 1. RAM的区别 56pin或者100pin的cy7c68013A,只有内部RAM,不支持外部RAM 128pin的cy7c68013A在pin脚EA=0 ...

随机推荐

- 黑科技如何制造人类V2.0?

黑科技泛指人类尚未成熟但具有巨大潜力的科学技术,智能手机.大数据.扫码支付.电子地图等等都曾属于黑科技范畴,随着时间的推移,它们慢慢成熟,且展现出巨大的能力,影响人类进程,最终黑科技转变成人类伟大的创 ...

- windows 环境下Maven私服搭建

使用Nexus.3.11在Windows环境上搭建1.下载nexus.3.11.zip包https://www.sonatype.com/download-oss-sonatype 下载下来之后,进行 ...

- ZOJ-1610 Count the Colors(线段树染色,求染色段)

http://acm.zju.edu.cn/onlinejudge/showProblem.do?problemCode=1610 https://vjudge.net/contest/318019# ...

- 混合欧拉回路poj 1637 Sightseeing tour

把该图的无向边随便定向,计算每个点的入度和出度.如果有某个点出入度之差为奇数,那么肯定不存在欧拉回路.因为欧拉回路要求每点入度 = 出度,也就是总度数为偶数,存在奇数度点必不能有欧拉回路: 好了,现在 ...

- 让mybatis不再难懂(一)

与hibernate相比,我无疑更喜欢mybatis,就因为我觉得它真的好用,哈哈.它简单上手和掌握:sql语句和代码分开,方便统一管理和优化:当然缺点也有:sql工作量很大,尤其是字段多.关联表多时 ...

- OfficeCommandbarViewer20171005.rar

OfficeCommandbarViewer用于查看Office各组件工具栏和控件信息的一款软件. 采用了本地XML文件的方式,所以使用本工具不需要提前打开任何Office组件. 动态图: 下载地址: ...

- StartDT_AI_Lab | 开启“数据+算法”定义的新世界

继「数据中台技术汇」栏目推出以来,获得了不少技术极客的喜爱.作为AI驱动的数据中台创导者,深度关注核心算法技术的自研创新.融合探索,故推出全新AI算法栏目「StartDT_AI_Lab」,主要介绍算法 ...

- 构造函数中可以进行if判断

- C# 将多个DataTable添加到指定的DataSet中

DataSet ds = new DataSet();//创建数据集 DataTable dt1=new DataTable(); //表1 DataTable dt2 = new DataTable ...

- LabVIEW部分视觉函数中文解说

IMAQ Learn Pattern 2 VI 在匹配阶段创建您要搜索的图案匹配的模板图像的描述,此描述的数据被附加到输入模板图像中.在匹配阶段,从模板图像中提取模板描述符并且用于从检查图像中搜索模板 ...