verilog HDL -模块代码基本结构

1--verilog HDL 语言的预编译指令作用:指示在编译verliog HDL源代码前,需要执行哪些操作。

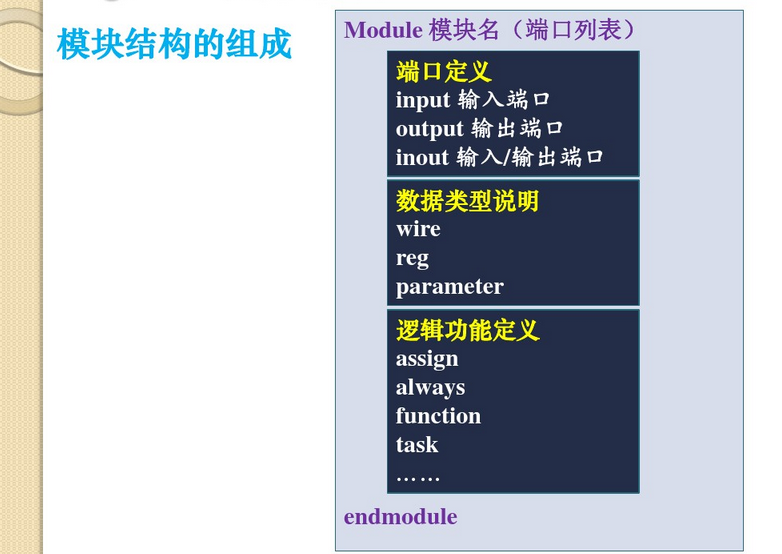

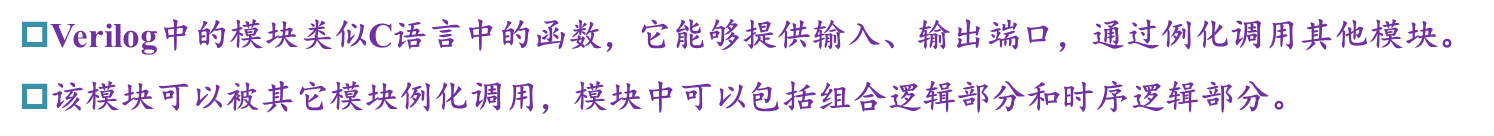

2--模块内容是嵌在module 和endmodule两个语句之间。每个模块实现特定的功能,模块可进行层次的嵌套,因此可以将大型的数字电路设计分割成大小不一的小模块来实现特定的功能,最

后通过由顶层模块调用子模块来实现整体功能。

3--模块包括接口描述部分和逻辑功能描述部分。这可以把模块与器件相类比。

4-verilog hdl语言支持的并行语句主要有一下四种:

连续赋值语句

模块实例化语句

initial语句

always语句

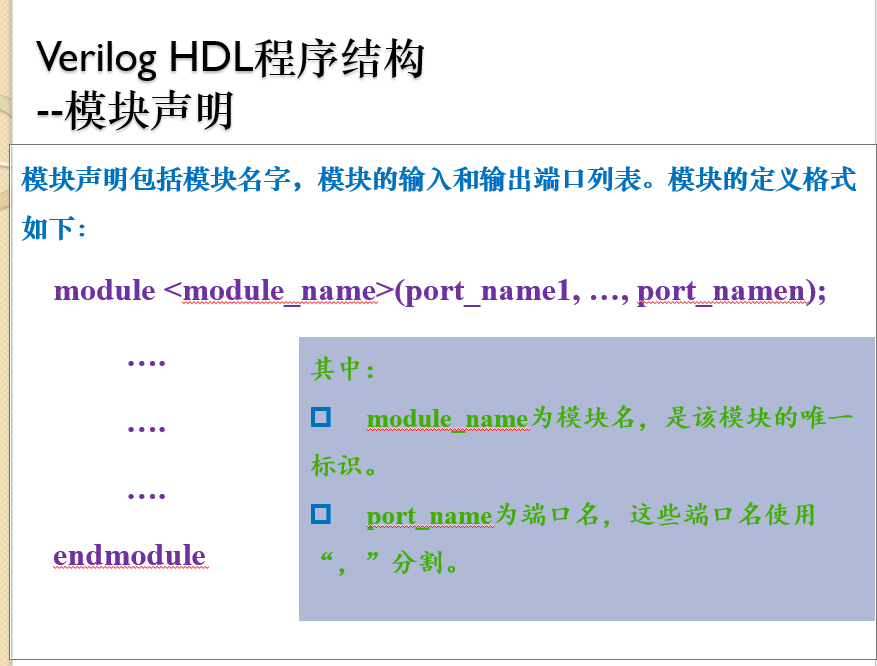

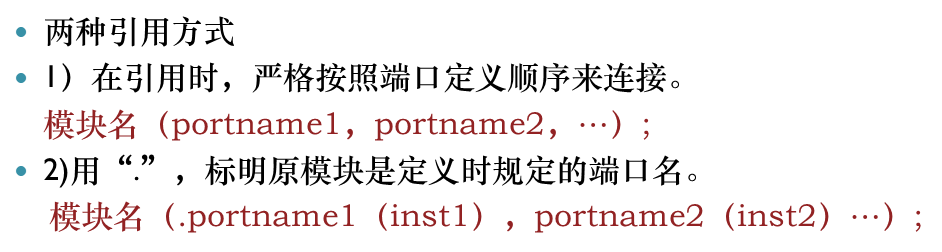

模块引用方式:

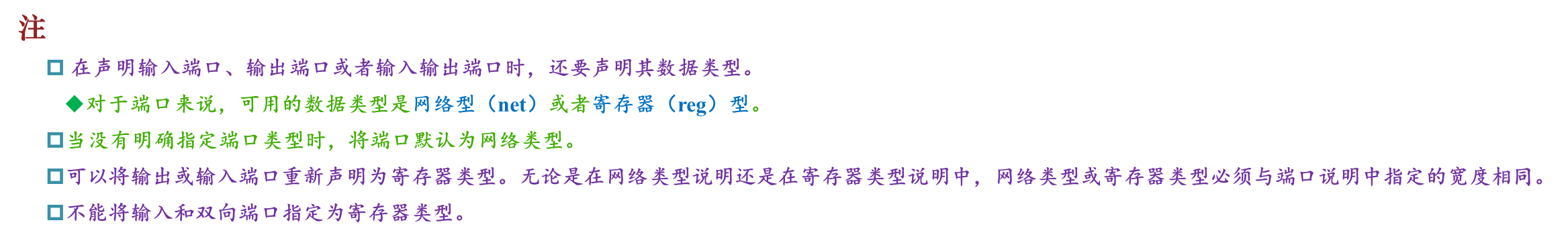

端口定义:

事件:当线网型或寄存器型信号的值发生变化时,对电路来说就是产生了一个事件,就需要进行相应的计算。

事件在代码中以@(时间列表)形式出现,事件列表可以有多个,用or分开,也可以用“,”分开,他们之间是“或”的关系。也就是说只要有一个事件产生,就会执行进程语句。事件分为电平信号和边沿信号两种。(posedge:上升沿事件,negedge:下降沿事件。)

【进程:行为模型的本质是进程。一个进程可以被看做是一个独立的运行单元,它可能很简单,也可能很复杂,我们可以将数字系统的行为看作很多有机结合的进程的集合。

在Verilog HDL中,描述进程的基本语句是always和initial。Always过程反复执行其中的块语句,而initial过程中的语句块只执行一次。除了always和initial过程块外,一个assign赋值语句、一个实例元件的调用都可以看作是一个进程。

进程的特点:

1-进程只有两种状态,即执行态和等待状态。进程是否进入执行态,取决于是否满足特定的条件,如敏感变量是否发生变化。一旦满足条件,进程即进入执行状态。当该进程执行完毕或遇到停止语句后,即停止执行,自动返回到起始语句,进入等待状态。

2-进程一般由敏感信号的变化来启动

3-各个进程之间通过信号线进行通信。多个进程之所以能同步并发运行,一个很重要的原因就是有进程之间的信号线的通信和协议。

4-一个进程中只允许描述对应于一个时钟信号的同步时序逻辑。

5-进程之间是并发执行的。两个或更多个“always”过程块、“assign”持续赋值语句、实例元件调用等操作都是同时执行的。】

always语句:(可综合)

特点:

1-循环执行

2-可综合

【综合:将用行为和功能层表达的电子系统转换成低层次的便于具体实现的模块组合装备的过程。

综合过程将把软件设计的HDL描述与硬件结构挂钩,是将软件转化为硬件电路的关键步骤,是文字描述与硬件相结合的一座桥梁。综合就是将电路的高级语言(如行为描述)转化为低级的,可以FPGA/CPLD的基本结构相映射的网表文件或程序。

当输入的hdl文件在eda工具中检测无误后,首选面临的就是逻辑综合,因此要求hdl源文件中的语句都是可综合的。】

3-必须有时序控制

4-在0时刻开始执行,可以有一条或者多条顺序语句。

使用方法:

语法格式:always

[时序控制]顺序语句;

时序控制可以是以时间刻度为单位的时间延时数字,也可以是信号变化事件条件。

当顺序语句有多条时,可以使用“begin”-“end”字符对进行组织。

【begin -- end就是一个模块 (相当于 C语音的一段程序)的起始和结束的标记。非常类似于 C语言中的 大括号 ({……})。】

注意:在不同的always逻辑块中,对同一个reg变量进行赋值,会冲突导致报错!

赋值操作符:

意义是更新被赋值数据对象的值。

1,赋值操作符 <=:

该操作符在进程块中使用,是非阻塞赋值,由于在进程中使用,所以被赋值的数据对象必须是reg型。

2,赋值操作符=:

该操作符在进程或者assign连续赋值语句中使用。被赋值数据对象可以是reg型或wire型,其中在进程块中的赋值方式是阻塞赋值。

*********************************************************************************************************************************************************

学习了上面的知识点,应该就能看懂下面的代码了。

'timescale 1ns/1ps //预编译指令定义了时间单位为1ns,时间精度为1ps module led_test(clk,rst_n,led); input clk;

input rst_n;

output [:] led; //寄存器型数据对象的定义

reg [:] timer;

reg [:] led; always @(posedge clk or negedge rst_n)

begin

if(~rst_n)

timer <=;

else if(timer=='d199_999_999)

timer<=;

else

timer<=timer+'b1;

end always @(posedge clk or negedge rst_n)

begin

if(~rst_n)

led<='b0000;

else if(timer=='d49_999_999)

led<='b0001;

else if(timer=='d99_999_999)

led<='b0010;

else if(timer=='149_999_999)

led<='b0100;

else if(timer=='d199_999_999)

led<='b1000;

end endmodule

ok,今天的学习结束!

verilog HDL -模块代码基本结构的更多相关文章

- Verilog HDL基础语法讲解之模块代码基本结构

Verilog HDL基础语法讲解之模块代码基本结构 本章主要讲解Verilog基础语法的内容,文章以一个最简单的例子"二选一多路器"来引入一个最简单的Verilog设计文件的 ...

- Verilog HDL模块的结构

一个设计是由一个个模块(module)构成的.一个模块的设计如下: 1.模块内容是嵌在module 和endmodule两个语句之间.每个模块实现特定的功能,模块可进行层次的嵌套,因此可以将大型的数字 ...

- 自己动手写处理器之第二阶段(2)——Verilog HDL简单介绍

将陆续上传本人写的新书<自己动手写处理器>(尚未出版),今天是第六篇.我尽量每周四篇 2.3 Verilog HDL简单介绍 本书实现的OpenMIPS处理器是使用Verilog HDL编 ...

- 你知道Verilog HDL程序是如何构成的吗

本节通过硬件描述语言Verilog HDL对二十进制编码器的描述,介绍Verilog HDL程序的基本结构及特点. 二十进制编码器及Verilog HDL描述 二十进制编码器是数字电路中常用的电路单元 ...

- Verilog HDL的程序结构及其描述

这篇博文是写给要入门Verilog HDL及其初学者的,也算是我对Verilog HDL学习的一个总结,主要是Verilog HDL的程序结构及其描述,如果有错,欢迎评论指出. 一.Verilog ...

- 浅谈Verilog HDL代码编写风格

消失了好久,没有写文章,也没有做笔记,因为最近再赶一个比赛,时间很紧,昨天周六终于结束了,所以趁着周末这会儿有时间,写点东西,记录下来.首先我学习FPGA才一年多,我知道自己没有资格谈论一些比较深层次 ...

- 基于Verilog HDL 的数字时钟设计

基于Verilog HDL的数字时钟设计 一.实验内容: 利用FPGA实现数字时钟设计,附带秒表功能及时间设置功能.时间设置由开关S1和S2控制,分别是增和减.开关S3是模式选择:0是正常时钟 ...

- FPGA Verilog HDL 系列实例--------步进电机驱动控制

[连载] FPGA Verilog HDL 系列实例 Verilog HDL 之 步进电机驱动控制 步进电机的用途还是非常广泛的,目前打印机,绘图仪,机器人等等设备都以步进电机为动力核心.那么,下面我 ...

- 写自己的第二级处理器(3)——Verilog HDL行为语句

我们会继续上传新书<自己动手写处理器>(未公布),今天是第七章,我每星期试试4 2.6 Verilog HDL行为语句 2.6.1 过程语句 Verilog定义的模块一般包含有过程语句,过 ...

随机推荐

- 62.纯 CSS 创作一只蒸锅(感觉不好看呀)

原文地址:https://segmentfault.com/a/1190000015389338 HTML code: <!-- steamer: 蒸锅: lid: 盖子: pot: 锅 --& ...

- java——IO流01

移动文件有一种简单方法,不需要复制文件再删除文件. package com.unir.test01; import java.io.File; import java.io.IOException; ...

- linux上用route添加/删除路由

1. 查看 route -n 2. 添加 route add -net 9.123.0.0 netmask 255.255.0.0 gw 9.123.0.1 3. 删除 route del -net ...

- Sphinx 安装与使用

Sphinx 优点 高速索引(接近10M/S) 高速搜索(2-4G文本搜索耗时不到0.1秒) 高可用性(单CPU支持100GB文本,100M文档) 提供相关性排名.分布式搜索.文档摘要(高亮显示) S ...

- BP神经网络与Python实现

人工神经网络是一种经典的机器学习模型,随着深度学习的发展神经网络模型日益完善. 联想大家熟悉的回归问题, 神经网络模型实际上是根据训练样本创造出一个多维输入多维输出的函数, 并使用该函数进行预测, 网 ...

- TCP与UDP,可靠UDP如何实现

两种协议都是传输层协议,为应用层提供信息载体. TCP协议是基于连接的字节流的可靠协议,有三次握手,四次挥手,超时重传,流量控制(滑动窗口),拥塞控制和差错控制,也正因为有可靠性的保证和控制手段,所以 ...

- (译)内存沉思:多个名称相关的神秘的SQL Server内存消耗者。

原文出处:https://blogs.msdn.microsoft.com/sqlmeditation/2013/01/01/memory-meditation-the-mysterious-sql- ...

- P1880 [NOI1995]石子合并-(环形区间dp)

https://www.luogu.org/problemnew/show/P1880 解题过程:本次的题目把石子围成一个环,与排成一列的版本有些不一样,可以在后面数组后面再接上n个元素,表示连续n个 ...

- Java 学习笔记提高篇

Java笔记(提高篇)整理 主要内容: 面向对象 异常 数组 常用类 集合 IO流 线程 反射 Socket编程 1. 面向对象 1.1包 用来管理Java中的类, 类似文件夹管理文件一样. 因 ...

- ProxyHandler处理器(代理设置)

很多网站会检测某一段时间某个IP的访问次数(通过流量统计,系统日志等),如果访问的次数多得不像正常人,它会禁止这个IP的访问. 所以我们可以设置一些代理服务器,每个一段时间换一个代理,就算IP被禁止, ...