你知道Verilog HDL程序是如何构成的吗

本节通过硬件描述语言Verilog HDL对二十进制编码器的描述,介绍Verilog HDL程序的基本结构及特点。

二十进制编码器及Verilog HDL描述

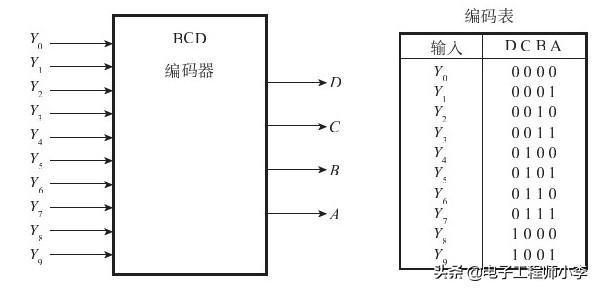

二十进制编码器是数字电路中常用的电路单元,它的输入是代表0~9这10个输入端的状态信息。输入信号为高电平时,输出相应的BCD码,因此也称为10线4线编码器。其功能表及电路符号如图3-1所示。

图3-1 二十进制编码器

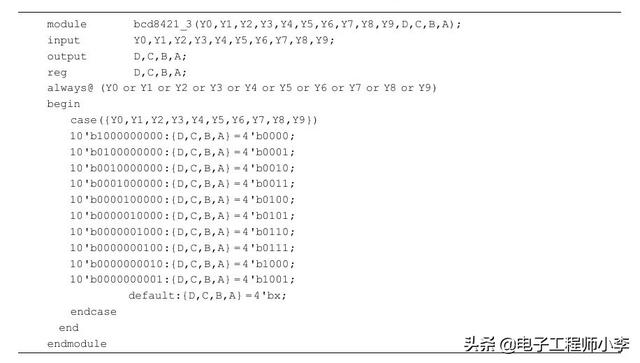

【例3-1】利用Verilog HDL对二十进制编码器进行设计。

Verilog HDL程序的基本构成

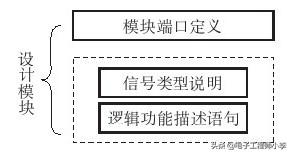

从例3-1可以看出,一个完整的Verilog HDL程序由3个基本部分构成,分别是:模块端口定义部分、信号类型说明部分和逻辑功能描述语句部分。其结构图如3-2所示。

图3-2 Verilog HDL程序基本结构

模块端口定义部分

对于硬件描述语言来说,一个程序代表了一个具有某种逻辑功能的电路,模块端口定义部分描述了该电路的接口部分的信息,即输入输出信号的信息。

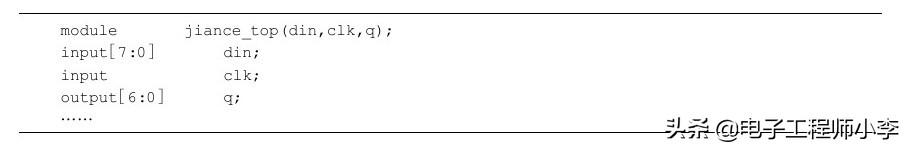

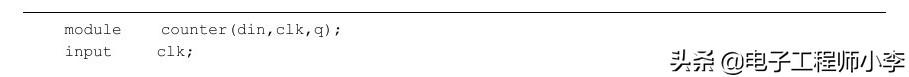

模块端口定义部分的语法结构如下:

module模块名(端口信号1,端口信号2,端口信号3,端口信号4,……);

input[width:0]端口信号1,端口信号3,……;

output[width:0]端口信号2,端口信号4,……;

程序以关键词module引导,模块名是设计者对于设计的电路所取的名字,在模块端口定义的第1行列出了所有进出该电路模块的端口信号,在第2行和第3行中定义了各端口信号流动方向。流动方向包括输入(input)、输出(output)和双向(inout),[width:0]表示信号的位宽,如果位宽没有特别说明,则系统默认为1位宽度。

【例3-2】模块端口定义举例。

信号类型说明部分

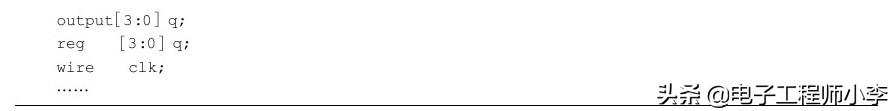

在Verilog HDL语法中,信号共有两种数据类型,分别为:网线类型(net型)和寄存器类型(register型)。在信号类型说明部分除了要对输入/输出端口的信号类型进行说明之外,还要对程序中定义的中间量的数据类型进行说明。

信号类型说明部分的语法结构如下:

wire[width:0]信号1,信号2,……;

reg[width:0]信号3,信号4,……;

【例3-3】信号类型说明举例。

逻辑功能描述语句部分

逻辑功能描述语句部分对输入/输出信号之间的逻辑关系进行了描述,是Verilog HDL程序设计中最主要的部分,在电路上相当于器件的内部电路结构。在Verilog HDL语言中,常用的逻辑功能描述语句可以分为以下3种:

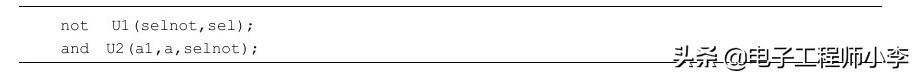

例化语句:调用已进行元件化封装的程序。这种语句常应用于层次化设计的顶层文件设计中。

【例3-4】例化语句举例。

该语句分别调用了一个非门和与门电路模块。

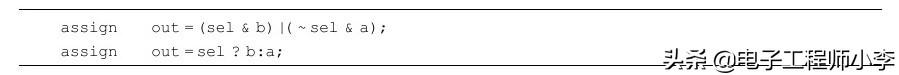

连续赋值语句:描述信号之间简单的赋值关系。在连续赋值语句中,右边表达式使用的操作数无论何时发生变化,右边表达式都重新计算。这类描述通常以关键词assign引导。

【例3-5】连续赋值语句举例。

该语句描述了输出信号与输入信号的赋值关系。

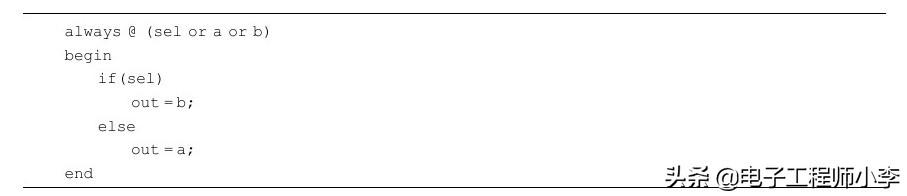

过程语句:以关键词always、initial等关键词引导的语句,描述了一定条件下信号之间的赋值关系。这种变量数据被赋值后,其值保持不变,直到下一次条件具备时对它们重新赋值。

【例3-6】过程语句举例。

与连续赋值语句一样,always和initial也描述了输出信号与输入信号的赋值关系,但是这种赋值往往是一种比较复杂的条件赋值,例如,例3-6就用了if……else语句描述了输出信号与输入信号的条件关系。

本文转自小平头电子技术社区:https://www.xiaopingtou.cn/article-104211.html嵌入式,物联网,硬件PCB,电子技术尽在小平头

你知道Verilog HDL程序是如何构成的吗的更多相关文章

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- 【转】Verilog HDL常用建模方式——《Verilog与数字ASIC设计基础》读书笔记(四)

Verilog HDL常用建模方式——<Verilog与数字ASIC设计基础>读书笔记(四) Verilog HDL的基本功能之一是描述可综合的硬件逻辑电路.所谓综合(Synthesis) ...

- Verilog HDL的程序结构及其描述

这篇博文是写给要入门Verilog HDL及其初学者的,也算是我对Verilog HDL学习的一个总结,主要是Verilog HDL的程序结构及其描述,如果有错,欢迎评论指出. 一.Verilog ...

- 关于初次使用Verilog HDL语言需要懂的基本语法

关于初次使用Verilog HDL语言需要懂的基本语法 1.常量 数字表达式全面的描述方式为:<位宽><进制><数字> 8’b10101100,表示位宽为8的二进制 ...

- 写自己的第二级处理器(3)——Verilog HDL行为语句

我们会继续上传新书<自己动手写处理器>(未公布),今天是第七章,我每星期试试4 2.6 Verilog HDL行为语句 2.6.1 过程语句 Verilog定义的模块一般包含有过程语句,过 ...

- 如何高效的编写Verilog HDL——进阶版

博主之前写过一篇文章来谈论如何高效的编写Verlog HDL——菜鸟版,在其中主要强调了使用Notepad++来编写Verilog HDL语言的便捷性,为什么说是菜鸟版呢,因为对于新手来说,在还没有熟 ...

- verilog HDL -模块代码基本结构

1--verilog HDL 语言的预编译指令作用:指示在编译verliog HDL源代码前,需要执行哪些操作. 2--模块内容是嵌在module 和endmodule两个语句之间.每个模块实现特定的 ...

- Verilog HDL与C语言的比较

Verilog HDL与C语言的比较 Verilog HDL是在C语言的基础上发展起来的,因而它保留了C语言所独有的结构特点. 为便于对Verilog HDL有个大致的认识,在这里将它与C语言的异 ...

- 自己动手写处理器之第二阶段(2)——Verilog HDL简单介绍

将陆续上传本人写的新书<自己动手写处理器>(尚未出版),今天是第六篇.我尽量每周四篇 2.3 Verilog HDL简单介绍 本书实现的OpenMIPS处理器是使用Verilog HDL编 ...

随机推荐

- VMware 14 激活密钥

VMware 14 激活密钥 FF31K-AHZD1-H8ETZ-8WWEZ-WUUVA CV7T2-6WY5Q-48EWP-ZXY7X-QGUWD

- python中的while

while循环 循环就是一个重复的过程,不断的重复.while循环又称条件循环 while 条件: code 1 code 2 code 3 ... ##实现ATM的输入密码重新输入的功能 while ...

- 吴裕雄 python 机器学习——模型选择参数优化随机搜索寻优RandomizedSearchCV模型

import scipy from sklearn.datasets import load_digits from sklearn.metrics import classification_rep ...

- 外置ADC

美信关于如何简化微控制器与温度传感器的接口设计?: 一般外置ADC与单片机UC之间通过SPI或SMBUS接口通信 当IO口比较紧张时可以选择脉冲或频率方波正比与测量值输出的外置ADC,此时也可以实现光 ...

- tp5的输入和验证

规则和模板 好像要写一样名字,只需要引入模板

- centos7下安装pcre库(pcretest)

在linux下需要对正则表达式的验证,使用的验证工具是pcretest,这个工具集成在pcre库中,下面是安装教程. 安装环境是centos7. 1)首先去官网下载压缩包文件. 其他的source网站 ...

- Windows事件ID

51 Windows 无法找到网络路径.请确认网络路径正确并且目标计算机不忙或已关闭.如果 Windows 仍然无法找到网络路径,请与网络管理员联系. 52 由于网络上有重名,没有连接.请到“控制面板 ...

- acm数论之旅(转载)--素数

https://www.cnblogs.com/linyujun/p/5198832.html 前言:好多学ACM的人都在问我数论的知识(其实我本人分不清数学和数论有什么区别,反正以后有关数学的知识我 ...

- MDC 输出线程信息帮助定位问题

log4j中的%x ---NDC,%X---MDC 即%x NDC.clear();NDC.push(this.toString());%X{first} %X{last}MDC.put(" ...

- ZOJ1004 Anagrams by Stack

题目大意:规定 i 为入栈,o 为出栈,现在给两个字符串st1,st2,现在要将st1转化为st2,转化方法是,st1中字符从头开始入栈,并合理出栈构造出st2.请输出所有可能的出入栈步骤. 深度优先 ...