FIFO的设计与仿真

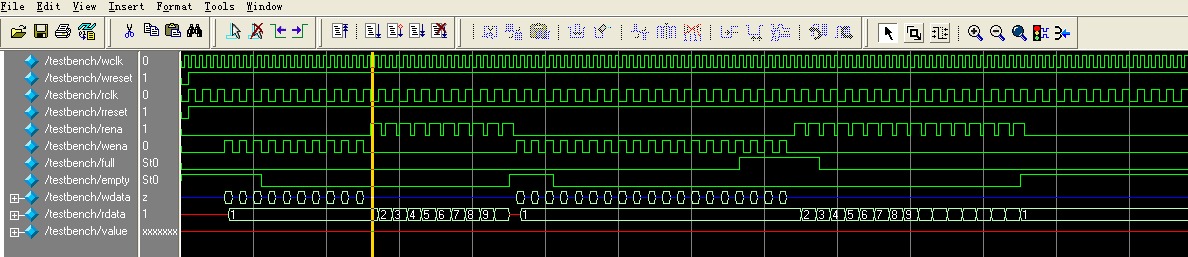

本设计参照齐威王大哥的设计,采用模块化的设计方法,每个模块简单易懂,并进行了每个模块的仿真。最后进行顶层设计,编写了测试激励在modisim上仿真正确,

下面给出代码和测试激励,附上一篇比较好的英文文献。

1 module yibu_fifo(wclk,wreset,wdata,wena,rclk,rena,rdata,rreset,full,empty);

2 parameter DSIZE = 8,

3 ASIZE = 4;

4 input wclk,wreset,rclk,rreset;

5 input wena,rena; //写控制信号 读控制信号

6 input [DSIZE-1:0] wdata; //写数据

7 output[DSIZE-1:0] rdata; //读数据

8 output full,empty ;//写满 读空

9 wire [ASIZE:0] wzz, wzz_syn,rzz,rzz_syn; //特别注意

10 wire [ASIZE-1:0] raddr,waddr; //特别注意

11 fifomem U1(rdata, wdata, waddr, raddr, wena,full, wclk);

12 w_full U2(full, waddr, wzz, rzz_syn, wena, wclk, wreset);

13 r_empty U3(empty, raddr, rzz, wzz_syn, rena, rclk, rreset);

14 syn_w2r U4(wzz,rclk,rreset,wzz_syn);

15 syn_r2w U5(wclk,wreset,rzz,rzz_syn);

16 endmodule

module fifomem (rdata, wdata, waddr, raddr, wena,full, wclk);

parameter DSIZE = 8,

ASIZE = 4;

input wclk;

input [DSIZE-1:0] wdata;

input wena,full;

output [DSIZE-1:0] rdata;

input [ASIZE-1:0] waddr;

input [ASIZE-1:0] raddr;

reg [DSIZE-1:0] mem[0:(1<<ASIZE)-1]; //register

assign rdata=mem[raddr]; //read

always @(posedge wclk) //write

if (wena && !full)

mem[waddr] <= wdata;

endmodule

module r_empty(empty, raddr, rzz, wzz_syn, rena, rclk, rreset);

parameter DSIZE = 8,

ASIZE = 4; //

input rclk, rreset,rena;

input [ASIZE:0] wzz_syn;

output [ASIZE:0] rzz;

output [ASIZE-1:0] raddr;

output empty;

reg empty;

reg [ASIZE:0] rzz;

reg [ASIZE:0] rbin;

wire [ASIZE:0] rgraynext,rbinnext;

//-------------empty产生与raddr产生-------------------

always @(posedge rclk or negedge rreset) // GRAYSTYLE2 pointer

begin

if (!rreset)

{rbin, rzz} <= 0;

else

{rbin, rzz} <= {rbinnext, rgraynext};

end

// Memory read-address pointer (okay to use binary to address memory)

assign raddr = rbin[ASIZE-1:0];

assign rbinnext = rbin + (rena & ~empty);

assign rgraynext = (rbinnext>>1) ^ rbinnext; // FIFO empty when the next rptr == synchronized wptr or on reset

assign rempty_val = (rgraynext == wzz_syn);

always @(posedge rclk or negedge rreset)

begin

if (!rreset)

empty <= 1'b1;

else

empty <= rempty_val;

end

endmodule

module w_full(full, waddr, wzz, rzz_syn, wena, wclk, wreset);

parameter DSIZE = 8,

ASIZE = 4;

input wclk,wreset;

input wena;

input [ASIZE:0] rzz_syn;

output [ASIZE:0] wzz;

output full;

output [ASIZE-1:0] waddr;

reg full;

reg [ASIZE:0] wzz;

reg [ASIZE:0] wbin;

wire [ASIZE:0] wgraynext,wbinnext;

//---------------full产生与waddr产生--------------------

always @(posedge wclk or negedge wreset)

if (!wreset)

{wbin, wzz} <= 0;

else

{wbin, wzz} <= {wbinnext, wgraynext};

// Memory write-address pointer (okay to use binary to address memory)

assign waddr = wbin[ASIZE-1:0];

assign wbinnext = wbin + (wena & ~full); assign wgraynext = (wbinnext>>1) ^ wbinnext; //bin to g

assign wfull_val = (wgraynext=={~rzz_syn[ASIZE:ASIZE-1], rzz_syn[ASIZE-2:0]}); // full always @(posedge wclk or negedge wreset)

if (!wreset)

full <= 1'b0;

else

full <= wfull_val;

endmodule

module syn_r2w(wclk,wreset,rzz,rzz_syn);

parameter DSIZE = 8,

ASIZE = 4;

input wclk,wreset;

input [ASIZE:0] rzz;

output [ASIZE:0] rzz_syn;

reg [ASIZE:0] rzz_syn;

reg [ASIZE:0] rzz_syn_1; //两级同步

always @(posedge wclk or negedge wreset)

if(!wreset)

{rzz_syn,rzz_syn_1} <= 0;

else

{rzz_syn,rzz_syn_1} <= {rzz_syn_1,rzz};

endmodule

module syn_w2r (wzz,rclk,rreset,wzz_syn);

parameter DSIZE = 8,

ASIZE = 4;

input rclk,rreset;

input [ASIZE:0] wzz;

output [ASIZE:0] wzz_syn;

reg [ASIZE:0] wzz_syn;

reg [ASIZE:0] wzz_syn_1; //两级同步

always @(posedge rclk or negedge rreset)

if (!rreset)

{wzz_syn,wzz_syn_1} <= 0;

else

{wzz_syn,wzz_syn_1} <= {wzz_syn_1,wzz};

endmodule

module testbench;

reg wclk,wreset;

reg rclk,rreset;

reg rena;

reg wena;

wire full;

wire empty;

reg [7:0] wdata;

wire [7:0] rdata;

reg [7:0] value;

yibu_fifo FIFO(wclk,wreset,wdata,wena,rclk,rena,rdata,rreset,full,empty);

// read

task read_word;

begin

@(negedge rclk);

rena = 1;

@(posedge rclk)

#5;

rena = 0;

end

endtask

//write

task write_word;

input [7:0] value;

begin

@(negedge wclk);

wdata = value;

wena = 1;

@(posedge wclk);

#5;

wdata = 8'hzz;

wena = 0;

end

endtask

//write clock

initial begin

wclk = 0;

forever begin

#5 wclk = 1;

#5 wclk = 0;

end

end

//read clock

initial begin

rclk = 0;

forever begin

#10 rclk = 1;

#10 rclk = 0;

end

end

// process

initial

begin

test1;

end

task test1;

begin

wdata = 8'hzz;

wena = 0;

rena = 0;

wreset = 0;

rreset= 0;

#10 wreset = 1;rreset=1;

#50;

//写入10个数据

write_word (8'h01);

write_word (8'h02); //正常

write_word (8'h03);

write_word (8'h04);

write_word (8'h05);

write_word (8'h06);

write_word (8'h07);

write_word (8'h08);

write_word (8'h09);

write_word (8'h0A);

repeat (10)

begin

read_word; // read 10

end

write_word (8'h01);

write_word (8'h02);

write_word (8'h03);

write_word (8'h04);

write_word (8'h05);

write_word (8'h06);

write_word (8'h07);

write_word (8'h08);

write_word (8'h09);

write_word (8'h0A);

write_word (8'h0B);

write_word (8'h0C);

write_word (8'h0D);

write_word (8'h0E);

write_word (8'h0F);

write_word (8'h10);

write_word (8'h11);

write_word (8'h12);

write_word (8'h13); // 写满溢出

repeat (16)

begin

read_word; // 读空

end

end

endtask

endmodule

2013-03-24

2013-03-24

英文文献http://www.sunburst-design.com/papers/

FIFO的设计与仿真的更多相关文章

- 异步fifo的设计

本文首先对异步 FIFO 设计的重点难点进行分析 最后给出详细代码 一.FIFO简单讲解 FIFO的本质是RAM, 先进先出 重要参数:fifo深度(简单来说就是需要存多少个数据) ...

- 异步fifo的设计(FPGA)

本文首先对异步 FIFO 设计的重点难点进行分析 最后给出详细代码 一.FIFO简单讲解 FIFO的本质是RAM, 先进先出 重要参数:fifo深度(简单来说就是需要存多少个数据) ...

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- Fixed-Point Designer(设计、仿真和分析定点系统)

Fixed-Point Designer™ 提供开发定点和单精度算法所需的数据类型和工具,以在嵌入式硬件上进行性能优化.Fixed-Point Designer 会分析您的设计并提供建议的数据类型和属 ...

- 基于TDA4863-2的单级PFC反激LED电源设计与仿真

LED是一个非线性器件,正向电压的微小变化会引起电流的巨大变化:LED是一个半导体二极管,其伏安特性随温度变化而变化(-2mV/℃),假如温度升高,在恒压驱动下LED的电流会增加.长期超过额定电流工作 ...

- 同步FIFO的设计

module scfifo #( , ) ( input clk, input rst_n, input wren, input rden, :] din, :] dout, output full, ...

- Verilog设计异步FIFO

转自http://ninghechuan.com 异步FIFO有两个异步时钟,一个端口写入数据,一个端口读出数据.通常被用于数据的跨时钟域的传输. 同步FIFO的设计.一个时钟控制一个计数器,计数器增 ...

- 基于FPGA的异步FIFO设计

今天要介绍的异步FIFO,可以有不同的读写时钟,即不同的时钟域.由于异步FIFO没有外部地址端口,因此内部采用读写指针并顺序读写,即先写进FIFO的数据先读取(简称先进先出).这里的读写指针是异步的, ...

- FIFO设计思考之一

不管同步FIFO还是异步FIFO,设计难点是full/empty状态flag的正确性. 要保证任何情况 FULL时NO WRITE,EMPTY时NO READ.overflow / underflow ...

随机推荐

- mac同时享受教育优惠和免手续费分期

神奇地址:工商银行 http://store.apple.com/cn_icbc_edu招商银行 http://store.apple.com/cn_cmb_edu农业银行 http://sto ...

- SGU 210 Acdream 1227 Beloved Sons KM

题目链接:点击打开链接 题意: 给定n个人 每一个人的点权 以下n行i行表示第i个人能够获得哪些数(数字从1-n.且不能反复分配) 若这个人获得了数字则你能够获得他的权值. 要你能获得的权值和最大. ...

- android开发游记:ItemTouchHelper 使用RecyclerView打造可拖拽的GridView

以下是RecyclerView结合ItemTouchHelper实现的列表和网格布局的拖拽效果. 效果图例如以下:(gif图有点顿卡,事实上执行是非常流畅的) demo下载地址: DragRecycl ...

- iOS 报错:(子线程中更新UI)This application is modifying the autolayout engine from a background thread after the engine was accessed from the main thread. This can lead to engine corruption and weird crashes.

今天在写程序的时候,使用Xcode 运行工程时报出下面的错误错信息,我还以为是什么呢,好久没遇到过这样的错误了. **ProjectName[1512:778965] This application ...

- [COI2007] [luogu P1823] Patrik 音乐会的等待 解题报告 (单调栈)

题目链接:https://www.luogu.org/problemnew/show/P1823 题目: N个人正在排队进入一个音乐会.人们等得很无聊,于是他们开始转来转去,想在队伍里寻找自己的熟人. ...

- Random words

To choose a random word from the histogram, the simplest algorithm is to build a list with multiple ...

- IHttpHandler的学习(1)

IHttpHandler的那些事 今晚看了一晚上的IHttpHAndler的知识, 在自定义了Httphandler后,在配置webconfig里配置也是个技术活,什么集成模式,什么asp管道什么的: ...

- WLAN STA/AP 并发

WLAN STA/AP 并发 Android 9 引入了可让设备同时在 STA 和 AP 模式下运行的功能.对于支持双频并发 (DBS) 的设备,此功能让一些新功能得以实现,例如在用户想要启用热点 ( ...

- NOIP 2017 逛公园 记忆化搜索 最短路 好题

题目描述: 策策同学特别喜欢逛公园.公园可以看成一张N个点MM条边构成的有向图,且没有 自环和重边.其中1号点是公园的入口,N号点是公园的出口,每条边有一个非负权值, 代表策策经过这条边所要花的时间. ...

- 移动端viewport解惑

我们在做移动端webapp的时候需要设置这么一段: <meta name="viewport" content="width=device-width, initi ...