HDLbits——Rotate100

verilog代码:

// Build a 100-bit left/right rotator, with synchronous load and left/right enable.

//A rotator shifts-in the shifted-out bit from the other end of the register,

// unlike a shifter that discards the shifted-out bit and shifts in a zero. If enabled,

// a rotator rotates the bits around and does not modify/discard them.

// 移出的一位不会丢弃而是补在空缺的位置,即就是题目中的a rotator要求

// load: Loads shift register with data[99:0] instead of rotating.

// ena[1:0]: Chooses whether and which direction to rotate.

// 2'b01 rotates right by one bit

// 2'b10 rotates left by one bit

// 2'b00 and 2'b11 do not rotate.

// q: The contents of the rotator.

module top_module(

input clk,

input load,

input [1:0] ena,

input [99:0] data,

output reg [99:0] q);

always @(posedge clk)

begin

if(load)begin

q <= data;

end

else begin

case(ena)

2'b01: q <= {q[0],q[99:1]};//拼接运算符号{,} ,向右移动1bit

2'b10: q <= {q[98:0],q[99]};//向左边移动1bit

2'b00,2'b11:q <= q; // 保持

default:

q<= q; //所有情况考虑完整的情况下,此处可以省略

endcase

end

end

endmodule

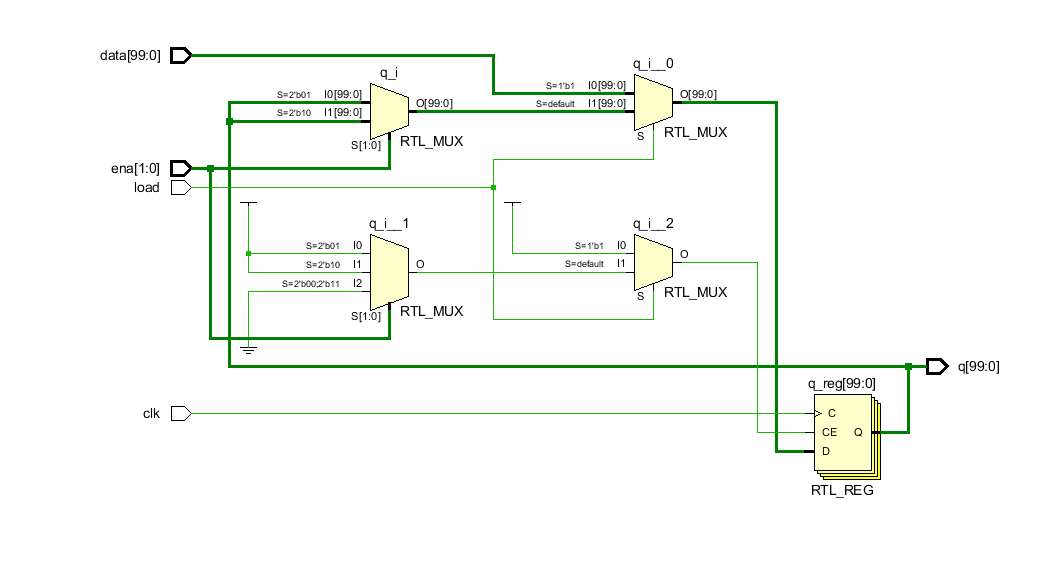

RTL原理图:

HDLbits——Rotate100的更多相关文章

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- HDLBits答案——Circuits

1 Combinational Logic 1.1 Basic Gates 1.1.1 Exams/m2014 q4h module top_module ( input in, output out ...

- HDLBits答案——Verification: Writing Testbenches

1 clock module top_module ( ); reg clk; dut U1(.clk(clk)); initial begin clk = 0; end always begin # ...

- HDLBits答案——Verification: Reading Simulations

1 Finding bugs in code 1.1 Bugs mux2 module top_module ( input sel, input [7:0] a, input [7:0] b, ou ...

- HDLBits答案——Verilog Language

Verilog Language 1 Basics 1.1 Wire module top_module( input in, output out ); assign out = in; endmo ...

- HDLBits答案——Getting started

Getting started 1 Step one module top_module( output one ); // Insert your code here assign one = 1' ...

- verilog常见错误列表

Error/Warning 来源:https://hdlbits.01xz.net/wiki/ 题目: 1.Quartus Warning 10235: Warning (): Verilog HDL ...

- Verilog HDL

https://wenku.baidu.com/view/9943b7acf524ccbff1218463.html https://hdlbits.01xz.net/wiki/Main_Page h ...

- Verilog设计技巧实例及实现

Verilog设计技巧实例及实现 1 引言 最近在刷HDLBits的过程中学习了一些Verilog的设计技巧,在这里予以整理.部分操作可能降低代码的可读性和Debug的难度,请大家根据实际情况进行使用 ...

- 入行数字IC验证的一些建议

0x00 首先,推荐你看两本书,<"胡"说IC菜鸟工程师完美进阶>(pdf版本就行)本书介绍整个流程都有哪些岗位,充分了解IC行业的职业发展方向.<SoC设计方法 ...

随机推荐

- 安装完IDEA后无法打开

安装完IDEA后无法打开 一.现象 安装完IDEA2021.3版本后,无论用什么办法都无法打开 二.原因 原先有安装过idea,里面有加载过一些插件,或者是破解过,会生成一些文件,导致IDEA无法运行 ...

- springboot中实现逆向工程

如果这篇文章能给你带来帮助 不胜荣幸,如果有不同的意见也欢迎批评指正,废话不多说直接上代码.(参考文档:https://www.cnblogs.com/kibana/p/8930248.html) 第 ...

- QT debug/moc_frmalarminfo.o:(.data.rel.ro._ZTV12FrmAlarmInfo[_ZTV12FrmAlarmInfo]+0x1c0): undefined reference to `non-virtual thunk to FrmAlarmInfo::~FrmAlarmInfo()'解决方法

这个报错很具有迷惑性,,,我在网上还看见了ZTI12的报错,但是仔细一看发现是.o文件报错. 简单解释下.o文件(此解释来自百度): o 就是object, 也就相当于windows下编译的obj文件 ...

- 【Linux】ArchLinux 使用之旅

主要参考以下两个链接进行,安装系统和安装桌面环境. 以官方Wiki的方式安装ArchLinux | viseator's blog ArchLinux安装后的必须配置与图形界面安装教程 | visea ...

- <input>输入框,限制输入的为正整数

<input id="eventId" col="EventId" type="text" class="form-cont ...

- 容器 之搭建 jenkins ci 平台

1 部署 gitlab docker run -d \ --name gitlab \ -p 8443:443 \ -p 80:80 \ -p 9998:22 \ -v $PWD/config:/et ...

- linux批量操作(一)

一.常用命令 1.关闭所有java进程命令: ps -ef | grep java | grep -v grep | awk '{print $2}' | xargs kill -9 2.批量文本操作 ...

- clear

BFC虽然可以达到外部背景由内部内容撑开的效果,但是存在副作用 所以由clear将affter受浮动效果解除,来解决以上问题

- 小白之Python-基础中的基础01

Python-基础中的基础01 第一次写博客笔记,尝试并监督下自己. 每一天都值得期待! 20170803 -----------------华丽的分界线------------- Python之-- ...

- MTK平台总结

1. 通过cmdline参数不对printk打印速率进行限制:mt_boot.c kcmdline_append(" ignore_loglevel=1 printk.devkmsg=on ...