HDLbits——Rotate100

verilog代码:

// Build a 100-bit left/right rotator, with synchronous load and left/right enable.

//A rotator shifts-in the shifted-out bit from the other end of the register,

// unlike a shifter that discards the shifted-out bit and shifts in a zero. If enabled,

// a rotator rotates the bits around and does not modify/discard them.

// 移出的一位不会丢弃而是补在空缺的位置,即就是题目中的a rotator要求

// load: Loads shift register with data[99:0] instead of rotating.

// ena[1:0]: Chooses whether and which direction to rotate.

// 2'b01 rotates right by one bit

// 2'b10 rotates left by one bit

// 2'b00 and 2'b11 do not rotate.

// q: The contents of the rotator.

module top_module(

input clk,

input load,

input [1:0] ena,

input [99:0] data,

output reg [99:0] q);

always @(posedge clk)

begin

if(load)begin

q <= data;

end

else begin

case(ena)

2'b01: q <= {q[0],q[99:1]};//拼接运算符号{,} ,向右移动1bit

2'b10: q <= {q[98:0],q[99]};//向左边移动1bit

2'b00,2'b11:q <= q; // 保持

default:

q<= q; //所有情况考虑完整的情况下,此处可以省略

endcase

end

end

endmodule

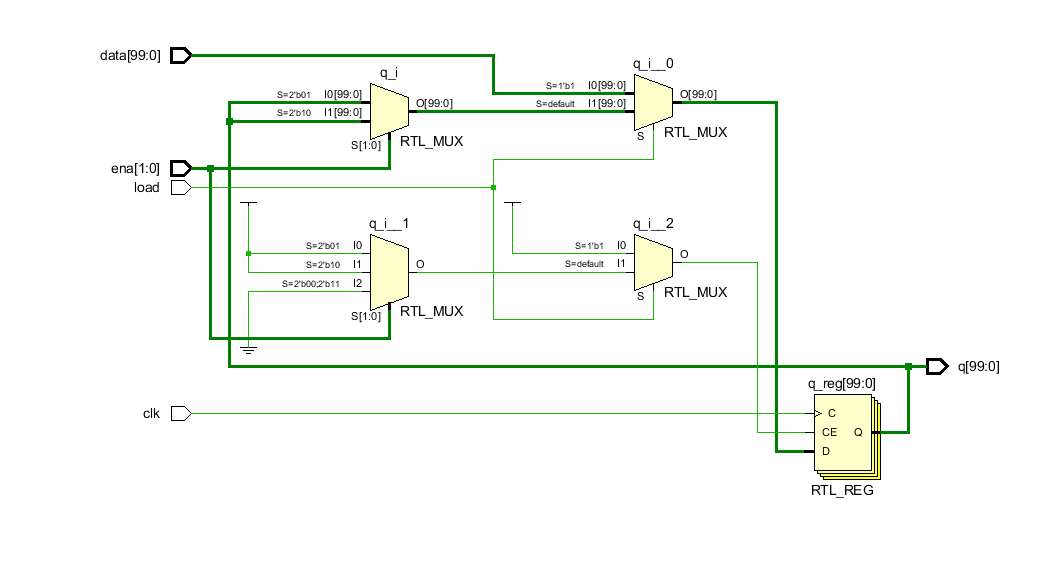

RTL原理图:

HDLbits——Rotate100的更多相关文章

- 学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进 ...

- HDLBits答案——Circuits

1 Combinational Logic 1.1 Basic Gates 1.1.1 Exams/m2014 q4h module top_module ( input in, output out ...

- HDLBits答案——Verification: Writing Testbenches

1 clock module top_module ( ); reg clk; dut U1(.clk(clk)); initial begin clk = 0; end always begin # ...

- HDLBits答案——Verification: Reading Simulations

1 Finding bugs in code 1.1 Bugs mux2 module top_module ( input sel, input [7:0] a, input [7:0] b, ou ...

- HDLBits答案——Verilog Language

Verilog Language 1 Basics 1.1 Wire module top_module( input in, output out ); assign out = in; endmo ...

- HDLBits答案——Getting started

Getting started 1 Step one module top_module( output one ); // Insert your code here assign one = 1' ...

- verilog常见错误列表

Error/Warning 来源:https://hdlbits.01xz.net/wiki/ 题目: 1.Quartus Warning 10235: Warning (): Verilog HDL ...

- Verilog HDL

https://wenku.baidu.com/view/9943b7acf524ccbff1218463.html https://hdlbits.01xz.net/wiki/Main_Page h ...

- Verilog设计技巧实例及实现

Verilog设计技巧实例及实现 1 引言 最近在刷HDLBits的过程中学习了一些Verilog的设计技巧,在这里予以整理.部分操作可能降低代码的可读性和Debug的难度,请大家根据实际情况进行使用 ...

- 入行数字IC验证的一些建议

0x00 首先,推荐你看两本书,<"胡"说IC菜鸟工程师完美进阶>(pdf版本就行)本书介绍整个流程都有哪些岗位,充分了解IC行业的职业发展方向.<SoC设计方法 ...

随机推荐

- Python-网络编程和多进程多线程开发

网络编程 osi7层模型 以通过访问网站发送请求数据为例,每一层会做如下的事情 应用层:规定数据的格式. "GET /s?wd=你好 HTTP/1.1\r\nHost:www.baidu.c ...

- reset slave

reset slave 所有中继日志文件都被删除,即使它们还没有被复制 SQL 线程完全执行. reset slave all 所有中继日志文件都被删除,它会清除连接参数(需要重新change mas ...

- vue 学习 css第四天

一.css背景属性 可以给页面元素添加背景样式. 背景属性(background)可以设置. 1.背景颜色. 2.背景图片. 3.背景平铺. 4.背景图片位置 5.背景图像固定 1.背景颜色(back ...

- consul剔除某个服务

curl --request PUT http://ip:端口/v1/agent/service/deregister/服务对应的id地址

- Kubernetes 设置master相关

设置master调度命令 1.设置master一般情况下不接受pod调度 sudo kubectl taint nodes master node-role.kubernetes.io/master= ...

- flink学习总结

flink学习总结 1.Flink是什么? Apache Flink 是一个框架和分布式处理引擎,用于处理无界和有界数据流的状态计算. 2.为什么选择Flink? 1.流数据更加真实的反映了我们的生活 ...

- Ubuntu 添加新用户并制定目录和shell

Ubuntu 添加新用户并制定目录和shell 分类: LINUX 2011-07-07 15:22:54 ubuntu新建的用户并没有新建相应的home目录和对应的shell环境. 下面就总结 ...

- js-防抖(简易版)

/** * 节流函数 */ var count = 1; var container = document.getElementById('container'); function getUse ...

- java实现读取json文件指定字段值

使用场景 现有一个大数据的json文件,每条数据有多层数据信息.现在想把其中某个字段提取并叠加计算. json文件格式 1 { 2 "MsgID":"111", ...

- GridView.RowCellClick Event

Fires when a user clicks a data cell. If data is editable and the ColumnViewOptionsBehavior.EditorSh ...