适用于带fifo接口的存储器和显示器测试模块封装 挑战cb

cb说完美是没有极限的,对此我表示赞同,自从用了cb的板子,玩开cmos,fpga,sdram,vga等。

不断涌现的是,双端口sdram,四端口sdram,各式各样的封装,但是大同小异,但总是有些不同,对于初学的我,感觉还是挺费事,玩转各种例程发现,cb的sdram驱动程序很强大但并不完美,其中对sdram有挑选作用,如hy57v641620ftp-7很ok的使用,换成hy57v641620ftp-6就有问题,但是使用其他版本程序测试,这两个ic均ok。

这个问题一度困扰过cb良久,最终cb偶然发现,将突发长度从256改为128,就能好好的解决,自此,解决了问题(详情参阅cb博客)

但是这样可能并不完美,需要深究其根本,就得仔细阅读内部代码,仔细推敲,本人水平有限,所以只能一步一个脚印。

现将兼容和不兼容的程序统一接口,使得程序更好移植,逻辑更加清晰。

ps:cb的接口已经做得很棒,只是我不太习惯,以下移植接口,按照我的思维理解方式修改。

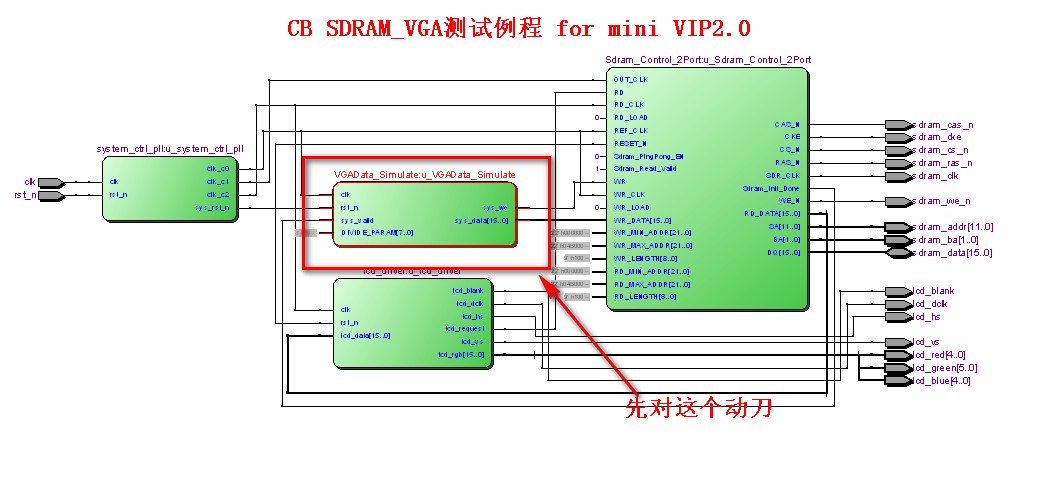

先看看cb现有的接口

改造中

1、

module LCDData_Simulate

(

input clk, //globan clock

input rst_n, //Global reset

input sys_vaild, //the device is ready

input[7:0] DIVIDE_PARAM, //0-255

input[11:0] X_size, // 增加x尺寸大小输入,

input[11:0] Y_size, // 增加y尺寸大小输入,

//sys 2 sdram control

output disp_valid, // 增加显示有效信号输出,告知设备,目前输出像素有效,类似显示的帧同步信号

output reg [15:0] sys_data,

output sys_we

);

2、SDRAM_VGA_Display_Test

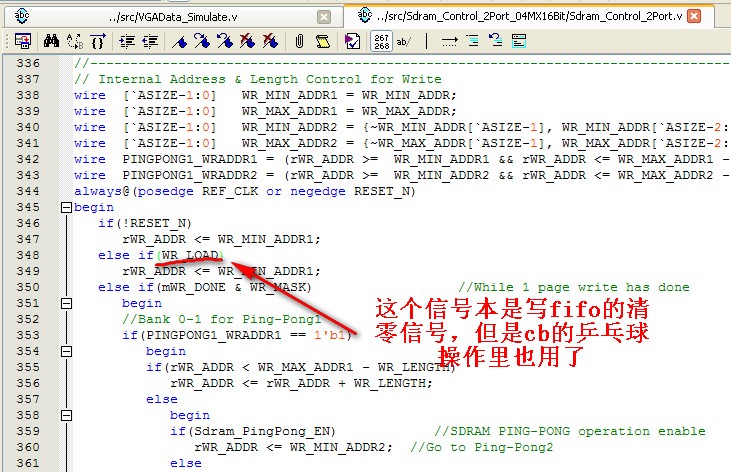

增加 WR_LOAD信号,根据数据产生模块的帧有效的信号,产生一个脉冲,高电平脉冲,在帧同步信号结束时产生,用于清除fifo

wire WR_LOAD;

reg sys_disp_valid_r1;

reg sys_disp_valid_r2;

always@(posedge clk_ref)

begin

sys_disp_valid_r1<=sys_disp_valid;

sys_disp_valid_r2<=sys_disp_valid_r1;

end

assign WR_LOAD=sys_disp_valid_r1&(!sys_disp_valid_r1);

3、SDRAM_VGA_Display_Test

// FIFO Write Side

.WR_CLK (clk_write), //write fifo clock

.WR_LOAD (WR_LOAD), //使用此信号

.WR_DATA (sys_data_in), //write data input

.WR (sys_we_in), //write data request

.WR_MIN_ADDR (22'd0), //write start address

.WR_MAX_ADDR (`H_DISP * `V_DISP *22'd1), //write max address

.WR_LENGTH (9'd256), //write burst length

就此,第一步兼容已经完成,此目的已经达到数据产生模块任意间隔产生数据,保证同步,下一再实现显示器尺寸自动匹配功能。

适用于带fifo接口的存储器和显示器测试模块封装 挑战cb的更多相关文章

- 基于Verilog的带FIFO写入缓冲的串口发送接口封装

一.模块框图及基本思路 tx_module:串口发送的核心模块,详细介绍请参照前面的“基于Verilog的串口发送实验” fifo2tx_module:当fifo不为空时,读取fifo中的数据并使能发 ...

- 关于Xilinx AXI Lite 源代码分析---自建带AXI接口的IP

关于Xilinx AXI Lite 源代码分析---自建带AXI接口的IP 首先需要注意此处寄存器数量的配置,它决定了slv_reg的个数. 读写数据,即是对寄存器slv_reg进行操作: 关于AXI ...

- 【关注图像采集视频传输】之 Cy3014 usb3.0 FIFO接口

CYUSB3014延续了CY7C68013A最吸引人的地方,那就是实现高速数据传输的Slave FIFO接口,应用这种模式,据说数据传输率可以达到320MB/s. 同USB2.0的芯片CY7C6801 ...

- 330-支持PXIE带FMC接口的Xilinx FPGA XC7K325T PCIeX8 接口卡平台

支持PXIE带FMC接口的Xilinx FPGA XC7K325T PCIeX8 接口卡平台 一.板卡概述 本板卡基于Xilinx公司的FPGAXC7K325T-2FFG900 芯片,pin_ ...

- python接口自动化(三十五)-封装与调用--流程类接口关联(详解)

简介 流程相关的接口,主要用 session 关联,如果写成函数(如上篇),s 参数每个函数都要带,每个函数多个参数,这时候封装成类会更方便.在这里我们还是以博客园为例,带着小伙伴们实践一下. 接口封 ...

- Asp.net 面向接口可扩展框架之数据处理模块及EntityFramework扩展和Dapper扩展(含干货)

接口数据处理模块是什么意思呢?实际上很简单,就是使用面向接口的思想和方式来做数据处理. 还提到EntityFramework和Dapper,EntityFramework和Dapper是.net环境下 ...

- MBIST:用于嵌入式存储器的可测试设计技术

MBist技术可以自动实现存储器单元或阵列的RTL级内建自测试电路,MBIST的EDA工具支持多种测试算法的自动实现,可针对一个或多个内嵌存储器自动创建BIST逻辑,并完成BIST逻辑与存储器的连接, ...

- (转)用mysql自带工具mysqlslap对数据库进行压力测试

http://aolens.blog.51cto.com/7021142/1901557-------用mysql自带工具mysqlslap对数据库进行压力测试 mysqlslap是mysql自带的工 ...

- 268-基于FMC接口的DSP TMS320C6657子卡模块

基于FMC接口的DSP TMS320C6657子卡模块 一. 概述 FMC连接器是一种高速多pin的互连器件,广泛应用于板卡对接的设备中,特别是在xilinx公司的所有开发板中都使用. ...

随机推荐

- Django 基本使用

Django 基本使用 Django 安装 pip install django Django 创建项目 django-admin startproject 项目名称 Django 创建应用 pyth ...

- nyoj 35-表达式求值(stack, 栈的应用)

35-表达式求值 内存限制:64MB 时间限制:3000ms Special Judge: No accepted:37 submit:53 题目描述: ACM队的mdd想做一个计算器,但是,他要做的 ...

- shuf

shi一个排序器,一般用来试用随机输入产生随机乱序的输出,他可以作用于输入文件或者数值范围,也可以对数组进行操作. -i -nN -e 1.掷骰子shuf -i 1-6 -n1 shuf -i 1-6 ...

- 记录工作遇到的死锁问题(Lock wait timeout exceeded; try restarting transaction)

1.问题背景 刚来新公司不久,对业务还不太熟悉,所以领导先安排我维护原有系统.大概介绍下项目背景,项目分为核心业务部分在项目A中,与第三方交互的业务在项目B中,前端发起请求调用A项目接口,并在A项目中 ...

- Win32 COM组件 x Android Service (二)

继续上一篇. 如果不使用AIDL(Android Interface Definition Language接口描述语言)编写服务接口的话,(COM组件,CORBA组件,ICE组件以及其它远程调用框架 ...

- mysql的属性zerofill

一.字段中zerofill属性的类似定义方式 SQL语句:字段名 int(M) zerofill 二.zerofill属性的作用 1.插入数据时,当该字段的值的长度小于定义的长度时,会在该值的前面补上 ...

- 小白学 Python 爬虫(4):前置准备(三)Docker基础入门

人生苦短,我用 Python 前文传送门: 小白学 Python 爬虫(1):开篇 小白学 Python 爬虫(2):前置准备(一)基本类库的安装 小白学 Python 爬虫(3):前置准备(二)Li ...

- web前端面试题总结(html、css)

1.对 WEB 标准以及 W3C 的理解与认识? 参考: 标签闭合.标签小写.不乱嵌套.提高搜索机器人搜索几率.使用外 链 css 和 js 脚本. 结构行为表现的分离.文件下载与页面速度更快.内容能 ...

- java的回调和C#的委托

曾经有人对我说java的回调很巧妙. 今天我自己看了一下,回调的关键就是一个接口的事情. 也许是因为用了一定的手法,一开始不好懂吧,所以看懂了会感觉巧妙. 但是我心里的想法却是,真啰嗦! 回调的实例 ...

- 最全 HTTP 安全响应头设置指南

销售“安全记分卡”的公司正在崛起,并已开始成为企业销售的一个因素.这些公司组合使用 HTTP 安全报头和 IP 信誉来进行评级.不过,在很大程度上,公司的得分取决于对外开放网站上设置的安全响应报头.本 ...