xilinx 高速收发器Serdes深入研究-Comma码(转)

一、为什么要用Serdes

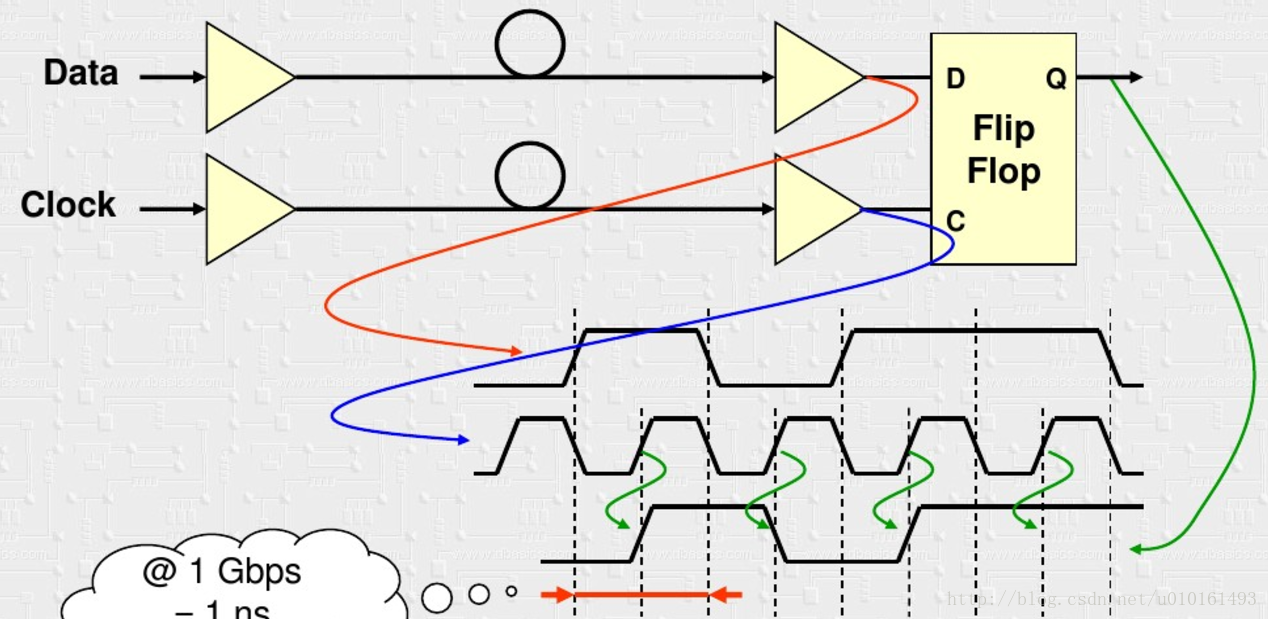

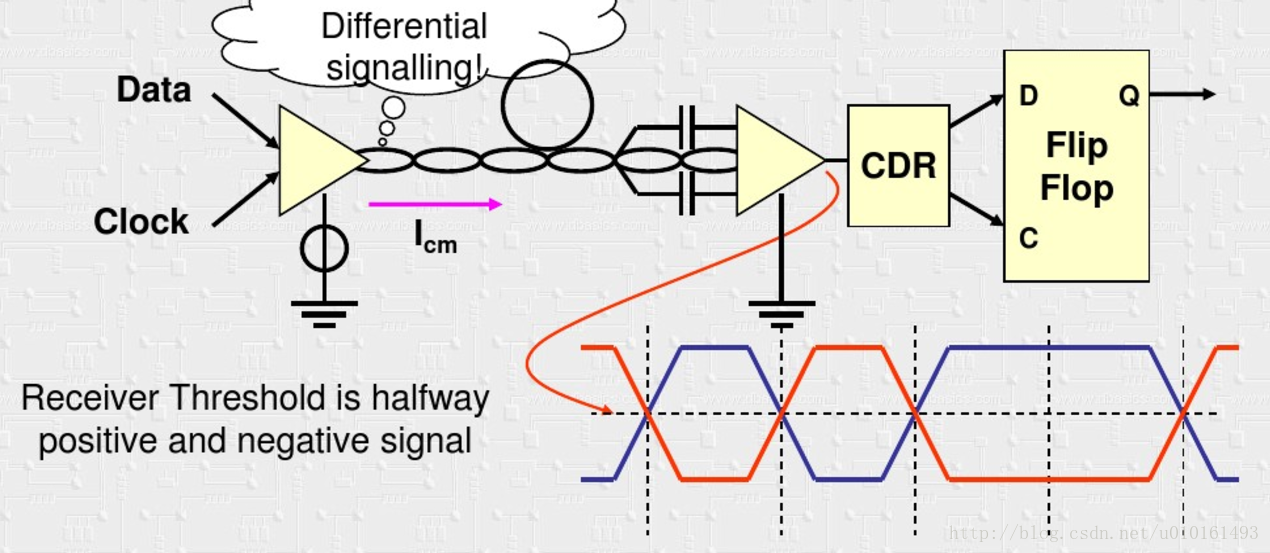

传统的源同步传输,时钟和数据分离。在速率比较低时(<1000M),没有问题。

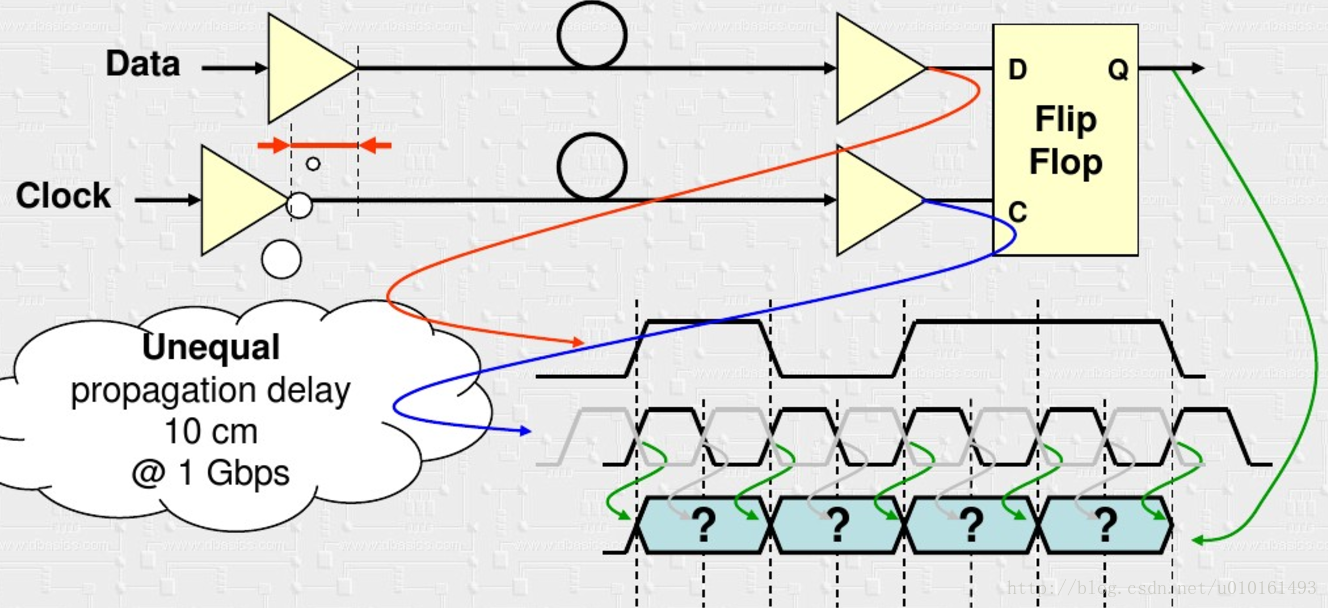

在速率越来越高时,这样会有问题

由于传输线的时延不一致和抖动存在,接收端不能正确的采样数据,对不准眼图中点。

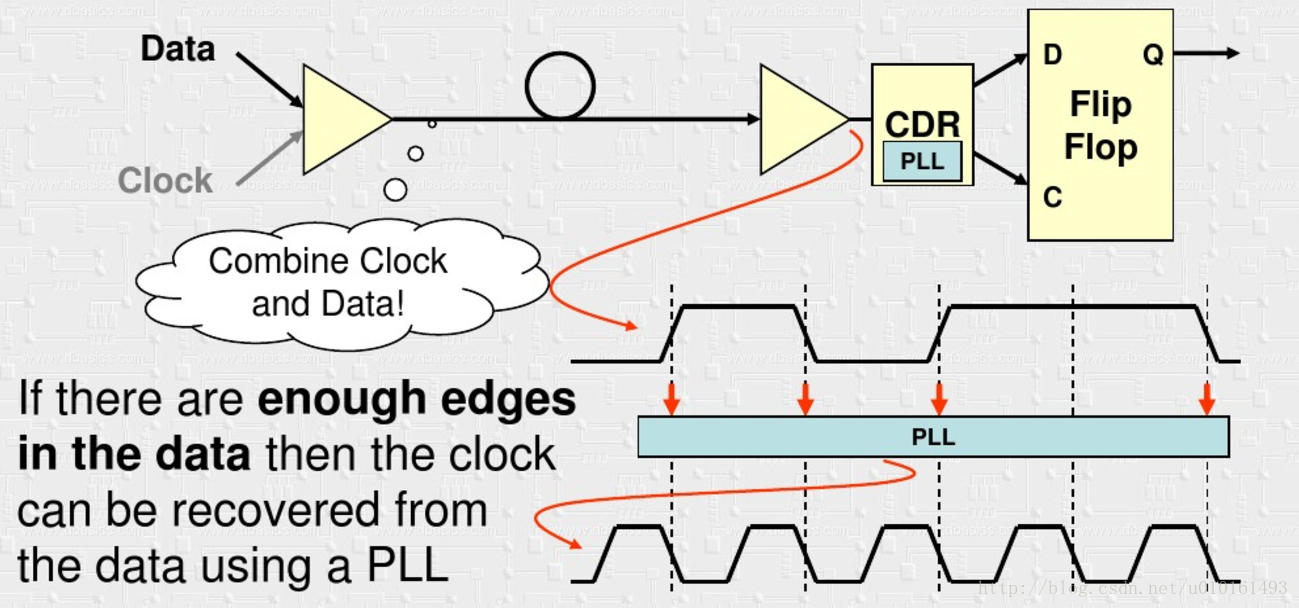

然后就想到了从数据里面恢复出时钟去采样数据,即CDR

这样就不存在延迟不一致的情况,有轻微的抖动也不会影响采样(恢复的时钟会随着数据一起抖动)。

二 、为什么要用8b10b,64b66b?

1 提供足够的跳变来恢复时钟

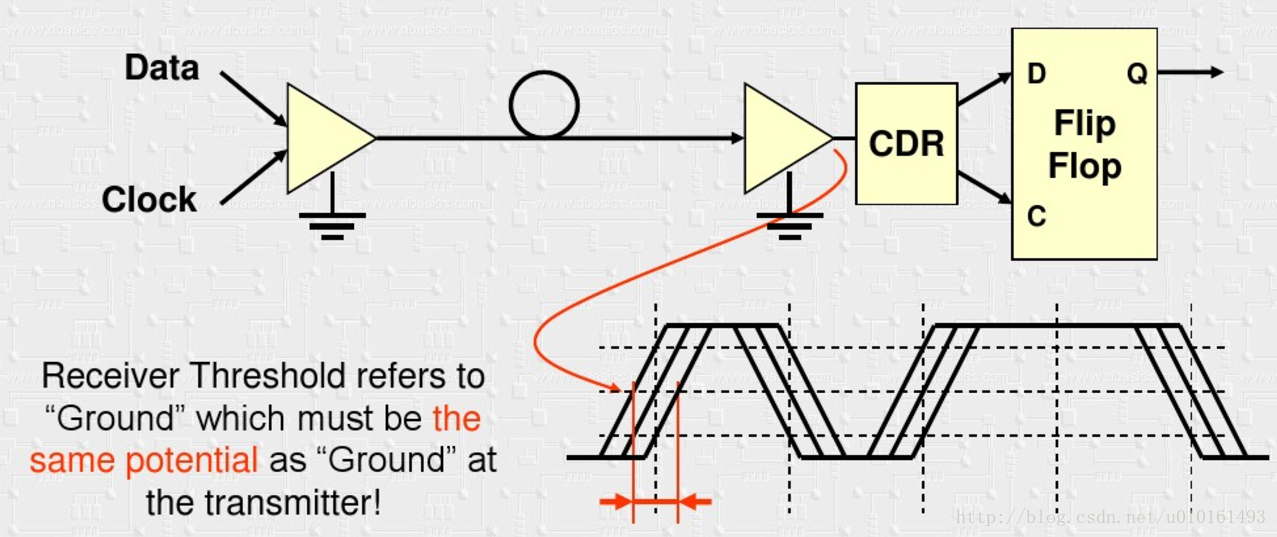

这样还有问题,收发两端必须共地,但往往很难实现。

于是采样差分信号传输,为了防止共模电压在接收端导致电流过大,使用电流驱动模式。看到接收端有电容进行交流耦合,隔直流。这样又带来一个问题,需要DC平衡。所以有了下面另一个原因。

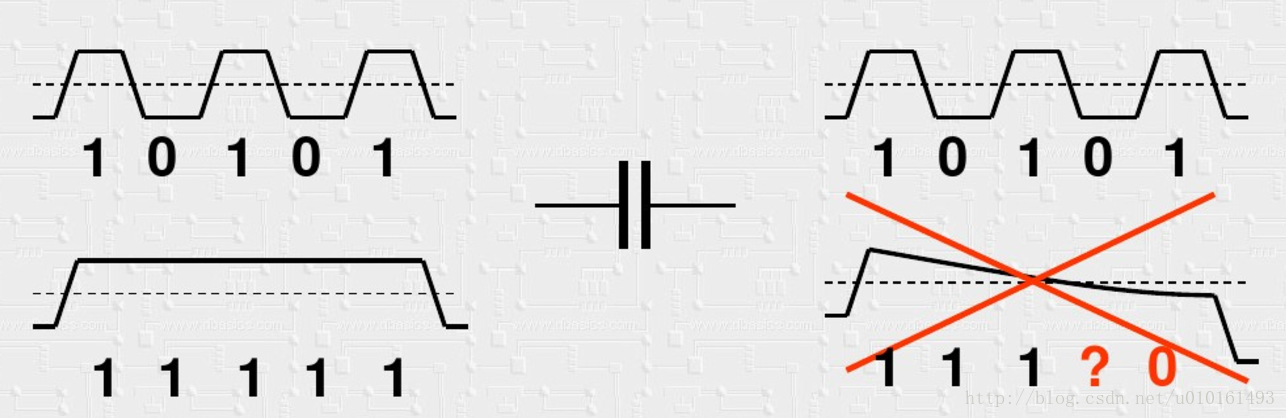

2 DC平衡,即0和1的数量要相等。

3 run length,0和1连续出现的最大长度

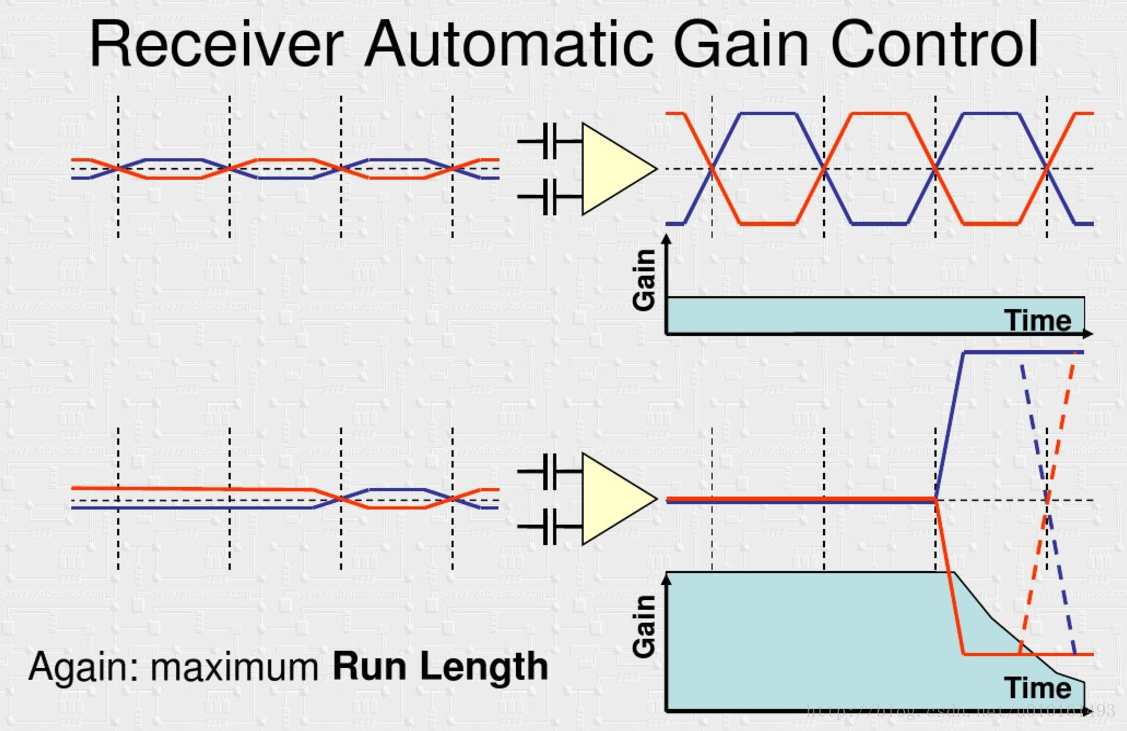

AGC自动增益控制需要交流分量才能实现放大

4 comma码,K码

在serdes上面的高速串行流在接收端需要重新串并转化成多字并行,怎么找到字的边界进行对齐呢?

这就需要一个特殊的序列,这就是comma码。

传输过程中需要的一些控制,最好不要和数据冲突了,这就是K码。

基于以上四个原因,就有了8b10b,64b66b的出现。

三 、8b10b编码

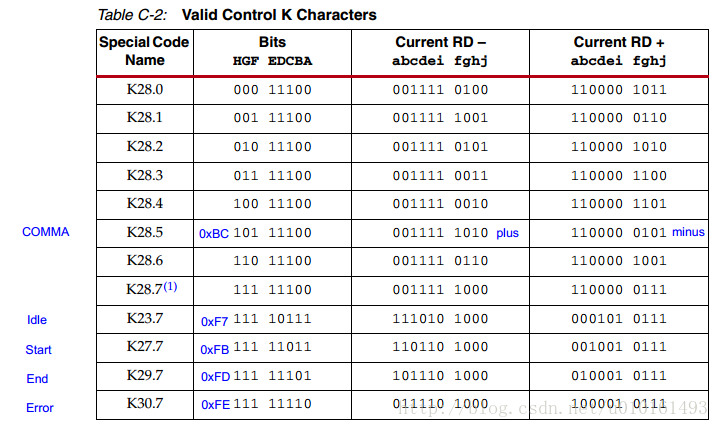

8b10b编码一句话概括起来就是把8bit的数据变成10bit的数据,其中所有1或0的个数不会超过6个,并且连续的1或0的个数不会超过4个。这样原本1024的汉明空间编码后就大大减小了。其中有256个data码和12K码控制码。这样数据和控制码不会重合。

其中K28.1,K28.5,K28.7可以作为分隔码,也叫comma码,用于接收端在串行的数据流中找到字节边界。常用的K28.5即0xBC。因为正常传输的数据也可能有0xBC,怎么区分呢?是有一根单独的控制线,tx_is_K在传输K码时拉高,在传数据时拉低,去控制8b10b的编码模块到底是编码成数据还是控制K码。

四、Xilinx Serdes的几个细节

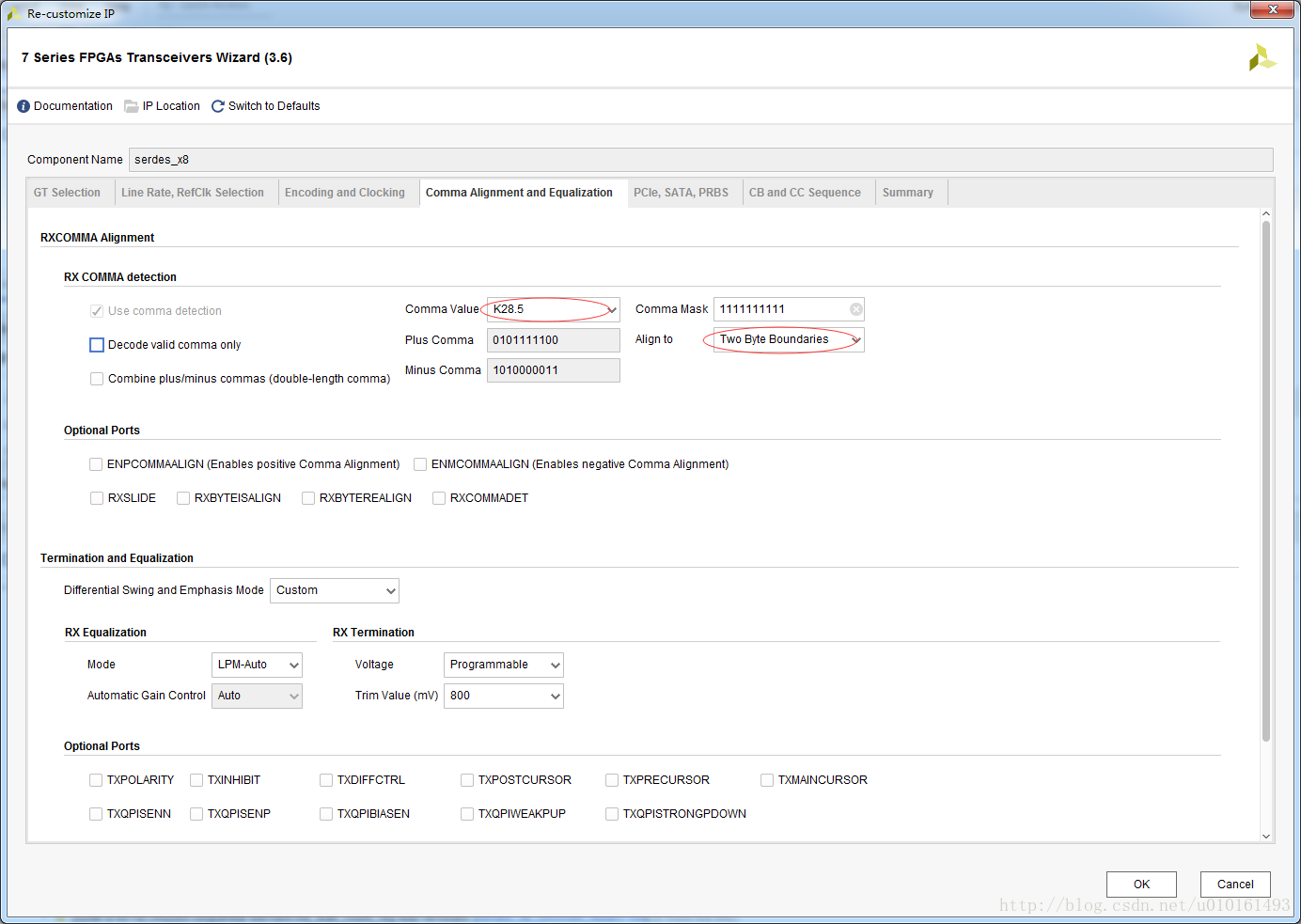

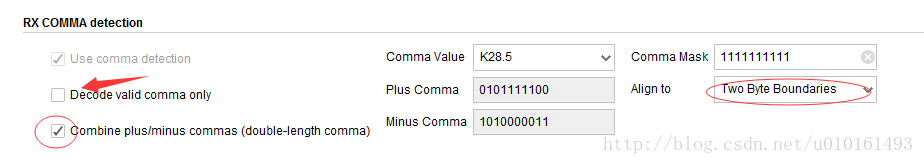

1.COMMA码使用

K28.5,0xBC,+0101_111100,-1010_000011; 为检测字节分割。

使用其它K码,作为帧开始,帧结束,时钟修正和数据对齐。

2.多字节处理

在数据率比较高的时候,外部位宽可能是2字(16位)或者4字(32位)。这是如果收发双方不约定好在高低哪个字发送comma码,这时是可以检测字边界,但接收端就会出现高低字节翻转的情况。在任意对于单COMMA的数据对齐,选择偶数字节对齐。发送的时候 0x5ABC->2’b01。

也可以选择发送组合的comma码,就是把NP的comma拼接起来发送,这样接收端就检测16bit的双字边界。也可以避免上面的情况出现。发送的时候0xBCBC->2’b11

注意:decode valid comma only不要选,因为还可能发送其他的K码用于控制。反正8b10b是用的收发器硬核的资源,不用白不用。

3、环回设置:

1.“000”:正常模式

2.“001”:近端PCS环回

3.“010”:近端PMA环回

4.“100”:远端PMA环回

5.“110”:远端PCS环回

注意Xilinx例化的example的文件中配置的环回是预留环回接口的意思,仍然需要另外手动配置。

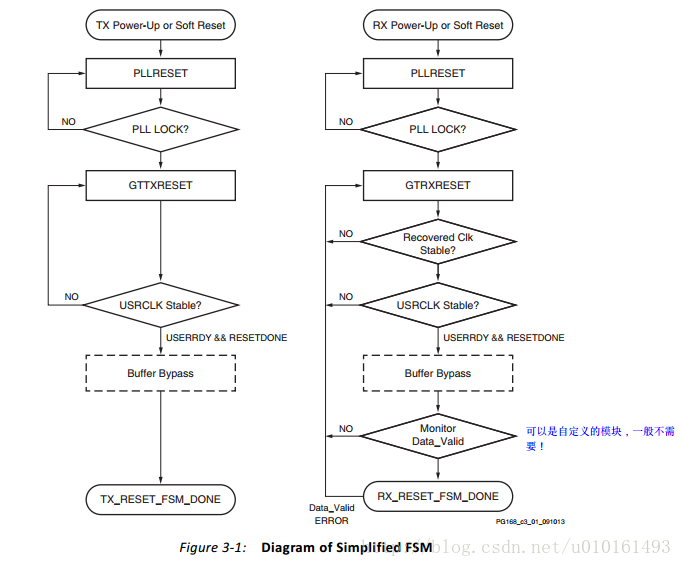

4、fsm_down状态机

在Monitor Data_Valid模块,是用的frame_check的正确的信号,校验失败会导致复位GTrxreset。可以不用这个反馈,直接置1。需要手动改一下。

5.通道绑定

限于篇幅,单独列出

6.时钟纠正

限于篇幅,单独列出

xilinx 高速收发器Serdes深入研究-Comma码(转)的更多相关文章

- 【转载】xilinx 高速收发器Serdes深入研究

此篇文章深入浅出介绍了关于高速串行收发器的几个重要概念和注意事项,为方便知识点复习总结和后续查阅特此转载,原文标题及链接为:xilinx 高速收发器Serdes深入研究 - CSDN博客 http ...

- Xilinx-7Series-FPGA高速收发器使用学习—TX发送端介绍

每一个收发器拥有一个独立的发送端,发送端有PMA(Physical Media Attachment,物理媒介适配层)和PCS(PhysicalCoding Sublayer,物理编码子层)组成,其中 ...

- Xilinx-7Series-FPGA高速收发器使用学习—概述与参考时钟篇

xilinx的7系列FPGA根据不同的器件类型,集成了GTP.GTX.GTH以及GTZ四种串行高速收发器,四种收发器主要区别是支持的线速率不同,图一可以说明在7系列里面器件类型和支持的收发器类型以及最 ...

- 7系列高速收发器总结 GTP IP核使用篇

上一篇7系列收发器博文讲解了GTP IP核的基本配置,本文继续分析如何将它使用起来.生成IP核后打开example design,先看看工程中包含的文件结构. 顶层文件下包含了gtp ip核系统顶层文 ...

- 【文献04】无人驾驶高速AWID-AWIS车辆运动控制研究

参考:阮久宏, 李贻斌, 荣学文, et al. 无人驾驶高速AWID-AWIS车辆运动控制研究[J]. 农业机械学报, 2009, 40(12):37-42. https://drive.wps.c ...

- IOS开发--待研究源码(持续添加更新)

1.丰富的CAEmitterLayer制作的粒子效果,比如烟花效果 (还未研究) 该项目本人未研究,待以后有时间或者有需求再研究 github源码下载地址:https://github.com/lic ...

- Xilinx-7Series-FPGA高速收发器使用学习—RX接收端介绍

上一篇博文介绍了GTX的发送端,这一篇将介绍GTX的RX接收端,GTX RX接收端的结构和TX发送端类似,数据流方向相反,不过和发送端也有一些区别,GTX的RX接收端结构图如图1所示: 图1 下面将根 ...

- Lattice系列FPGA入门相关0(Lattice与Altera、Xilinx对比及入门)

需求说明:Lattice系统FPGA入门 内容 :Lattice与Altera.Xilinx对比 来自 :时间的诗 1.Lattice与Altera.Xilinx对比 latt ...

- Xilinx FPGA高速串行收发器简介

1 Overview 与传统的并行实现方法相比,基于串行I/O的设计具有很多优势,包括:器件引脚数较少.降低了板空间要求.印刷电路板(PCB)层数较少.可以轻松实现PCB设计.连接器较小.电磁干扰降低 ...

随机推荐

- centos 下卸载mysql

查看当前已安装服务 [root@localhost]# rpm -qa|grep -i mysqlMySQL-server-5.6.36-1.rhel5.x86_64qt-mysql-4.8.5-13 ...

- 利用Anaconda完美解决Python 2与python 3的共存问题

前言 现在Python3 被越来越多的开发者所接受,同时让人尴尬的是很多遗留的老系统依旧运行在 Python2 的环境中,因此有时你不得不同时在两个版本中进行开发,调试. 如何在系统中同时共存 Pyt ...

- LeetCode--255--用队列实现栈(java版)

使用队列实现栈的下列操作: push(x) -- 元素 x 入栈 pop() -- 移除栈顶元素 top() -- 获取栈顶元素 empty() -- 返回栈是否为空 注意: 你只能使用队列的基本操作 ...

- 20170906xlVBA_GetEMailFromDocument

Public Sub GetDataFromWord() AppSettings 'On Error GoTo ErrHandler Dim StartTime, UsedTime As Varian ...

- android主流开源库

网络框架:Volley 和 Async Volley特点:能使网络通信更快,更简单.更健壮 Get,Post网络请求及网络图像的高效率 Async:高效的网络数据请求, 解析成json 持久化cook ...

- ImportError: sys.meta_path is None, Python is likely shutting down

python执行过错中,报错:ImportError: sys.meta_path is None, Python is likely shutting down 解决方法:在C:\Users\Adm ...

- 『计算机视觉』Mask-RCNN_推断网络其三:RPN锚框处理和Proposal生成

一.RPN锚框信息生成 上文的最后,我们生成了用于计算锚框信息的特征(源代码在inference模式中不进行锚框生成,而是外部生成好feed进网络,training模式下在向前传播时直接生成锚框,不过 ...

- 部署项目到linux中报Spring MVC报异常:org.springframework.web.util.NestedServletException: Request processing failed

@RequestMapping(value = "/security/login", method = RequestMethod.POST) public ModelAndVie ...

- python3使用requests模块完成get/post/代理/自定义header/自定义Cookie

一.背景说明 http请求的难易对一门语言来说是很重要的而且是越来越重要,但对于python一是urllib一些写法不太符合人的思维习惯文档也相当难看,二是在python2.x和python3.x中写 ...

- php常见问题-foreach和引用造成的问题。

结论: foreach($arr as &$v) 类似这样的引用循环, 脚本语言需要注意,再次使用 $v时,他还指向原来的引用.会产生问题. unset($v)可以解除引用. 所以循环引用过 ...